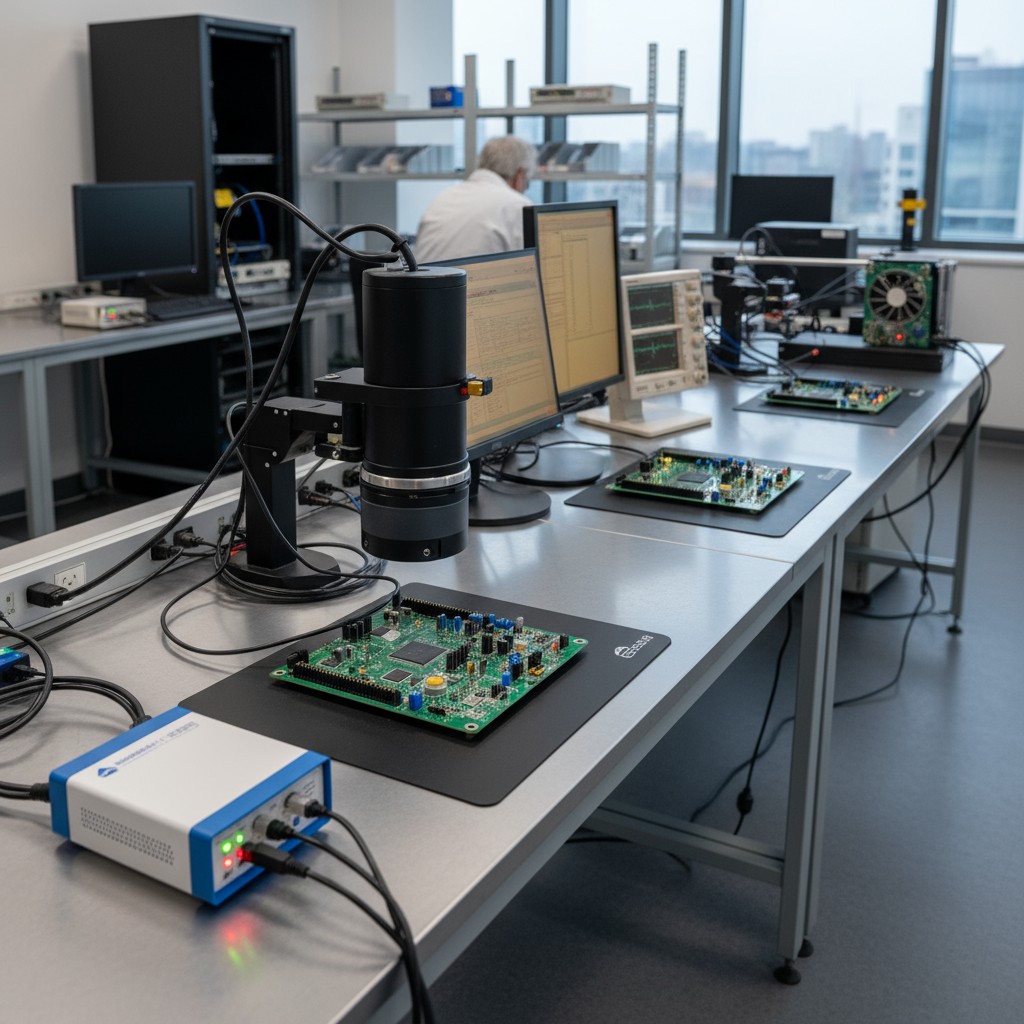

La presión por detectar fallos de fabricación antes de que las placas sean enviadas no es negociable. Un fallo escapado en un sistema crítico puede costar exponencialmente más que las pruebas que lo habrían detectado. Esta realidad empuja a muchos equipos de ingeniería hacia las pruebas en circuito (ICT) como el método predeterminado, considerado durante mucho tiempo el estándar de oro para la cobertura. La ICT completa ofrece acceso integral a casi cada nodo en una placa, prometiendo tasas de detección de fallas que se acercan al máximo teórico. Para la producción en volumen alto, la inversión tiene sentido; los costos fijos de ingeniería del fixture y equipo de prueba se amortizan en miles de unidades, reduciendo la carga por unidad a niveles insignificantes.

Pero la economía cambia cuando los volúmenes de producción disminuyen. Para lotes inferiores a unos pocos cientos de unidades, las propias fortalezas de la ICT se convierten en cargas. El fixture personalizado requerido para cada diseño de placa tiene un costo de ingeniería alto y fijo que no escala. Los tiempos de entrega se extienden mientras se diseñan, construyen y depuran los fixtures. Las iteraciones de diseño, comunes en la introducción de nuevos productos, invalidan los fixtures por completo, obligando a reiniciar el ciclo. En Bester PCBA, hemos visto esto en cientos de proyectos. Para lotes inferiores a 200 o 300 unidades, la ICT completa rara vez justifica su inversión.

La alternativa no es abandonar las pruebas rigurosas, sino reemplazar el modelo dependiente del fixture por una estrategia más ágil y rápida basada en escaneo de frontera, pruebas sin vectores y pruebas funcionales focalizadas. Esta combinación ofrece una cobertura de fallas comparable, elimina el cuello de botella del fixture y proporciona un ciclo de depuración más rápido cuando se detectan fallas. Este cambio no es ideológico; es una respuesta práctica a la fricción matemática y mecánica que la ICT impone a una producción ágil de bajo volumen.

La Asunción ICT y Dónde Se Rompe

Las pruebas en circuito se convirtieron en el estándar de la industria en una era de diseños de alto volumen y estables. El modelo era simple: invertir mucho inicialmente en un fixture de prueba personalizado y en un probador sofisticado, y luego aprovechar esa inversión en decenas de miles de unidades idénticas. Con tiempos de prueba por unidad medidos en segundos, el costo marginal por placa era efectivamente cero después de absorber los costos fijos. Para un fabricante de electrónica de consumo que produce 50,000 unidades del mismo SKU, las matemáticas eran irrefutables.

Ese modelo de producción se ha fracturado. La fabricación moderna de electrónica sirve cada vez más a mercados con alta variedad y bajo volumen. Los ciclos de vida del producto son más cortos, las iteraciones de diseño son más frecuentes y la personalización es una ventaja competitiva. Una empresa podría producir 150 unidades de una variante, iterar el diseño, y luego producir 200 de la siguiente. La suposición de que un solo fixture probará miles de placas idénticas ya no se sostiene. Los costos fijos que eran insignificantes en volúmenes altos se vuelven castigadores cuando se distribuyen en unos pocos cientos de unidades.

El modelo se rompe donde el costo total de la infraestructura ICT supera el costo ajustado por riesgo de las estrategias alternativas. Ese umbral no es arbitrario. Es una función del costo del fixture, el tiempo de ingeniería, el tiempo de entrega de producción y la cobertura alcanzable a través de métodos sin fixture. Para la mayoría de los diseños de placas, ese umbral se sitúa entre 200 y 300 unidades.

La Trampa del Costo Fijo de las Pruebas en Circuito Cerrado

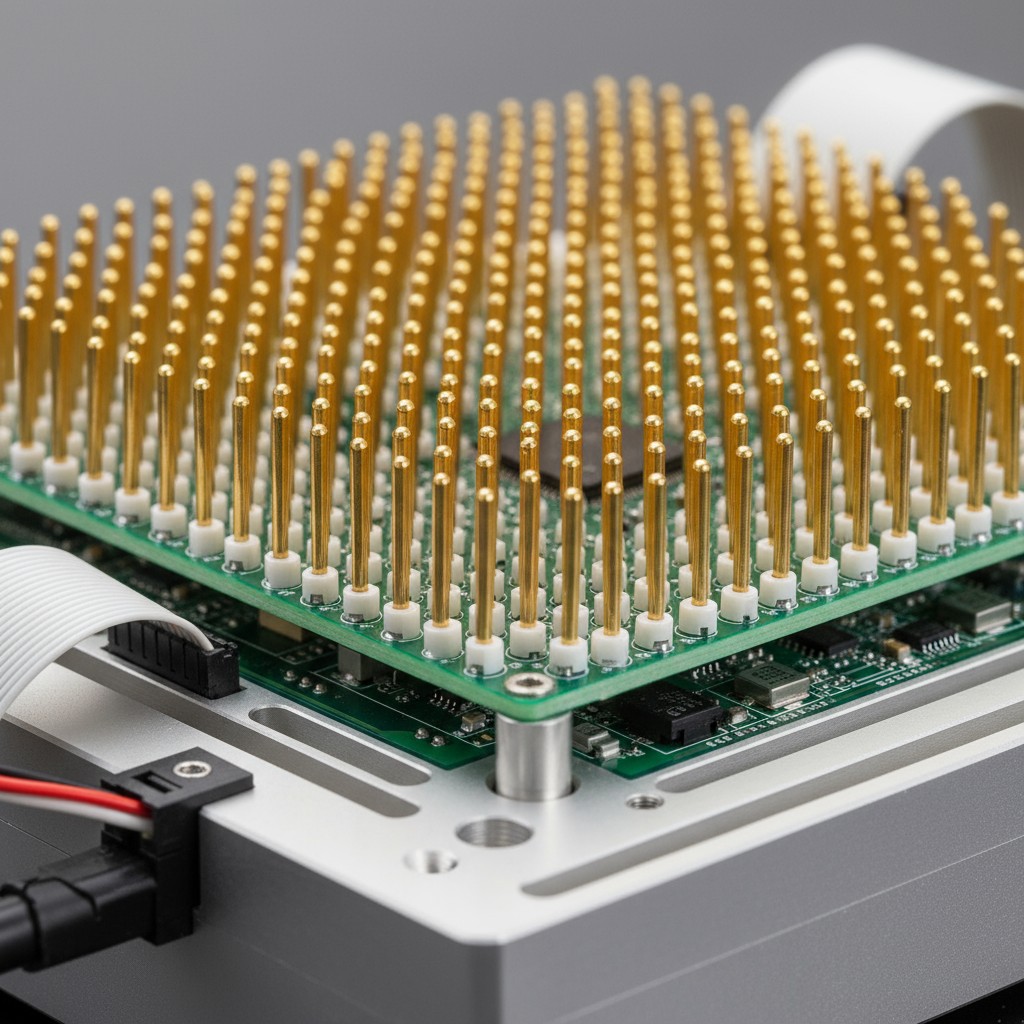

Aunque el fixture es el costo más visible de la ICT, la verdadera carga económica es mucho más amplia. Un fixture ICT personalizado no es una compra estándar; es un artefacto diseñado específicamente, construido para la disposición de la placa. El proceso de diseño requiere traducir la lista de conexiones y la colocación de componentes en una estructura mecánica equipada con sonda de prueba accionada por resorte, alineada con precisión submilimétrica a cada punto de prueba. El fixture debe tener en cuenta las tolerancias de componentes, la deformación de la placa y el desgaste de las sondas. Luego debe ser validado y depurado, un proceso que a menudo revela problemas imprevistos con el acceso a las sondas o la integridad de la señal.

Costos de ingeniería y tiempos de entrega del fixture

El coste de ingeniería para un fijador moderadamente complejo generalmente oscila entre $8,000 y $15,000. Las tablas de alta densidad con componentes de paso fino o acceso limitado a puntos de prueba pueden elevar esa cifra hasta $25,000 o más. Esto es puramente el coste de la interfaz mecánica y eléctrica personalizada necesaria para conectar la placa al equipo ICT, separado del gasto de capital del probador en sí.

El tiempo de entrega es igualmente importante. Desde el momento en que se finaliza un diseño de placa, el diseño y fabricación del fijador suelen requerir de dos a cuatro semanas, extendiéndose a seis para diseños complejos. Durante este período, la producción se detiene. Las placas pueden ser ensambladas, pero no se pueden probar. Permanecen en inventario, esperando. Si el diseño cambia durante esta ventana—un evento común en la introducción de nuevos productos—el fijador debe ser revisado o descartado. El reloj se reinicia.

La matemática del punto de equilibrio para lotes de bajo volumen

La trampa económica se vuelve clara cuando los costes del fijador se dividen por la cantidad de unidades. Un fijador de $12,000 para una producción de 100 unidades añade una carga de $120 a cada placa. Para una placa con un bill de materiales de $500, eso es un 24 por ciento de sobrecarga por prueba. Incluso si el proceso ICT es rápido, la eficiencia económica es pobre. El mismo fijador amortizado en 500 unidades reduce el coste por unidad a $24, una sobrecarga mucho más aceptable del cinco por ciento. La diferencia es puramente una función del volumen.

El punto de equilibrio es donde el coste total de ICT—incluyendo ingeniería, configuración y el coste de oportunidad del tiempo de entrega—igualan al coste de una alternativa sin fijador. Para una estrategia que combina escaneo de límites, pruebas sin vectores y una prueba funcional ligera, el coste de infraestructura es significativamente menor. El escaneo de límites no requiere fijador, y las pruebas sin vectores utilizan sensores reutilizables que funcionan sin contacto mecánico. Cualquier fijador de prueba funcional suele ser mínimo y genérico, no un artefacto específico para la placa que requiera semanas de ingeniería.

En volúmenes de producción inferiores a 200 unidades, la economía de ICT colapsa. Por debajo de 300 unidades, el caso es marginal, dependiendo de la complejidad de la placa. Solo por encima de 300 unidades, para diseños estables y no iterativos, ICT comienza a tener sentido económico nuevamente.

Lo que realmente son el Boundary Scan y las pruebas sin vectores

La alternativa a las pruebas basadas en fixtures no es un compromiso en rigor, sino un cambio hacia métodos que aprovechan la infraestructura de diseño existente y la medición sin contacto. Estas herramientas fueron desarrolladas para abordar la misma tendencia que socava la TIC: el aumento de la densidad de la placa y la reducción del acceso a los puntos de prueba físicos.

El escaneo de límites, formalizado en el estándar IEEE 1149.1 (comúnmente conocido como JTAG), incorpora la lógica de prueba directamente en los circuitos integrados de una placa. Los chips compatibles incluyen una cadena de celdas en cada pin de entrada y salida. Durante una prueba, una interfaz simple de cuatro cables desplaza patrones en estas celdas, controlando los estados lógicos en las redes de la placa. Los estados resultantes se capturan y se desplazan para su análisis, permitiendo al probador controlar y observar señales a nivel de pin sin contacto físico. Este método no invasivo es muy efectivo para detectar cortocircuitos, aberturas y fallos atascados entre dispositivos compatibles.

Las pruebas sin vectores complementan esto utilizando mediciones capacitivas e inductivas para detectar fallos en toda la placa. Una matriz de sensores colocada cerca de la placa mide la firma electromagnética de los componentes y trazas ensamblados. Los cortocircuitos crean acoplamientos capacitivos medibles; las aberturas muestran cambios característicos en la impedancia. El método es rápido, no invasivo y puede inferir la presencia de componentes, polaridad y valor aproximado, siendo efectivo para detectar defectos de fabricación grandes como componentes faltantes, diodos invertidos o trazas puente.

Comparación de Cobertura: Los Números Detrás del Compromiso

La objeción principal a abandonar ICT es la cobertura. Aunque ICT puede, en principio, acceder a cada nodo en una placa con suficientes puntos de prueba, la afirmación de que las alternativas son inferiores está incompleta. La verdadera cuestión es si logran una cobertura suficiente para detectar los fallos que realmente ocurren, y si una prueba funcional enfocada puede cerrar la brecha restante.

Qué cubre Boundary Scan

La cobertura de escaneo de frontera depende de cuántos componentes en la placa cumplen con la norma JTAG. Para placas dominadas por lógica digital—microprocesadores, FPGAs, memoria—la cobertura es extensa. La cadena de escaneo puede probar la interconexión entre estos dispositivos con tasas de detección de fallos que superan el 95 por ciento para cortocircuitos, circuitos abiertos y fallos persistentes. Una placa donde el 80 por ciento de los componentes cumplen con la norma logrará aproximadamente un 70 a 85 por ciento de cobertura neta. Las secciones analógicas, componentes discretos y partes legacy son invisibles para este método. Sin embargo, para diseños con mucho contenido digital, el escaneo de frontera por sí solo ofrece una cobertura comparable al ICT para la capa de interconexión, donde ocurren la mayoría de los fallos de ensamblaje.

Lo que añade la prueba sin vectores

Las pruebas sin vector rellenan los huecos que deja la exploración de límites, particularmente para componentes pasivos y defectos de ensamblaje grueso. Las mediciones capacitivas pueden detectar resistencias faltantes, valores incorrectos de capacitores y diodos colocados al revés. Aunque menos precisas que las mediciones directas de ICT, son una pantalla efectiva para los errores más comunes: componente incorrecto, componente faltante o desalineación grave. Esto añade otro 10 a 20 por ciento a la cobertura total de fallos, proporcionando una capa de verificación sin contacto para las piezas que la exploración de límites no puede ver.

La brecha restante y cómo la prueba funcional ligera la cierra

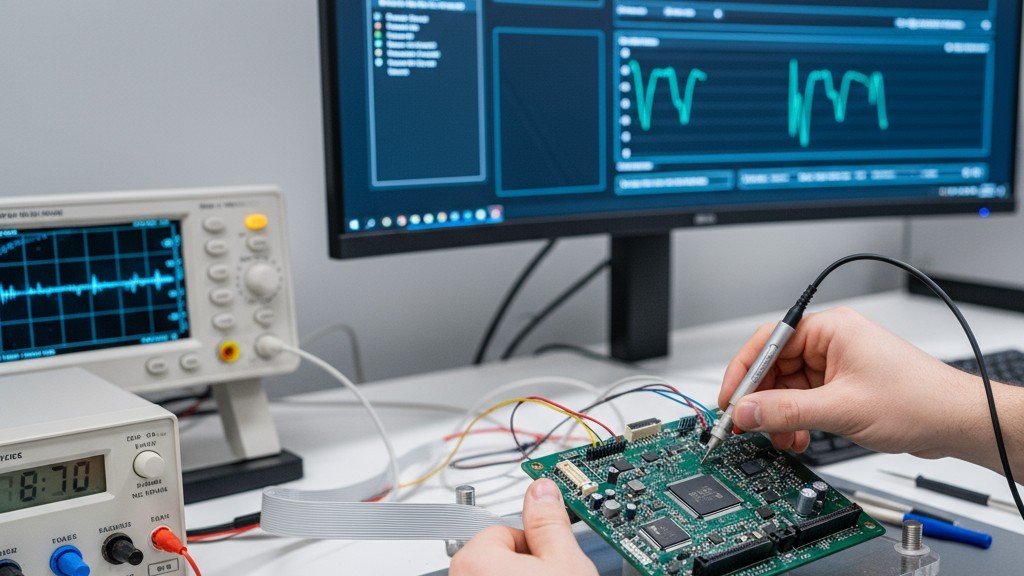

La combinación de escaneo de límites y pruebas sin vectores todavía deja una brecha en la validación funcional y el rendimiento analógico. Un componente puede estar presente y conectado correctamente pero aún así fallar en operar dentro de las especificaciones. Una fuente de alimentación puede entregar voltaje pero con un rizado excesivo. Aquí es donde entra en juego una prueba de circuito funcional ligera (FCT). A diferencia de una configuración completa de ICT, una FCT ligera valida que la placa realiza su función prevista en condiciones realistas. Aplica energía, estimula entradas y mide salidas. Para un controlador de motor, podría verificar la generación de señales PWM; para una placa de comunicación, podría comprobar la transmisión de datos sin errores. La prueba funcional complementa las pruebas estructurales, detectando fallos que otros métodos no pueden ver.

En conjunto, estos tres métodos logran típicamente una cobertura de fallos del 85 al 95 por ciento. Esto no es el 100 por ciento, pero tampoco lo es ICT en la práctica. Debido a las limitaciones en los puntos de prueba y al desgaste de las sondas, la cobertura real de ICT a menudo es menor que su máximo teórico. La diferencia en cobertura es mucho menor que la penalización en coste y tiempo de entrega.

La Ventaja del Bucle de Depuración

La cobertura de la prueba es solo la mitad de la ecuación del valor; la otra mitad es la velocidad y precisión del aislamiento de fallos. Una prueba que detecta un fallo pero proporciona diagnósticos vagos aumenta el tiempo y el coste necesarios para localizar la causa raíz.

Mientras que ICT es excelente para detectar fallos, sus diagnósticos pueden ser frustrantemente vagos. Un probador podría informar que el nodo 47 está en corto a tierra, pero no explica por qué ni dónde. El técnico debe trazar el esquema, localizar la red y realizar una inspección visual en el área—un proceso que puede consumir horas en una placa densa y multicapa.

Los diagnósticos de escaneo de frontera son fundamentalmente diferentes. Debido a que la cadena de escaneo está embebida en los componentes, la prueba aisla fallas a pines y dispositivos específicos. Una corto circuito entre dos redes se identifica por los pines exactos del dispositivo involucrados, reduciendo la búsqueda a unos pocos milímetros cuadrados. Las aberturas se detectan entre pares específicos de conductor y receptor. La salida diagnóstica no es un código de falla. Es un mapa. Esta precisión significa que una falla que lleva una hora depurar con datos ICT a menudo puede resolverse en 10 a 20 minutos con escaneo de frontera. Para una producción de 100 unidades con una tasa de falla típica, el tiempo acumulado de depuración ahorrado puede superar las 10 horas.

El Tiempo de Entrega y la Flexibilidad: El Valor Oculto

El argumento económico contra el ICT para bajos volúmenes es convincente, pero la penalización por tiempo de entrega es igual de significativa. El proceso de ingeniería del dispositivo, que dura de dos a cuatro semanas, impone una demora obligatoria entre la congelación del diseño y la preparación para la prueba. Para la introducción de nuevos productos, donde el tiempo de comercialización es crítico, esta demora suele ser inaceptable.

El escaneo de frontera y la prueba sin vectores eliminan esta espera. La configuración de la prueba puede hacerse en horas o días, no en semanas, permitiendo que las placas pasen de montaje a prueba y luego a envío en un flujo continuo. Esta flexibilidad es crucial cuando los diseños se iteran. Una prueba temprana con prototipo puede revelar problemas que requieren cambios en el diseño de la placa. Con ICT, cada revisión exige un dispositivo nuevo o reprogramado, incurring en el costo y tiempo de entrega una y otra vez. Los patrones de prueba de escaneo de frontera, generados a partir de la lista de Redes, se actualizan automáticamente con el diseño. Esto crea una estrategia de prueba que soporta el desarrollo iterativo en lugar de penalizarlo.

Cuándo seguir eligiendo TIC

Pero el caso contra ICT de bajo volumen no es absoluto. Ciertos diseños y contextos de producción todavía justifican la inversión.

Las placas con secciones analógicas o RF de alta densidad son malos candidatos para una estrategia puramente sin dispositivo. Los componentes analógicos carecen de lógica de escaneo de frontera, y características críticas de rendimiento como la ganancia o el ruido de fase no pueden verificarse estructuralmente. Si el circuito analógico o RF representa más del 40 por ciento de la funcionalidad de la placa, el caso para ICT se fortalece considerablemente.

Industrias impulsadas por cumplimiento, como la médica, aeroespacial y automotriz, a menudo operan bajo regulaciones que exigen una cobertura de prueba o métodos específicos. Si una norma gobernante requiere pruebas en circuito o acceso a nivel de nodo equivalente, las estrategias alternativas pueden no ser suficientes. Aquí, el costo del ICT es un costo innegociable de entrada al mercado.

Finalmente, un camino claro y comprometido hacia la producción en volumen alto cambia las reglas del juego. Si una primera producción de 150 unidades se espera que escale a 1,000 unidades en seis meses, el costo del dispositivo se amortiza en todo el volumen anticipado. Esto requiere una alta confianza en la previsión y un diseño estable, pero puede hacer que la inversión inicial valga la pena.

Construyendo la Estrategia de Prueba Alternativa

Reemplazar ICT no es un simple intercambio; es una reconfiguración de la arquitectura de prueba en una estrategia en capas, donde cada capa captura fallas que las otras podrían pasar por alto.

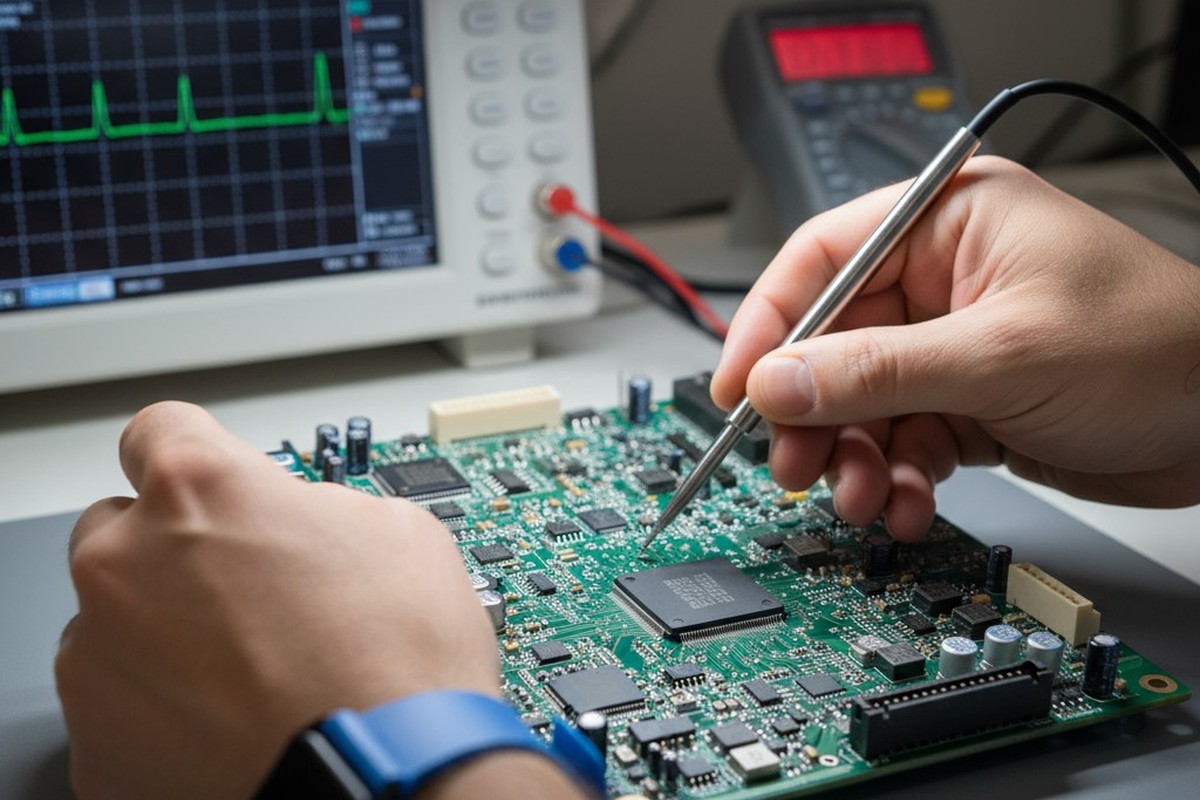

El proceso debe ser secuencial. La primera capa es el escaneo de frontera, que se ejecuta rápidamente en todos los dispositivos compatibles para detectar fallas de interconexión en las porciones digitales de la placa. Las placas que fallan se marcan para re-diseño inmediato, evitando fallas catastróficas cuando se aplica energía posteriormente. La segunda capa es la prueba sin vectores, que se ejecuta en toda la placa para detectar componentes pasivos faltantes o incorrectos, cortocircuitos graves y errores de polaridad. Cubre los componentes y redes invisibles para la cadena de escaneo.

La tercera y última capa es una prueba funcional enfocada. Con errores estructurales ya filtrados, la placa se alimenta para validar sus funciones críticas bajo condiciones de operación realistas. El alcance se ajusta al propósito de la placa—verificar la precisión del ADC en una placa de adquisición de datos o la regulación de carga en una fuente de alimentación. Esta secuencia asegura que las fallas catastróficas se detecten tempranamente y de manera no destructiva, minimizando el tiempo de depuración en fallas funcionales más complejas.

Para placas con complejidad híbrida—como un núcleo digital denso rodeado por acondicionamiento de señales analógicas, por ejemplo—una estrategia híbrida puede ser la mejor. Se puede diseñar un dispositivo ICT parcial para sondear solo la sección analógica crítica, dejando la parte digital para el escaneo de frontera. La economía de un dispositivo parcial es más favorable, reduciendo costos y tiempo de entrega, pero aún brindando la cobertura necesaria para todo el diseño.