ส่วนประกอบที่อันตรายที่สุดบน PCB แบบสัญญาณผสมไม่ใช่ BGA และไม่ใช่ QFN ที่มีแผ่นความร้อน แต่มันคือฝาครอบโล่ RF ขณะที่วิศวกรใช้เวลาหลายสัปดาห์ในการจำลองการจับคู่ความต้านทานและการปรับจูนเสาอากาศ ฝาครอบโล่จริงๆ มักถูกวางลงบนเลย์เอาต์เป็นความคิดทีหลัง—กล่องโล่งง่ายๆ ที่วาดด้วยเส้นบัดกรีทึบบนชั้นกลไก

“ความคิดทีหลัง” นั้นคือระเบิดเวลาการผลิต เมื่อสายการผลิตหยุดทำงานเพราะ 15% ของบอร์ดล้มเหลวในการทดสอบการสั่นสะเทือน หรือเมื่อคาปาซิเตอร์ 0201 เกิดช็อตลัดอย่างลึกลับหลังจากใช้งานสามเดือน ผู้ร้ายมักเป็นกระบวนการประกอบโล่ป้องกัน ปัญหามักไม่มาจากประสิทธิภาพการป้องกันเอง แต่มาจากการปฏิเสธที่จะยอมรับว่าโล่เป็นฮีทซิงก์ความร้อนขนาดใหญ่และกับดักก๊าซ หากคุณออกแบบรอยเท้าโล่โดยไม่เคารพพลศาสตร์ของของเหลวบัดกรีที่หลอมเหลว คุณไม่ได้สร้างกรงฟาราเดย์ แต่คุณกำลังสร้างเครื่องกำเนิดเม็ดบัดกรี

ศัตรูที่มองไม่เห็น: การเกิดเม็ดบัดกรี

กลไกความล้มเหลวนี้เรียบง่าย รุนแรง และเล็กมาก เมื่อคุณพิมพ์เส้นบัดกรีทึบมาตรฐานสำหรับกรอบโล่ มันจะสร้างการปิดผนึกเปียกกับพื้นผิว PCB ในระหว่างการรีโฟลว์ ฟลักซ์ภายในบัดกรีนั้นจะระเหยและต้องระบาย ในข้อต่อชิ้นส่วนทั่วไป ก๊าซจะหนีออกทางขอบ แต่ใต้ผนังโล่หนักที่มีเส้นบัดกรีต่อเนื่อง ก๊าซจะถูกกักขัง

แรงดันจะเพิ่มขึ้นจนเกิดการระเบิดอย่างมีประสิทธิภาพ ดันเม็ดบัดกรีหลอมเหลวขนาดเล็กออกมาจากใต้ผนังโล่ เหล่านี้คือ “เม็ดบัดกรี” ในกรณีที่เลวร้ายที่สุด—ซึ่งมักพบในสายการผลิตรถยนต์ปริมาณมาก—เม็ดเหล่านี้ลอยไปบนพื้นผิวบอร์ดบนเบาะฟลักซ์ และในที่สุดก็ติดอยู่ใต้ชิ้นส่วนใกล้เคียง เช่น พาสซีฟ 0201 หรือขา IC ที่มีระยะขาเล็ก สร้างการลัดวงจรที่แข็งแรง เพราะเม็ดบัดกรีมักจะติดแน่น ใต้ ตัวชิ้นส่วน การตรวจสอบอัตโนมัติด้วยแสง (AOI) มาตรฐานจะไม่พบมัน แม้แต่การตรวจสอบด้วยรังสีเอกซ์ก็ไม่ใช่คำตอบทั้งหมด บนบอร์ดที่มีความหนาแน่นสูงและมีชั้นกราวด์ เม็ดบัดกรีเล็กๆ สามารถซ่อนตัวในสัญญาณรบกวนได้ การแก้ไขที่แท้จริงเพียงอย่างเดียวคือการป้องกันไม่ให้เม็ดบัดกรีเกิดขึ้นตั้งแต่แรก

Aperture Engineering: ความผิดพลาด 1:1

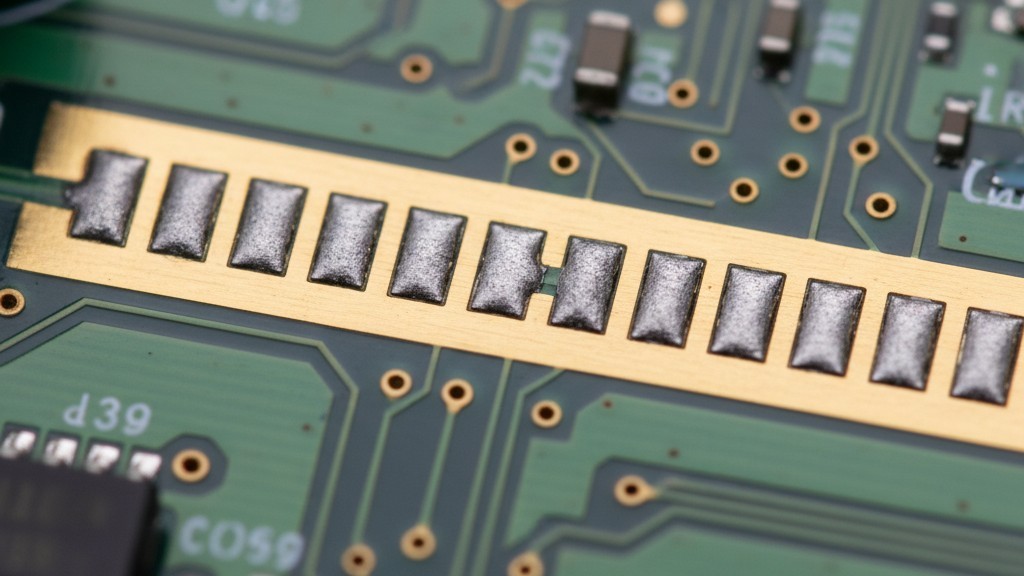

ข้อผิดพลาดที่พบบ่อยที่สุดในการออกแบบโล่คือความสัมพันธ์ 1:1 ระหว่างแผ่นทองแดงกับช่องเปิดสเตนซิล หากแผ่นกว้าง 1 มม. วิศวกรจะขอให้ฝากบัดกรีกว้าง 1 มม. นั่นคือความผิดพลาด โล่ไม่จำเป็นต้องมีการปิดผนึกบัดกรีแบบกันอากาศเพื่อทำหน้าที่เป็นตัวบล็อก EMI แต่มันต้องการความต่อเนื่องทางไฟฟ้าและการยึดติดทางกล

เพื่อกำจัดเม็ดบัดกรี คุณต้องทำลายการปิดผนึก ช่องเปิดสเตนซิลไม่ควรเป็นเส้นทึบ แต่ต้องแบ่งเป็นส่วนๆ แนวทางมาตรฐาน IPC-7525 และประสบการณ์จริงในสาย SMT ชี้ไปที่รูปแบบ “เส้นประ” หรือ “หน้าต่าง” โดยการแบ่งฝากบัดกรีเป็นส่วนๆ พร้อมช่องว่างเล็กๆ (โดยทั่วไป 0.3 มม. ถึง 0.5 มม.) คุณจะสร้างช่องระบายสำหรับไอระเหยฟลักซ์ ช่วยลดแรงดันไฮดรอลิกในระหว่างรีโฟลว์และเก็บบัดกรีให้อยู่ในที่ที่ควรอยู่

นักออกแบบมักจะต่อต้านตรงนี้ เพราะกลัวพลังงาน RF จะรั่วผ่านช่องว่าง สำหรับความถี่เชิงพาณิชย์มาตรฐาน (ต่ำกว่า 6GHz) นี่เป็นเรื่องเข้าใจผิดอย่างมาก ความยาวคลื่นสัญญาณใหญ่กว่าช่องว่างบัดกรี 0.3 มม. มาก เว้นแต่คุณจะทำงานในแอปพลิเคชันมิลลิเมตรเวฟขั้นสูง ฟิสิกส์ของคลื่นจะไม่อนุญาตให้ผ่านช่องเปิดเล็กๆ เช่นนี้ ความเสี่ยงของการลัดวงจรจากเม็ดบัดกรีคือความล้มเหลวในการทำงาน 100%; ความเสี่ยงของการรั่วไหล RF จากข้อต่อบัดกรีแบ่งส่วนมีน้อยมาก ให้ความสำคัญกับผลผลิต

นอกจากนี้ คุณต้องลดปริมาณบัดกรี โล่วางอยู่บนบัดกรี; มันไม่มีขาที่ “จม” ลงไป ปริมาณ 1:1 มักทำให้โล่ลอยหรือเอียง (สูญเสียความเรียบ) การลดพื้นที่ครอบคลุมลงเหลือ 50-60% ของพื้นที่แผ่นทองแดงมักเป็นจุดที่เหมาะสม สำหรับเลย์เอาต์ที่ไวต่อความผิดพลาดมาก การใช้ช่องเปิดรูป “แผ่นบ้านกลับด้าน” สามารถดึงบัดกรีส่วนเกินออกจากขอบในของโล่ ช่วยลดโอกาสเกิดเม็ดบัดกรีภายในได้อีก

สถาปัตยกรรม: ปัญหา “กล่องดำ”

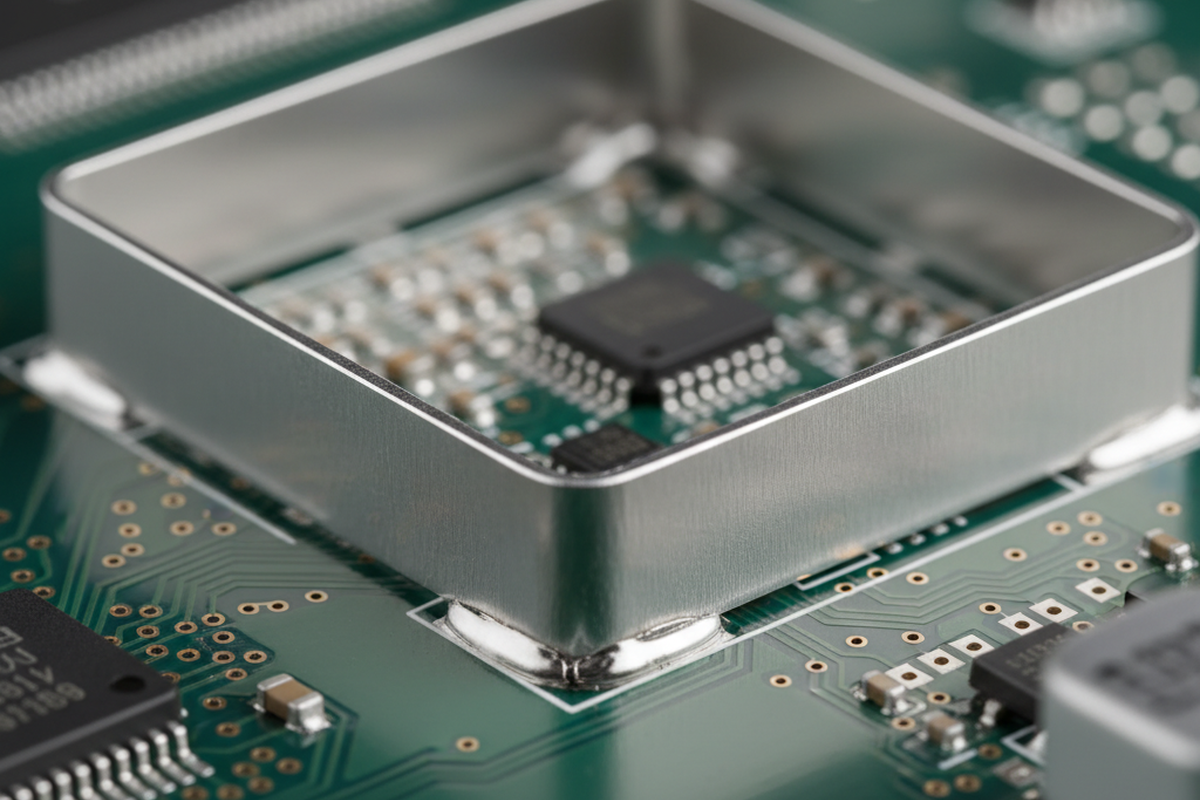

นอกเหนือจากสเตนซิล โครงสร้างทางกายภาพของชิลด์กำหนดความน่าเชื่อถือของอุปกรณ์ มีแรงจูงใจอย่างมากที่จะใช้ชิลด์ชิ้นเดียว (ฝากระป๋องโลหะปั๊มชิ้นเดียวที่บัดกรีติดตรงลงบนบอร์ด) เพราะถูกกว่าและมีโปรไฟล์ต่ำกว่า อย่างไรก็ตาม ชิลด์ชิ้นเดียวจะเปลี่ยนวงจรด้านใต้ให้กลายเป็นกล่องดำ

เมื่อฝากระป๋องนั้นถูกบัดกรีลงไป การตรวจด้วยสายตาจะเป็นไปไม่ได้ ยิ่งไปกว่านั้น การทำความสะอาดก็เป็นไปไม่ได้ หากคุณใช้ฟลักซ์ละลายน้ำ หรือแม้แต่ฟลักซ์ “ไม่ต้องล้าง” ในสภาพแวดล้อมที่มีความชื้น คุณต้องคำนึงถึงสิ่งที่เกิดขึ้นกับคราบที่ถูกกักอยู่ใต้ฝากระป๋องนั้น หากชิลด์มีความสูงช่องว่างเกือบเป็นศูนย์ สารเคมีล้างก็ไม่สามารถไหลเข้าไปข้างใต้ได้ คราบฟลักซ์ยังคงอยู่รวมตัวรอบๆ เส้นลายที่อ่อนไหว เมื่อเวลาผ่านไป—โดยเฉพาะในอุปกรณ์สวมใส่หรืออุปกรณ์การแพทย์ที่สัมผัสความร้อนและความชื้นจากร่างกาย—คราบนี้จะนำไปสู่การเติบโตในลักษณะเดนดริติกและการอพยพทางอิเล็กโทรเคมี วงจรก็เหมือนจะกินตัวเอง

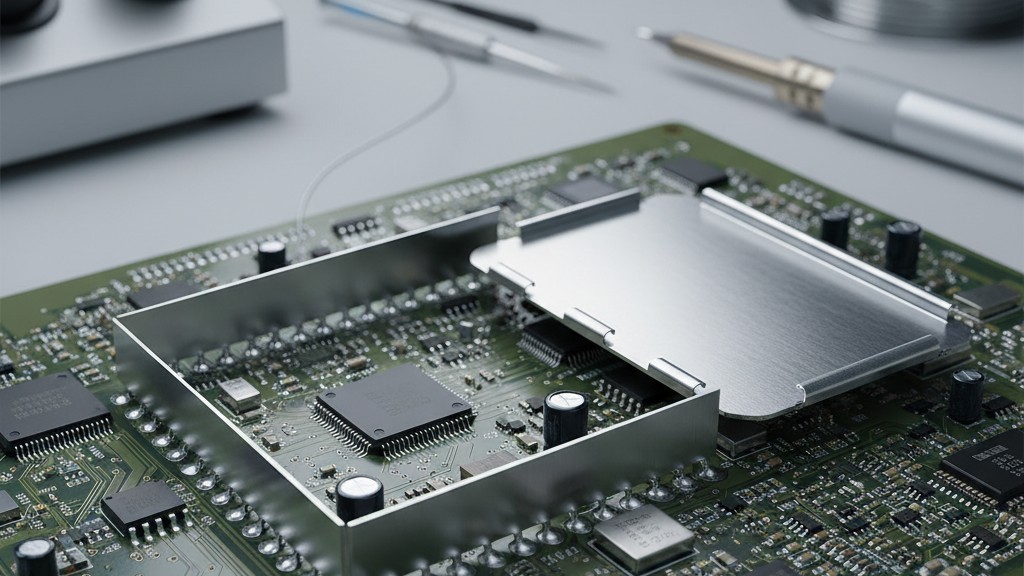

หากความน่าเชื่อถือคือสิ่งสำคัญ ให้ใช้ระบบสองชิ้น: กำแพง (เฟรม) บัดกรีกับบอร์ด และฝาแบบสแน็ปออน วิธีนี้ช่วยให้สามารถตรวจด้วยสายตาอย่างเต็มที่ที่ข้อต่อที่ผ่านการรีโฟลว์และทำความสะอาดคราบฟลักซ์ได้อย่างทั่วถึงก่อนจะสแน็ปฝาลง ใช่แล้ว ต้นทุน BOM จะสูงกว่า แต่ต้นทุนในการทิ้งบอร์ดที่เสร็จแล้วเพราะตัวปรับแรงดัน $0.05 เสียภายในฝากระป๋องที่ปิดผนึก—ซึ่งต้องใช้หัวแร้งลมร้อนในการซ่อมจนดึงแผ่นแพดขึ้นและทำลาย PCB—นั้นสูงกว่าเป็นเท่าทวีคูณ

สำหรับการสร้างต้นแบบหรือบอร์ดที่ต้องเข้าถึงบ่อย ให้พิจารณาใช้คลิปชิลด์ SMT สปริงขนาดเล็กเหล่านี้ยึดฝากระป๋องไว้โดยไม่ต้องใช้แหวนบัดกรีต่อเนื่อง พวกมันขจัดความเสี่ยงเรื่องการบีดได้ทั้งหมด เพราะไม่มีเส้นเพสต์ยาวๆ และยังเอื้อให้ถอดชิลด์ได้ง่ายเมื่อต้องดีบัก แม้มันอาจไม่ให้ความต้านแรงสั่นสะเทือนเทียบเท่ากับเฟรมบัดกรีสำหรับอากาศยาน แต่สำหรับอิเล็กทรอนิกส์สำหรับผู้บริโภคที่ต้องมีความสะดวกในการซ่อมแซมซ่อนอยู่ มันมักจะดีกว่า

การแช่ความร้อน

จากนั้นก็เป็นเรื่องอุณหพลศาสตร์ของเตารีโฟลว์ ชิลด์ RF โลหะโดยสารถือเป็นฮีตซิงก์จริงๆ มวลความร้อนสูงมากเมื่อเทียบกับตัวต้านทานและตัวเก็บประจุเล็กๆ ที่อยู่รอบๆ หากโปรไฟล์รีโฟลว์ของคุณรุนแรง—เร่งความร้อนอย่างรวดเร็ว—ชิ้นส่วนขนาดเล็กจะถึงอุณหภูมิเหลวเร็วกว่าชิลด์โดยมาก

สิ่งนี้นำไปสู่ “ข้อต่อเย็น” เพสต์บัดกรีที่แพดของชิลด์อาจหลอม แต่กำแพงชิลด์เองยังไม่ร้อนพอที่จะรับบัดกรี ฟลักซ์จะไหม้ไป เพสต์จะเปียกกับแพด PCB แต่ไม่เปียกกับกำแพงชิลด์ชุบนิกเกิล ผลลัพธ์คือชิลด์ฝังอยู่ในแอ่งบัดกรีเย็นแทนที่จะยึดเกาะ เมื่อเจอการเปลี่ยนอุณหภูมิหรือแรงกระแทกทางกล ข้อนี้จะแตกทันที

เพื่อแก้ไข โปรไฟล์รีโฟลว์ต้องมี “โซนบ่ม” ที่มีเวลาคงอุณหภูมิ (ปกติระหว่าง 150°C ถึง 180°C) นาน 60 ถึง 90 วินาที วิธีนี้ช่วยให้มวลความร้อนของชิลด์ตามขึ้นมาทันกับส่วนอื่นๆ ของบอร์ด คุณไม่สามารถแค่ยิงความร้อนอย่างรุนแรงได้; ต้องปล่อยให้บ่มจนโลหะชิลด์ร้อนพอที่จะเปียก นี่อาจทำให้ UPH (Units Per Hour) ช้าลง แต่รับประกันว่าข้อต่อเป็นทางโลหะวิทยา ไม่ใช่แค่รูปลักษณ์

รายการตรวจสอบการควบคุมกระบวนการ

ในการสร้างชิลด์ที่ไม่ลดอัตราผลผลิต ให้ปฏิบัติตามลำดับขั้นตอนป้องกันนี้:

- แบ่งช่องเปิด: อย่าพิมพ์เส้นเพสต์ต่อเนื่อง ใช้ลวดลายประเพื่อมีช่องว่าง 0.3mm-0.5mm เพื่อให้ก๊าซไหลออกได้

- ลดปริมาตร: ตั้งเป้าหมายการปกคลุมเพสต์ที่ 50-60% เมื่อเทียบกับพื้นที่แพด

- เคารพมวล: ตรวจสอบให้แน่ใจว่าโปรไฟล์การรีโฟลว์มีโซนซ็อกที่ยาวพอที่จะให้ความร้อนกับผนังโล่ ไม่ใช่แค่เพสท์เท่านั้น

- ออกแบบเพื่อความเป็นจริง: ถ้าคุณไม่สามารถทำความสะอาดใต้สิ่งนั้นได้ ให้สมมติว่าจะเกิดการกัดกร่อนเว้นแต่คุณจะตรวจสอบฟลักซ์และสภาพแวดล้อมอย่างสมบูรณ์แบบ ควรใช้ระบบสองชิ้นหรือคลิปเมื่อมีงบประมาณเพียงพอ

ฟิสิกส์ไม่สนใจเส้นตายของคุณ ถ้าคุณดักจับก๊าซ มันจะระเบิด ถ้าคุณขโมยความร้อน การบัดกรีจะไม่ติดกัน ออกแบบกระบวนการ ไม่ใช่แค่แผนผังวงจร