เมื่อไฟล์การออกแบบเข้าสู่คิววิศวกรรม เราไม่ดูที่เส้นทางหรือการวางตำแหน่งชิ้นส่วนก่อน หน้า เรามองที่ชั้นแม่แบบ Paste Mask.

นักออกแบบส่วนใหญ่มองว่าชั้นนี้เป็นการแปลตรงของจานทองแดง: ถ้ามีจานบนบอร์ด ควรมีรูขนาดเท่ากันในแม่แบบ การทำงานแบบ 1:1 นี้เป็นระเบียบ เรียบร้อย และสมบูรณ์แบบทางคณิตศาสตร์ในสภาพแวดล้อม CAD มันยังเป็นสาเหตุที่พบบ่อยที่สุดของข้อบกพร่องในการประกอบบนบอร์ดเทคโนโลยีผสมสมัยใหม่.

ปัญหา? ไฟล์ Gerber เป็นแผนที่สองมิติ แต่จุดเชื่อมต่อซ็อลเดอร์เป็นปริมาณสามมิติ ทันทีที่เราย้ายจากหน้าจอไปยังพื้นการผลิต เรากำลังจัดการกับพลศาสตร์ของของไหล, สัมผัสผิว และข้อจำกัดทางกายภาพของการผลักดิสก์แท่งโลหะผ่านแผ่นเหล็ก.

ถ้าเราเผลอตัดแม่แบบโดยอิงจากผลลัพธ์ “100% coverage” จากซอฟต์แวร์ ECAD ของคุณ เรารับประกันความล้มเหลว บนบอร์ดที่มีทั้งตัวเชื่อมต่อหนักและไมโครชิปที่มีความหนาสูง วิธีการใช้แนวทางเดียวกันอย่างสม่ำเสมอทำให้ครึ่งหนึ่งของบอร์ดได้รับ paste มากเกินไป ในขณะที่อีกครึ่งหนึ่งขาดแคลน เราไม่แก้ไขข้อมูลแม่แบบของคุณเพื่อให้ยากขึ้น; เรายอมทำเพราะฟิสิกส์ต้องการมัน

ซ็อลเดอร์เป็นปัญหาด้านปริมาณ

ลืมเรื่อง “coverage” ไปเลย เราต้องคิดเป็นลูกบาศก์มิล.

ความสมบูรณ์ของกลุ่มเชื่อมต่อ—โดยเฉพาะส่วนประกอบด้านไฟฟ้าและตัวเชื่อมต่อ—ขึ้นอยู่กับปริมาณของฟิลเลตยึดเหนี่ยวโลหะที่เกิดขึ้น จานพิมพ์หน้าสามารถดูดีด้วยการเคลือบ paste หนา 5 มิล แต่หัวผ่านรูแบบรีฟลอว์และตัวเชื่อมต่อ USB-C เป็นสิ่งที่แตกต่างกัน.

นักออกแบบมักตกใจเมื่อส่วนเชื่อมต่อขาดในระหว่างการทดสอบต้นแบบ โดยเข้าใจผิดว่าส่วนประกอบชำรุดหรือเคสอ่อนแอ จริง ๆ แล้ว ปัญหามักเป็นปัญหาความหนาของแม่แบบ USB-C มีขาโครงสร้างที่ต้องมีการยึดแน่นลึกเข้าไปในแท่งของแผ่นวงจร. ถ้าเราใช้แผ่นฟอยล์มาตรฐาน 4 มิลหรือ 5 มิล (ซึ่งเป็นแบบทั่วไปสำหรับบอร์ดสัญญาณส่วนใหญ่) เราจะส่งมอบซ็อลเดอร์เพียงบางส่วนที่จำเป็นต้องเติมเต็มในท่อของบอร์ดนั้น Paste จะพิมพ์บนผิว, ฟลอว์, และหายเข้าไปในรู ทำให้เกิด meniscus ที่อ่อนแอและขาดแคลน ซึ่งจะอ่อนแรงเมื่อใส่ครั้งแรก.

เพื่อแก้ไขปัญหานี้ เราต้องคำนวณปริมาณของรูหยุดตามความยาวของปลายให้หักล้างกัน พร้อมทั้งเพิ่ม Buffer 10% สำหรับการเผาไหม้ของฟลักซ์ และย้อนกลับการออกแบบรูแม่แบบเพื่อส่งมอบ paste ในปริมาณดังกล่าว บ่อยครั้งจัดขนาด pad บนบอร์ดไม่พอที่จะรองรับ paste ที่เปียกนั้น ซึ่งบีบบังคับให้เรากำหนดพิมพ์ซ้ำ—การพิมพ์ paste บนแม่แบบซ่อนเพื่อให้มันดึงกลับมายัง pad ระหว่างการ reflow.

อัตราส่วนพื้นที่ระดับพื้น

ในขณะที่ชิ้นส่วนขนาดใหญ่ขาดอาหาร ชิ้นส่วนเล็กกลับมีปัญหาตรงกันข้าม: พวกมันไม่ยอมปล่อย นี่คือจุดที่กฎ “Area Ratio” กลายเป็นพื้นผิวที่สามารถผลิตได้อย่างเข้มงวด.

การพิมพ์สแตนซิลเป็นการต่อสู้ระหว่างสองแรง: ความตึงผิวของสารเคลือบที่ติดกับแผ่น PCB และแรงเสียดทานของสารเคลือบที่ติดกับผนังด้านในของรูสแตนซิล เพื่อให้สารเคลือบปล่อยตัวสำเร็จ พื้นที่ของแผ่นต้องมีขนาดใหญ่กว่าพื้นที่ของผนังรูอย่างมีนัยสำคัญ

มาตรฐานอุตสาหกรรม (IPC-7525) ตั้งเขตอันตรายที่อัตราส่วน 0.66 หากอัตราส่วนลดลงต่ำกว่านี้ (เช่น BGA ชิพลายระยะ 0.4 มม. หรือ capacitor ขนาด 01005) สารเคลือบจะอุดตันอยู่ภายในสแตนซิลแทนที่จะวางบนแผ่น คุณจะได้การพิมพ์ดีหนึ่งครั้ง อาจสองครั้ง แล้วรูจะอุดตัน ตัวเครื่องตรวจสอบด้วยแสงออปติคอลอัตโนมัติ (AOI) จะเริ่มรายงาน “บัดกรีไม่เพียงพอ” โดยทันที

เราสามารถลองหลอกลวงเล็กน้อยด้วยการเคลือบ nano ซึ่งทำให้เหล็กเป็นไฮโดรโฟบิก โดยการหล่อลื่นผนังของรู แต่เป็นการแก้ไขชั่วคราวเท่านั้น เคลือบเหล่านี้จะสึกหรอหลังการใช้งาน 10,000 วงจร หรือการทำความสะอาดด้วยวิธีการแบบกวาดอย่างรุนแรง วิธีแก้ปัญหาแบบถาวรเดียวคือการเปลี่ยนรูปทรงเรขาคณิต: เราสามารถทำให้รูใหญ่ขึ้น (เสี่ยงต่อการเชื่อมต่อกัน) หรือทำแผ่นสแตนซิลบางลงเพื่อ ลดพื้นที่ผนัง

ความขัดแย้งระหว่างชิ้นส่วนขนาดใหญ่ / ขนาดเล็ก

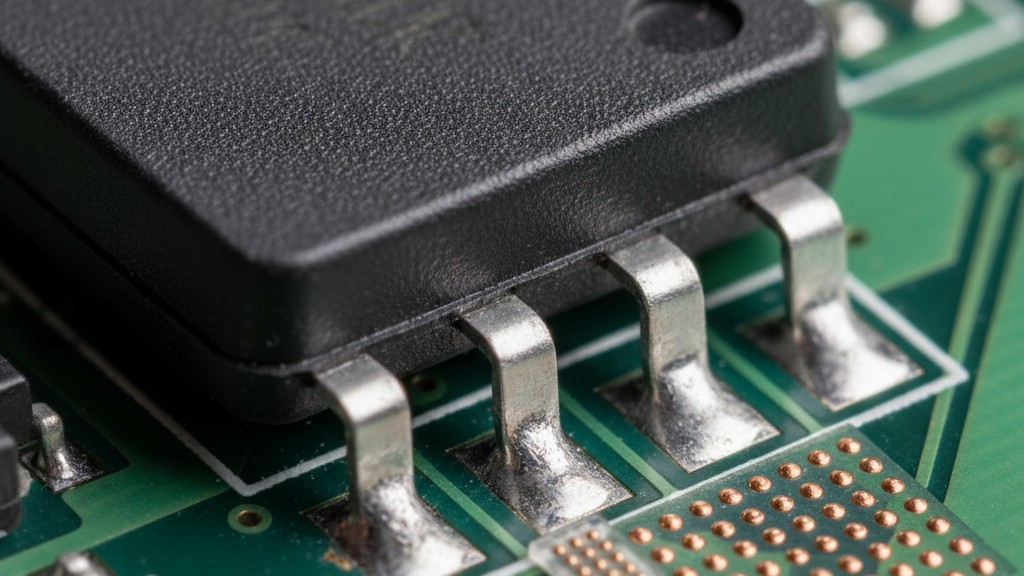

ตอนนี้เราเจอปัญหาหลักของการประกอบอุปกรณ์อิเล็กทรอนิกส์ยุคใหม่: ปัญหา ‘ชิ้นส่วนใหญ่ / ชิ้นส่วนเล็ก’ คุณอาจมีตัวควบคุมแรงดันไฟฟ้า D2PAK ที่ต้องการบัดกรีจำนวนมากเพื่อระบายความร้อน อยู่ติดกันกับแพ็กเกจระดับเวเฟอร์ขนาด 0.35 มม. ที่ต้องการผสมสารเคลือบเพียงเล็กน้อยเพื่อป้องกันการลัดวงจร

ถ้าเราใช้สแตนซิลล์ฟอยล์ขนาด 5mil ซึ่งเป็นตัวเลือกเริ่มต้นสำหรับคำขอใบเสนอราคา 90% ที่เราเห็น — เราอาจทำให้ชิ้นส่วนอย่างใดอย่างหนึ่งเสีย ไป ฟอยล์ 5mil ให้ปริมาณพอสำหรับ D2PAK แต่บางเกินไปสำหรับชิปเวเฟอร์ขนาดเล็ก; อัตราส่วนด้านจะผิด และสารเคลือบจะไม่ปล่อยออก หากเปลี่ยนเป็นฟอยล์ขนาด 3mil เพื่อรองรับชิปขนาดเล็ก D2PAK จะขาดแคลนและเกิดช่องว่างและความล้มเหลวทางความร้อน

นักออกแบบมักถามว่า “ทำไมคุณไม่ลดขนาดรูสำหรับชิ้นส่วนเล็ก?” เราทำได้ แต่ต้องจำไว้ว่า อัตราพื้นที่: การลดขนาดรูโดยรักษาความหนาของฟอยล์ให้คงที่นั้นจะทำให้อัตราแย่ลง คุณไม่สามารถแก้ปัญหาของแกน Z ด้วยการปรับแกน X-Y

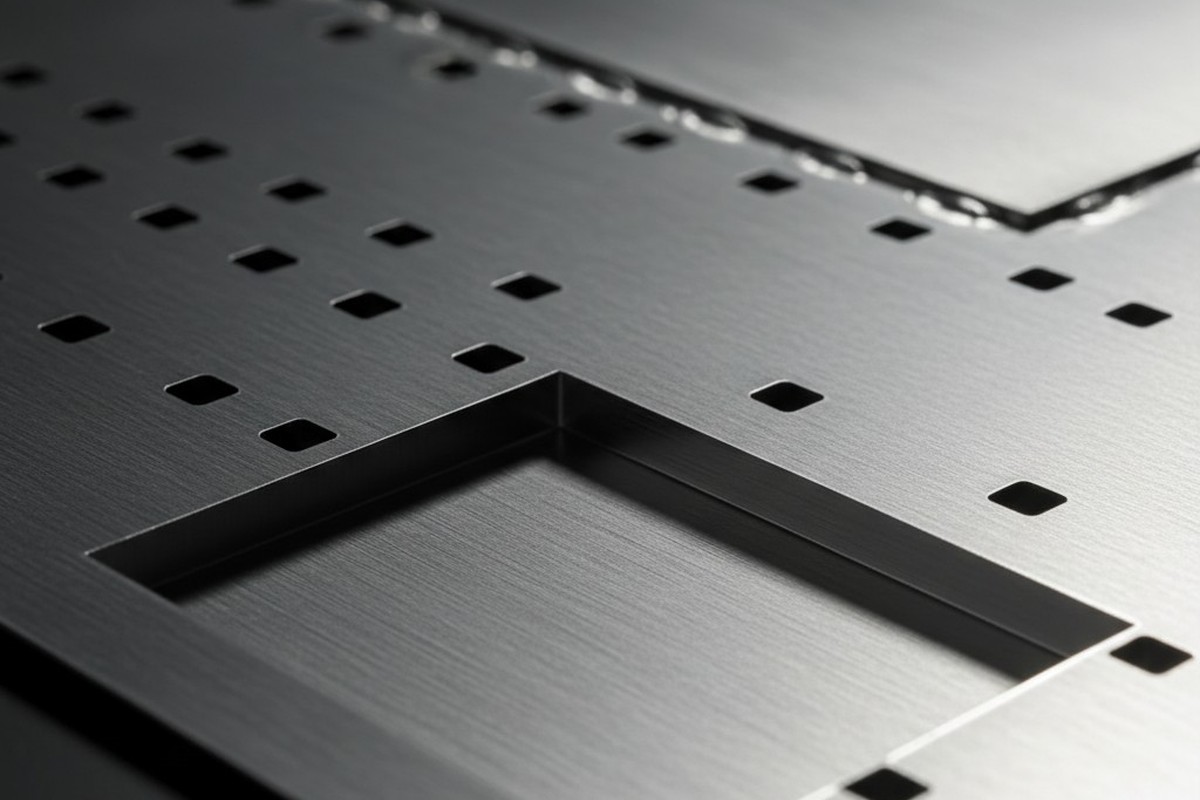

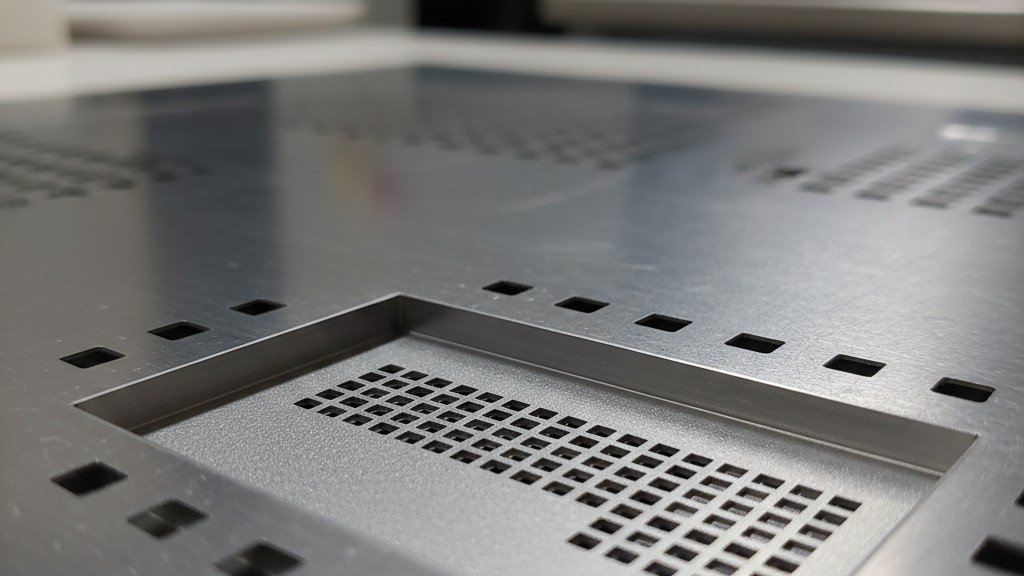

ภูมิประเทศวิศวกรรม: แม่แบบขั้นตอน

เราต้องปฏิบัติกับสแตนซิลน้อยกว่าทางแบนราบ และเปรียบเสมือนแผนที่ภูมิประเทศ

เราใช้สแตนซิลแบบขั้นเพื่อสร้างโซนความหนาที่เป็นตำแหน่งเฉพาะ สำหรับ D2PAK หรือคอนเนคเตอร์ USB เราอาจ ‘ขึ้นระดับ’ สแตนซิลโดยเชื่อมแท็บเหล็กความหนา 6mil หรือ 8mil ไปยังบริเวณนั้น สำหรับ BGA ที่มีระยะห่างเล็ก เราแกะสลัก ‘ลงระดับ’ เป็นแอ่งที่ลดความหนาเหลือ 3.5mil หรือ 3mil สำหรับพื้นผิวของชิ้นส่วนเท่านั้น

นี่ไม่ใช่มนต์วิเศษ; มันต้องการการวางแผนอย่างละเอียด ชั้นวางซิลล์มีความยืดหยุ่น แต่ไม่ใช่น้ำ บนชั้นนี้ต้องมีพื้นที่เชื่อมต่อ—โดยปกติ 50 ถึง 100 mils—เพื่อให้สามารถขึ้นหรือลงบนขั้นโดยไม่ข้ามหรือดูดสารเคลือบออกจากรู เราต้องวางแผนโซนที่ไม่สามารถสัมผัสได้อย่างรอบคอบ เพื่อให้แน่ใจว่าอุปกรณ์สำคัญไม่มีอยู่บนทางลาดของขั้น เมื่อทำอย่างถูกต้องแล้ว จะสามารถพิมพ์สารเคลือบจำนวนมากสำหรับชิ้นส่วนพลังงานและการวางฝากระพือแบบละเอียดสูงสำหรับไมโครชิ้นส่วนในครั้งเดียว ทำให้แผ่นวงจรที่ ‘ไม่สามารถสร้างได้’ กลายเป็นแผ่นที่ผลผลิตได้ถึง 99%

แผ่นหน้าต่างและการออกก๊าซ

การแก้ไขทางเรขาคณิตไม่ได้จำกัดอยู่แค่ความหนา เรายังต้องต่อสู้กับพฤติกรรมของฟลักซ์เองด้วย

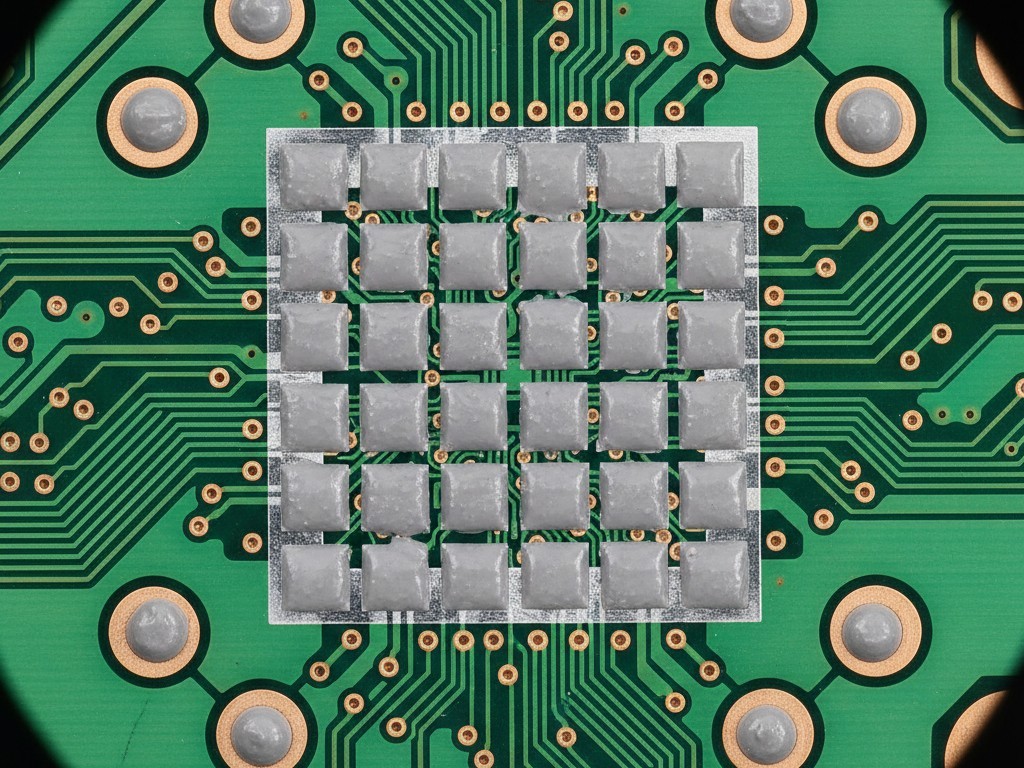

ใต้แผ่นความร้อนขนาดใหญ่ เช่นใน QFN หรือ FET กำลังไฟล์ นักออกแบบมักวาดแกนบล็อกสารเคลือบที่ตรงกับแผ่นทองแดง หากเราพิมพ์เช่นนั้น เราจะกักเก็บของเหลวระเหย (พาหนะของฟลักซ์) ไว้ภายใต้ชิปในระหว่างการรีโฟลว์ เมื่อฟลักซ์เดือดก๊าซจะไม่มีทางออก ทำให้เกิดช่องว่างขนาดใหญ่—ฟองอากาศภายในจุดบัดกรี ซึ่งเป็นอุปสรรคในการถ่ายเทความร้อน

เพื่อป้องกันสิ่งนี้ เราจะไม่สนใจบล็อกแข็งใน Gerber และใช้การลดขนาด ‘หน้าต่าง’ เราจะแบ่งรูปร่างสี่เหลี่ยมขนาดใหญ่เป็นตารางของสี่เหลี่ยมเล็กๆ ซึ่งแยกออกจากกันด้วยช่องว่าง 10-15 มิล ซึ่งช่องว่างเหล่านี้ทำหน้าที่เป็นทางด่วนให้แก๊สออกมาได้ ฟังดูขัดกับความคิดของวิศวกรไฟฟ้าที่ต้องการการถ่ายเทความร้อนสูงสุด แต่การพิมพ์ น้อยกว่า การวาง (บ่อยครั้ง 60-70% ครอบคลุมแทน 100%) เป็นผลให้ มากขึ้น การสัมผัส metal-to-metal เพราะมันกำจัดช่องว่าง

เศรษฐศาสตร์ของการแก้ไข

มักจะมีการตอบโต้เรื่องค่าใช้จ่าย stencil ที่ถูกตัดด้วยเลเซอร์มาตรฐาน อาจมีค่าใช้จ่าย $150 ถึง $200 สำหรับ stencil ขั้นตอนหลายระดับที่เคลือบด้วยนาโน อาจมีค่าใช้จ่าย $350 ถึง $450 ทีมงานจัดซื้อจะดูที่รายการนี้และถามว่าควร “ทำให้ใช้งานได้” ด้วยตัวเลือกมาตรฐานหรือไม่

เปรียบเทียบกับต้นทุนของทางเลือกอื่น

การแก้ไขบอร์ด BGA ขนาด 0.4mm ที่เชื่อมต่อกันเป็นรอยต่อไม่ใช่แค่ยาก; บ่อยครั้งเป็นไปไม่ได้โดยไม่ทำลายบอร์ดหรือส่วนประกอบที่อยู่ติดกัน การเปลี่ยนสายเชื่อมต่อที่ถูกตัดบนหน่วยที่เสร็จสมบูรณ์มีค่าใช้จ่ายสิบเท่าของชิ้นส่วนดิบ ค่าใช้จ่าย NRE (Non-Recurring Engineering) ของ stencil ที่เหมาะสมเป็นค่าใช้จ่ายครั้งเดียว ค่าใช้จ่ายในการเก็บซ่อม solder บนบอร์ดพันละหลัง เพราะพยายามฝ่าฟันกฏฟิสิกส์ เป็นเรื่องที่เกิดซ้ำเจ็บปวด และสามารถป้องกันได้ง่าย เราปรับเปลี่ยนข้อมูลเพราะว่าความถูกต้องในครั้งแรกมีค่าใช้จ่ายต่ำกว่าการแก้ไขในภายหลังเสมอ