แรงกดดันในการจับข้อผิดพลาดในการผลิตก่อนส่งมอบเป็นเรื่องที่ไม่สามารถต่อรองได้ ข้อผิดพลาดเดียวที่รอดพ้นในระบบสำคัญอาจมีค่าใช้จ่ายมากกว่าการทดสอบที่จับมันได้อย่างมาก ความเป็นจริงนี้เป็นแรงผลักดันให้ทีมวิศวกรรมหลายแห่งหันมาใช้การทดสอบในวงจร (ICT) เป็นมาตรฐาน ซึ่งเป็นวิธีที่ได้รับการยอมรับว่ามีเกณฑ์ครอบคลุมมากที่สุด การทำ ICT ครบถ้วนให้การเข้าถึงเกือบทุกจุดบนบอร์ด เพื่อความสามารถในการตรวจจับข้อผิดพลาดในระดับสูงสุด สำหรับการผลิตในปริมาณมาก การลงทุนนี้มีเหตุผล ต้นทุนคงที่ของวิศวกรรมแผ่นเฟรมและอุปกรณ์ทดสอบจะถูกหารออกไปในหน่วยจำนวนมาก ทำให้ภาระต่อต่อหน่วยลดลงจนเกือบไม่รู้สึก

แต่เศรษฐศาสตร์เปลี่ยนเมื่อปริมาณการผลิตลดลง สำหรับการผลิตไม่เกินสองร้อยหน่วย ข้อได้เปรียบของ ICT กลับกลายเป็นข้อเสีย คุณสมบัติที่ต้องการสำหรับแต่ละดีไซน์บอร์ดมีต้นทุนวิศวกรรมแบบคงที่ที่สูง ซึ่งไม่สามารถขยายได้ เวลานำทางยืดออกเนื่องจากต้องออกแบบ สร้าง และดีบักเฟรม การทำซ้ำการออกแบบ ซึ่งเป็นเรื่องปกติในนวัตกรรมผลิตภัณฑ์ใหม่ ทำให้เฟรมล้มเหลวโดยสิ้นเชิงและต้องเริ่มต้นใหม่ เราได้เห็นชั้วนี้หลายร้อยโครงการแล้ว ในการผลิตน้อยกว่าหรือเท่ากับ 200 ถึง 300 หน่วย การทำ ICT แบบเต็มรูปแบบแทบไม่คุ้มค่า

ทางเลือกคือไม่ละทิ้งการทดสอบเข้มงวด แต่เปลี่ยนจากโมเดลที่ขึ้นอยู่กับเฟรมเป็นกลยุทธ์ที่เบาขึ้นและรวดเร็วขึ้นที่สร้างบนสแกนบาร์เรนดาร์ด การทดสอบแบบไม่มีเวกเตอร์ และการทดสอบที่เน้นฟังก์ชัน การผสมผสานนี้ให้การครอบคลุมข้อผิดพลาดในระดับเท่าเทียมกัน ขจัดข้อจำกัดของเฟรม และให้วงจรดีบักที่รวดเร็วขึ้นเมื่อพบข้อผิดพลาด การเปลี่ยนแปลงนี้ไม่ใช่แนวความคิดอุดมคติ แต่เป็นการตอบสนองเชิงปฏิบัติที่ต่อกรกับแรงเสียดทานเชิงคณิตศาสตร์และกลไกที่ ICT สร้างขึ้นในกระบวนการผลิตแบบฉับไวและปริมาณน้อย

ความเชื่อสมมติใน ICT และจุดที่มันล้มเหลว

การทดสอบในวงจรกลายเป็นมาตรฐานอุตสาหกรรมในยุคที่มีการออกแบบที่มีปริมาณสูงและเสถียร โมเดลนี้ง่าย: ลงทุนอย่างมากล่วงหน้าในเฟรมทดสอบแบบกำหนดเองและเครื่องทดสอบอัจฉริยะ จากนั้นก็ใช้การลงทุนนั้นในหน่วยที่มีความเหมือนกันหลายหมื่นหน่วย ด้วยเวลาทดสอบต่อหน่วยที่วัดได้ในวินาที ต้นทุนต่อบอร์ดก็แทบเป็นศูนย์หลังจากต้นทุนคงที่ถูกครอบคลุมแล้ว สำหรับผู้ผลิตอิเล็กทรอนิกส์ผู้ผลิตที่มีการผลิตสินค้าเดียวกัน 50,000 หน่วย จะเป็นไปตามคณิตศาสตร์ที่ไม่สามารถโต้แย้งได้

โมเดลการผลิตนี้แตกแถว การผลิตอิเล็กทรอนิกส์สมัยใหม่ผลิตให้กับตลาดที่มีความหลากหลายสูงและปริมาณต่ำ ลูปอายุผลิตภัณฑ์สั้นลง การออกแบบซ้ำซ้อนบ่อยขึ้น และการปรับแต่งกลายเป็นข้อได้เปรียบเชิงการแข่งขัน บริษัทอาจผลิต 150 หน่วยของรุ่นเดียว แล้วปรับเปลี่ยนการออกแบบ แล้วผลิต 200 หน่วยของรุ่นถัดไป ความเชื่อสมมติที่ว่าเฟรมเดียวจะสามารถทดสอบบอร์ดที่เหมือนกันได้เป็นพันๆ ชิ้นไม่ได้ใช้แล้ว ต้นทุนคงที่ที่เคยเล็กน้อยในปริมาณสูงกลายเป็นต้นทุนที่น่ารำคาญเมื่อกระจายออกไปในกลุ่มไม่กี่ร้อยหน่วย

โมเดลล้มเหลวเมื่อต้นทุนรวมของโครงสร้าง ICT เกินกว่าต้นทุนที่ปรับความเสี่ยงได้ของกลยุทธ์ทางเลือก Threshold นี้ไม่ได้เป็นเรื่องสุ่ม มันเป็นฟังก์ชันของต้นทุนเฟรม เวลาและความสามารถในการครอบคลุมที่สามารถทำได้ผ่านวิธีการไร้เฟรม สำหรับการออกแบบบอร์ดส่วนใหญ่ Threshold นี้อยู่ระหว่าง 200 ถึง 300 หน่วย

กับดักต้นทุนคงที่ของการทดสอบในวงจร

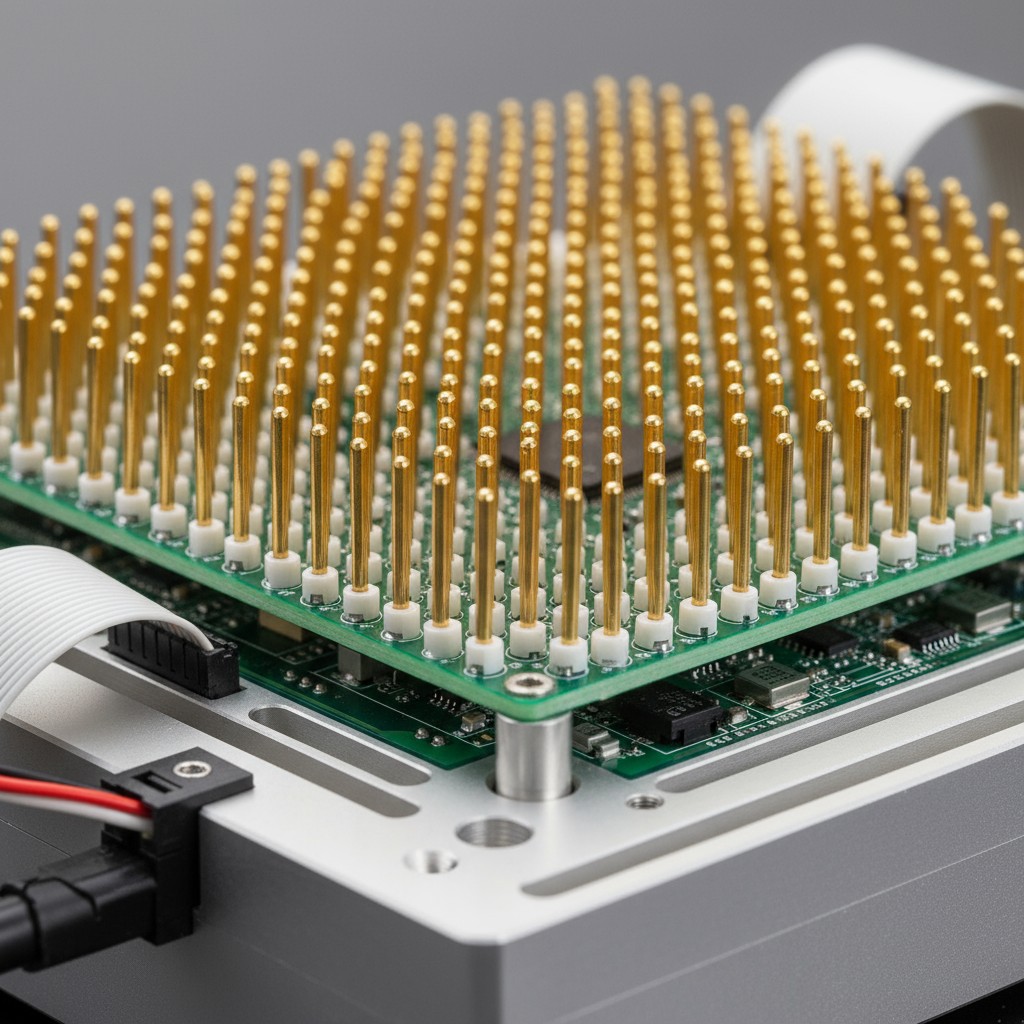

แม้ว่เฟรมจะเป็นต้นทุนที่เห็นได้ชัดเจนที่สุดของ ICT ต้นทุนที่แท้จริงนั้นครอบคลุมมากกว่าเฟรม เฟรม ICT ที่กำหนดเองไม่ใช่การซื้อแบบสำเร็จรูป มันเป็นงานวิศวกรรมที่ออกแบบมาเฉพาะสำหรับการวางผังบอร์ดนั้น การออกแบบต้องแปลเน็ตลิสต์และตำแหน่งชิ้นส่วนของบอร์ดให้อยู่ในโครงสร้างกลไกที่ติดตั้ง probes แบบสปริง มีความแม่นยำระดับมิลลิเมตรย่อย เฟรมต้องคำนึงถึงความคลาดเคลื่อนของชิ้นส่วน การโก่งตัวของบอร์ด และการสึกหรอของ probes จากนั้นจึงต้องได้รับการรับรองและดีบัก—กระบวนการที่บ่อยครั้งเผยปัญหาที่ไม่คาดคิดเกี่ยวกับการเข้าถึง probes หรือความเสถียรของสัญญาณ

ต้นทุนวิศวกรรมเฟรมและเวลานำ

ต้นทุนวิศวกรรมสำหรับอุปกรณ์ติดตั้งที่มีความซับซ้อนปานกลางมักอยู่ระหว่าง $8,000 ถึง $15,000 แผ่นบอร์ดที่มีความหนาแน่นสูงและองค์ประกอบแบบละเอียด หรือจุดทดสอบที่เข้าถึงได้จำกัดอาจทำให้ตัวเลขนั้นสูงขึ้นไปถึง $25,000 หรือมากกว่า นี่เป็นเพียงต้นทุนของอินเทอร์เฟซกลไกและไฟฟ้าที่กำหนดเองเพื่อเชื่อมต่อบอร์ดกับอุปกรณ์ ICT ซึ่งแยกจากค่าใช้จ่ายด้านทุนของเครื่องทดสอบเอง

เวลารอคอยก็มีผลเช่นกัน ตั้งแต่ช่วงเวลาที่ออกแบบบอร์ดเสร็จสิ้น การออกแบบและการผลิตอุปกรณ์ติดตั้งมักใช้เวลาสองถึงสี่สัปดาห์ โดยเพิ่มเป็นหกสัปดาห์สำหรับการออกแบบที่ซับซ้อน ระหว่างเวลานี้ การผลิตหยุดชะงัก บอร์ดอาจประกอบสมบูรณ์แล้ว แต่ไม่สามารถทดสอบได้ พวกมันนั่งอยู่ในสต็อก คอยรอ หากการออกแบบเปลี่ยนแปลงในช่วงเวลานี้ ซึ่งเป็นเรื่องปกติในการแนะนำผลิตภัณฑ์ใหม่ อุปกรณ์ติดตั้งจะต้องได้รับการปรับปรุงใหม่หรือทิ้ง รถจะถูกรีเซ็ตใหม่

คณิตศาสตร์จุดคุ้มทุนสำหรับการผลิตจำนวนต่ำ

กับดักทางเศรษฐกิจจะชัดเจนเมื่อค่าของอุปกรณ์ติดตั้งถูกแบ่งด้วยจำนวนยูนิต อุปกรณ์ติดตั้ง $12,000 สำหรับการผลิต 100 ยูนิต จะเพิ่มภาระ $120 ต่อแต่ละบอร์ด สำหรับบอร์ดที่มีบิลวัสดุ $500 นั่นคือภาระการทดสอบร้อยละ 24 ถึงแม้ว่ากระบวนการ ICT จะรวดเร็ว ประสิทธิภาพทางเศรษฐกิจยังต่ำ อุปกรณ์ติดตั้งเดียวกันนี้ที่นำไปใช้กับ 500 ยูนิต ลดต้นทุนต่อหน่วยเหลือ $24 ซึ่งเป็นการบรรเทาภาระร้อยละ 5 ที่ยอมรับได้มากกว่า ความแตกต่างนี้เป็นเพียงผลของปริมาณ

จุดคุ้มทุนคือเมื่อค่ารวมของ ICT — รวมถึงวิศวกรรม การตั้งค่า และต้นทุนโอกาสของเวลาในการรอคอย — เท่ากับต้นทุนของทางเลือกที่ไม่มีอุปกรณ์ติดตั้ง สำหรับกลยุทธ์ที่ผสมผสานการสแกนพื้นที่ขอบ ข้อมูลแบบไม่ใช้เวกเตอร์ และการทดสอบเชิงฟังก์ชันแบบ Lean โครงสร้างพื้นฐานมีต้นทุนต่ำลงอย่างมาก การสแกนพื้นที่ขอบไม่ต้องการอุปกรณ์ติดตั้ง และการทดสอบโดยไม่ใช้เวกเตอร์ใช้เซ็นเซอร์ที่สามารถนำกลับมาใช้ใหม่ได้ ซึ่งทำงานโดยไม่ต้องสัมผัสทางกล วิธีการทดสอบเชิงฟังก์ชันใดๆ มักเป็นแบบพื้นฐานและทั่วไป ไม่ใช่สิ่งประดิษฐ์บนบอร์ดที่ต้องใช้เวลานานในการวิศวกรรม

ในปริมาณการผลิตต่ำกว่า 200 ยูนิต เศรษฐศาสตร์ของ ICT ล้มเหลว ในระดับต่ำกว่า 300 ยูนิต ข้อดีเป็นแค่กลายๆ ขึ้นอยู่กับความซับซ้อนของบอร์ด เท่านั้น แต่เมื่อถึงระดับ 300 ยูนิตขึ้นไป สำหรับแบบที่เสถียรและไม่ซ้ำกัน ICT จะเริ่มมีเหตุผลทางเศรษฐกิจอีกครั้ง

ความหมายที่แท้จริงของ Boundary Scan และการทดสอบแบบ Vectorless

ทางเลือกแทนการทดสอบแบบ fixture ไม่ใช่การลดความเข้มงวด แต่เป็นการเปลี่ยนไปใช้วิธีที่ใช้โครงสร้างการออกแบบที่มีอยู่และการวัดโดยไม่สัมผัส เครื่องมือนี้ได้รับการพัฒนาเพื่อตอบสนองแนวโน้มเดียวกันที่ทำลาย ICT: ความหนาแน่นของบอร์ดเพิ่มขึ้นและการเข้าถึงจุดทดสอบทางกายภาพลดลง

การสแกนพื้นที่ขอบ ซึ่งเป็นมาตรฐานใน IEEE 1149.1 (ที่รู้จักกันโดยทั่วไปในชื่อ JTAG) ฝังตรรก์ทดสอบไว้ในวงจรรวมของบอร์ด ไอเท็มที่เข้ากันได้รวมถึงชุดของเซลล์ที่อยู่ในแต่ละจุดเข้าออก ระหว่างการทดสอบ อินเทอร์เฟซสี่สายง่ายๆ เลื่อนรูปแบบเข้าไปในเซลล์เหล่านี้ ควบคุมสภาวะตรรกะบนเครือข่ายของบอร์ด สภาวะที่ได้ถูกจับภาพและเปลี่ยนที่สำหรับวิเคราะห์ ช่วยให้เทสต์เตอร์ควบคุมและสังเกตสัญญาณที่จุดต่อสัญญาณโดยไม่ต้องสัมผัสทางกายภาพ วิธีนี้ไม่ก่อให้เกิดผลเสียและมีประสิทธิภาพสูงในการตรวจจับการเชื่อมต่อผิด สายเปิด และข้อผิดพลาดติดอยู่ระหว่างอุปกรณ์ที่เข้ากันได้

การทดสอบแบบไม่ใช้เวกเตอร์เสริมด้วยการวัดด้วยความจุและอินดักทีฟเพื่อค้นหาข้อผิดพลาดทั่วทั้งบอร์ด แผงเซ็นเซอร์ที่วางใกล้บอร์ดวัดลักษณะแม่เหล็กไฟฟ้าขององค์ประกอบและสายไฟ การเชื่อมต่อผิดสร้างการ coupling ด้วยความจุซึ่งสามารถวัดได้; สายไฟเปิดแสดงความเปลี่ยนแปลงของความต้านทานที่เป็นลักษณะ วิธีนี้เร็ว ไม่ต้องสัมผัส และสามารถสรุปว่ามีส่วนประกอบ, โพลาริตี, และค่าประมาณ ซึ่งช่วยตรวจจับข้อผิดพลาดที่สำคัญในการผลิต เช่น การขาดส่วนประกอบ, ไดโอดที่คืนค่าในทิศทางผิด, หรือสายไฟเชื่อมต่อกัน

เปรียบเทียบความครอบคลุม: ตัวเลขเบื้องหลังการเสียสละ

ข้อโต้แย้งหลักในการละเว้น ICT คือการครอบคลุม แม้ว่า ICT สามารถเข้าถึงจุดต่างๆ บนบอร์ดได้ทุกจุดด้วยจุดทดสอบเพียงพอ คำอ้างว่าทางเลือกด้อยกว่านั้นไม่ครบถ้วน คำถามที่แท้จริงคือพวกมันสามารถครอบคลุมข้อผิดพลาดที่เกิดขึ้นจริงหรือไม่ และถ้าการทดสอบเชิงฟังก์ชันแบบเน้นๆ สามารถปิดช่องว่างที่เหลืออยู่ได้หรือไม่

สิ่งที่ Boundary Scan ครอบคลุม

การครอบคลุมการตรวจสอบขอบเขตขึ้นอยู่กับจำนวนส่วนประกอบบนแผ่นบอร์ดที่ปฏิบัติตามมาตรฐาน JTAG สำหรับบอร์ดที่มีลักษณะโดดเด่นด้านดิจิทัล—ไมโครโปรเซสเซอร์, FPGA, หน่วยความจำ—การครอบคลุมจะกว้างไกล ชุดการสแกนสามารถทดสอบการเชื่อมต่อระหว่างอุปกรณ์เหล่านี้โดยอัตราการตรวจจับข้อผิดพลาดเกิน 95 เปอร์เซ็นต์สำหรับไฟล์ชอร์ต, เปิด, และข้อผิดพลาด stuck-at แผ่นบอร์ดที่มีส่วนประกอบ 80 เปอร์เซ็นต์ที่ปฏิบัติตามจะได้เน็ตครอบคลุมประมาณ 70 ถึง 85 เปอร์เซ็นต์ ส่วนอนาล็อก, ส่วนประกอบแบบแยกส่วน, และชิ้นส่วนเสื่อมสภาพจะมองไม่เห็นด้วยวิธีนี้ อย่างไรก็ตาม สำหรับการออกแบบที่เน้นดิจิทัลเป็นหลัก การสแกนขอบเขียวเท่านั้นให้การครอบคลุมที่เทียบเท่ากับ ICT สำหรับชั้นเชื่อมต่อ ซึ่งเป็นที่ที่เกิดข้อผิดพลาดในการประกอบส่วนใหญ่

สิ่งที่การทดสอบไรเวกเตอร์เพิ่มเข้ามา

การทดสอบแบบไม่มีเวกเตอร์เติมเต็มช่องว่างที่เหลือโดย boundary scan โดยเฉพาะสำหรับส่วนประกอบแบบพาสซีฟและข้อบกพร่องของการประกอบโดยรวม การวัดค่าคาปาซิทีฟสามารถตรวจจับตัวต้านทานที่ขาดหาย ค่าแรงดันของตัวเก็บประจุที่ผิดพลาด และไดโอดที่ขวางทาง ถึงแม้ว่าจะมีความแม่นยำต่ำกว่าการวัดโดยตรงของ ICT แต่มันก็เป็นหน้าจอที่มีประสิทธิภาพสำหรับข้อผิดพลาดที่พบบ่อยที่สุด: ส่วนประกอบผิด ส่วนประกอบขาด หรือความไม่ตรงกันอย่างรุนแรง การนี้จะเพิ่มครอบคลุมข้อผิดพลาดอีก 10 ถึง 20 เปอร์เซ็นต์ รวมเป็นชั้นการตรวจสอบแบบไม่ต้องสัมผัสสำหรับชิ้นส่วนที่ boundary scan ไม่สามารถมองเห็นได้

ช่องว่างที่เหลือและวิธีที่การทดสอบเชิงฟังก์ชันแบบ Lean ปิดช่องว่างนี้

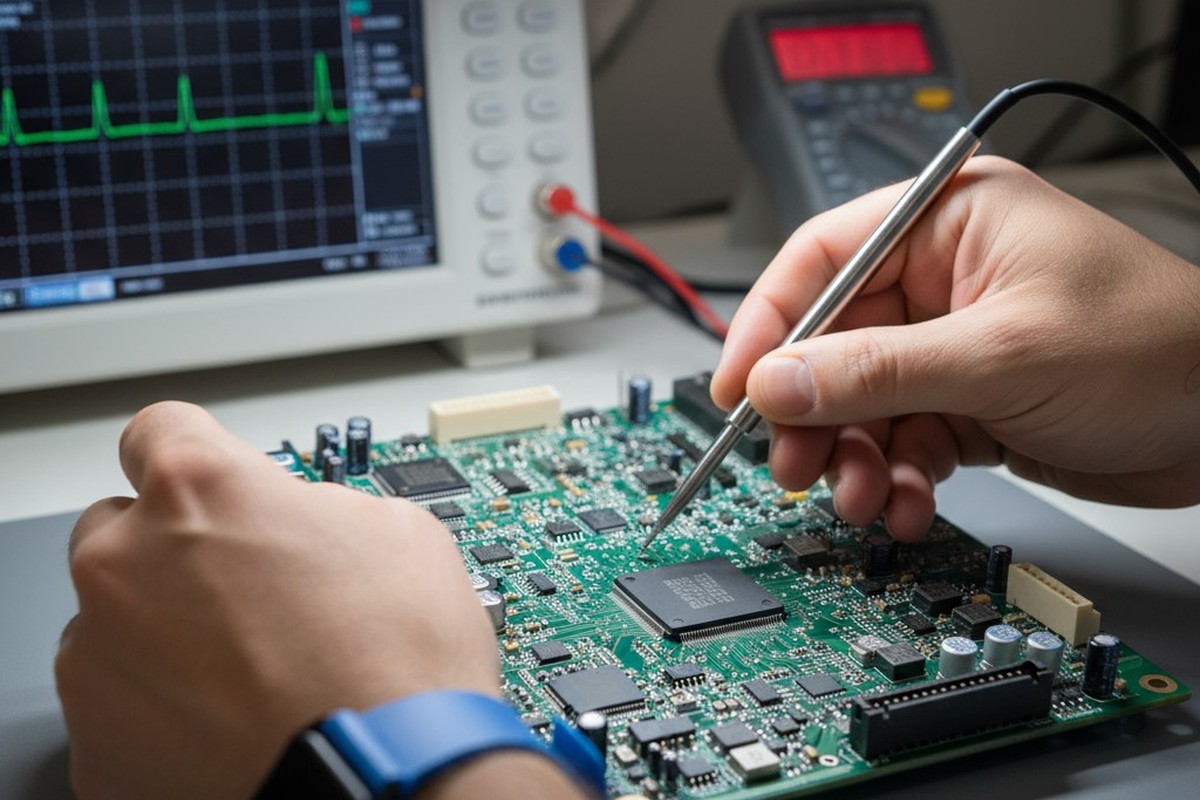

การผสมผสานของการสแกนพื้นที่ขอบและการทดสอบโดยไม่ใช้เวกเตอร์ยังคงทิ้งช่องว่างไว้ในการตรวจสอบเชิงฟังก์ชันและประสิทธิภาพอนาลอักส์ ส่วนประกอบอาจจะมีอยู่และเชื่อมต่อถูกต้อง แต่ยังคงทำงานผิดพลาดเกินสเปคได้ เช่น จ่ายไฟแต่มีรอยคลื่นมากเกินไป ที่นี่คือหน้าที่ของการทดสอบวงจรเชิงฟังก์ชันแบบ Lean ซึ่งไม่ใช่การตั้งค่า ICT ทั้งหมด มันยืนยันว่าบอร์ดทำงานตามที่ออกแบบไว้ภายใต้เงื่อนไขจริง ใช้จ่ายพลังงาน กระตุ้นสัญญาณเข้า และวัดสัญญาณออก สำหรับตัวควบคุมมอเตอร์ อาจตรวจสอบการสร้างสัญญาณ PWM; สำหรับบอร์ดสื่อสาร อาจตรวจสอบการส่งข้อมูลโดยไม่มีข้อผิดพลาด การทดสอบเชิงฟังก์ชันเป็นการเสริมการทดสอบด้านโครงสร้าง ซึ่งช่วยจับข้อผิดพลาดที่วิธีอื่นมองไม่เห็น

โดยรวม วิธีการทั้งสามนี้จะได้ประมาณ 85 ถึง 95 เปอร์เซ็นต์ของการครอบคลุมข้อผิดพลาด นี่ไม่ใช่ 100 เปอร์เซ็นต์ แต่ก็ไม่ใช่ ICT ในทางปฏิบัติ เนื่องจากข้อจำกัดของจุดทดสอบและการสึกหรอของหัวแร้ง ค่าการครอบคลุมของ ICT ในโลกแห่งความเป็นจริงมักจะต่ำกว่าค่าสูงสุดทางทฤษฎี ความแตกต่างในการครอบคลุมนี้มีค่าน้อยกว่าค่าปรับในด้านต้นทุนและเวลานำเข้า

ข้อได้เปรียบของวงจรดีบัก

การครอบคลุมการทดสอบเป็นเพียงครึ่งหนึ่งของสมการคุณค่า อีกครึ่งหนึ่งคือความเร็วและความแม่นยำในการแยกแยะข้อผิดพลาด การทดสอบที่ตรวจพบข้อผิดพลาดแต่ให้การวินิจฉัยที่คลุมเครือ จะเพิ่มเวลาและต้นทุนที่ใช้ในการหาสาเหตุหลัก

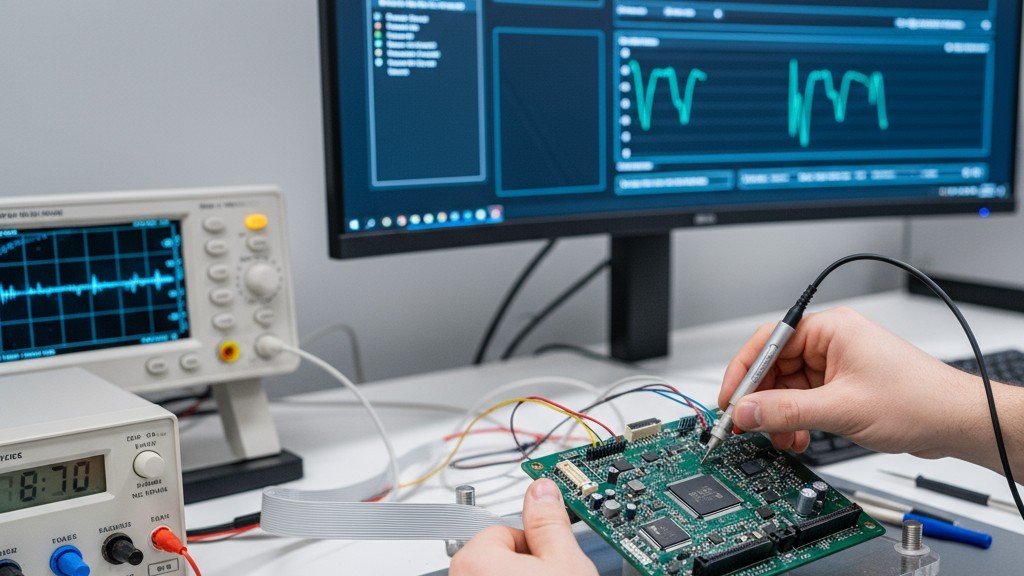

ในขณะที่ ICT ดีในการเตือนข้อผิดพลาด การวินิจฉัยของมันอาจเป็นได้อย่างน่าหงุดหงิด ขึ้นอยู่กับเทคนิค คุณอาจรายงานว่าสายต่อที่ 47 เป็นสายเชื่อมต่อผิดหรือช็อตไปยังพื้นดิน แต่ไม่อธิบายว่าทำไมและที่ไหน ช่างเทคนิคต้องติดตามไช้ schematic ค้นหาเครือข่าย แล้วตรวจสอบทางสายตา—เป็นกระบวนการที่อาจใช้เวลาหลายชั่วโมงบนบอร์ดหลายชั้นที่ซับซ้อน

การวินิจฉัยการสแกนขอบเขตมีความแตกต่างอย่างพื้นฐาน เนื่องจากสายการสแกนฝังอยู่ในส่วนประกอบ โหมดทดสอบจะแยกความผิดออกเป็นพินและอุปกรณ์เฉพาะ จุดเชื่อมต่อระหว่างสองเครือข่ายที่สั้นจะถูกระบุโดยพินของอุปกรณ์ที่เกี่ยวข้อง การค้นหาเรื่องเปิดจะถูกตรวจจับระหว่างคู่ไดรเวอร์และรีซีฟเวอร์เฉพาะ ผลลัพธ์ของการวินิจฉัยไม่ใช่รหัสความผิด มันคือแผนที่ ความแม่นยำนี้หมายความว่าความผิดที่ใช้เวลาหนึ่งชั่วโมงในการแก้ไขด้วยข้อมูล ICT สามารถแก้ไขได้ในเวลา 10 ถึง 20 นาทีด้วยการสแกนขอบเขต สำหรับการทดสอบ 100 หน่วยที่มีอัตราความผิดปกติทั่วไป เวลาที่ประหยัดได้จากการดีบักสะสมอาจเกิน 10 ชั่วโมง

เวลาในการดำเนินการและความยืดหยุ่น: มูลค่าที่ซ่อนอยู่

ข้อโต้แย้งทางเศรษฐกิจต่อต้าน ICT สำหรับปริมาณต่ำมีความน่าดึงดูดใจ แต่ค่าปรับเวลาในการดำเนินการก็สำคัญเช่นกัน กระบวนการวิศวกรรมอุปกรณ์ที่ใช้เวลาสองถึงสี่สัปดาห์บังคับให้เกิดความล่าช้าระหว่างการหยุดชะงักการออกแบบและการพร้อมทดสอบ สำหรับการแนะนำผลิตภัณฑ์ใหม่ ซึ่งเวลาสู่ตลาดเป็นสิ่งสำคัญ ความล่าช้านี้มักเป็นสิ่งที่ยอมรับไม่ได้

การสแกนขอบเขตและการทดสอบโดยไม่ใช้เวกเตอร์ช่วยกำจัดความรอคอยนี้ การตั้งค่าการทดสอบสามารถทำในชั่วโมงหรือวัน ไม่ใช่สัปดาห์ ทำให้บอร์ดสามารถเคลื่อนย้ายจากการประกอบไปยังการทดสอบและการจัดส่งในกระบวนการต่อเนื่อง ความยืดหยุ่นนี้มีความสำคัญเมื่อการออกแบบมีการปรับปรุง การรันต้นแบบในช่วงต้นอาจเปิดเผยปัญหาที่ต้องเปลี่ยนแปลงการจัดวางบอร์ด ด้วย ICT การแก้ไขแต่ละครั้งต้องการชุดกระดานใหม่หรือปรับปรุง ซึ่งเพิ่มต้นทุนและเวลาในการดำเนินการอีกครั้ง รูปแบบการทดสอบด้วยการสแกนขอบเขตที่สร้างจากเน็ตลิสต์อัปเดตโดยอัตโนมัติเมื่อมีการเปลี่ยนแปลงการออกแบบ ซึ่งสร้างกลยุทธ์การทดสอบที่สนับสนุนการพัฒนาซ้ำๆ แทนที่จะลงโทษมัน

เมื่อไหร่ที่ยังคงเลือก ICT

แต่กรณีต่อต้าน ICT สำหรับปริมาณต่ำไม่ได้เป็นสิ่งที่สมบูรณ์แบบ การออกแบบและบริบทการผลิตบางอย่างยังสนับสนุนการลงทุนนี้อยู่

บอร์ดที่มีส่วนประกอบอะนาล็อกความหนาแน่นสูงหรือ RF เป็นตัวอย่างที่ไม่เหมาะสมสำหรับกลยุทธ์ไร้กระดานอย่างบริสุทธิ์ ส่วนประกอบอะนาล็อกขาดตรรกะการสแกนขอบเขต และคุณสมบัติการแสดงประสิทธิภาพสำคัญ เช่น การเพิ่มหรือเสียงเฟส ไม่สามารถตรวจสอบได้ในเชิงโครงสร้าง หากวงจรอะนาล็อกหรือ RF คิดเป็นมากกว่า 40 เปอร์เซ็นต์ของฟังก์ชันการทำงานของบอร์ด กรณีสำหรับ ICT ก็จะเพิ่มขึ้นอย่างมีนัยสำคัญ

อุตสาหกรรมที่เน้นความสอดคล้องตามกฎระเบียบ เช่น การแพทย์, อวกาศ, และยานยนต์ มักดำเนินการภายใต้กฎระเบียบที่บังคับให้ตรวจสอบหรือเข้าถึงจุดระดับอุปกรณ์ในวงจร หากมาตรฐานที่บังคับใช้ต้องการการทดสอบในวงจรหรือการเข้าถึงในระดับโหนดที่เทียบเท่า กลยุทธ์ทางเลือกอาจไม่เพียงพอ ที่นี่ ต้นทุนของ ICT เป็นค่าใช้จ่ายที่หลีกเลี่ยงไม่ได้เพื่อการเข้าถึงตลาด

สุดท้าย เส้นทางที่ชัดเจนและมุ่งมั่นสู่การผลิตในปริมาณสูงเปลี่ยนแปลงคณิตศาสตร์ หากคาดว่าการผลิตช่วงแรก 150 หน่วยจะขยายเป็น 1,000 หน่วยภายในหกเดือน ค่าใช้จ่ายสำหรับชุดอุปกรณ์จะถูกหักกลบกับปริมาณที่คาดการณ์ไว้ทั้งหมด ซึ่งต้องการความมั่นใจสูงในคำทำนายและการออกแบบที่เสถียร แต่ก็สามารถทำให้การลงทุนล่วงหน้าคุ้มค่า

สร้างกลยุทธ์การทดสอบทางเลือก

การแทนที่ ICT ไม่ใช่สิ่งที่ง่ายดาย มันคือการปรับเปลี่ยนสถาปัตยกรรมการทดสอบให้เป็นกลยุทธ์ระดับชั้น ซึ่งแต่ละชั้นจะจับข้อผิดพลาดที่ชั้นอื่นอาจมองข้าม

กระบวนการควรดำเนินตามลำดับ ชั้นแรกคือการสแกนขอบเขต ซึ่งดำเนินการอย่างรวดเร็วบนอุปกรณ์ที่เป็นไปตามข้อกำหนดทั้งหมดเพื่อจับข้อผิดพลาดของการเชื่อมต่อบนส่วนดิจิตัลของบอร์ด บอร์ดที่ล้มเหลวจะถูกรายงานสำหรับการปรับปรุงทันที เพื่อป้องกันข้อผิดพลาดร้ายแรงเมื่อเปิดใช้งานจ่ายไฟ ขั้นที่สองคือการทดสอบโดยไม่ใช้เวกเตอร์ ซึ่งครอบคลุมบอร์ดทั้งหมดเพื่อค้นหาชิ้นส่วนพาสซีฟที่ขาดหรือผิดพลาด การเชื่อมต่อสั้นเกิน ความผิดพลาดใน Polarity ซึ่งเป็นส่วนที่มองไม่เห็นในสายการสแกน

ชั้นที่สามและสุดท้ายคือการทดสอบเชิงฟังก์ชันเป็นจุดสนใจ เมื่อความผิดปกติในโครงสร้างถูกกรองออกแล้ว บอร์ดจะเปิดใช้งานเพื่อรับรองความถูกต้องของฟังก์ชันสำคัญภายใต้สภาพการใช้งานจริง ขอบเขตถูกปรับให้เหมาะสมกับวัตถุประสงค์ของบอร์ด—เช่น การตรวจสอบความแม่นยำของ ADC บนบอร์ดเก็บข้อมูลหรือการควบคุมโหลดบนแหล่งจ่ายไฟ ลำดับนี้ช่วยให้ตรวจจับความผิดพลาดร้ายแรงได้ตั้งแต่เนิ่นๆ และไม่ทำลายซึ่งช่วยลดเวลาการดีบักในข้อผิดพลาดฟังก์ชันที่ซับซ้อนกว่า

สำหรับบอร์ดที่มีความซับซ้อนแบบผสม—for instance, ศูนย์กลางดิจิตอลที่หนาแน่นล้อมรอบด้วยการปรับสัญญาณอะนาล็อก—กลยุทธ์ผสมอาจเป็นทางเลือกที่ดีที่สุด ชุดอุปกรณ์ ICT แบบบางสามารถออกแบบให้ตรวจจับเฉพาะส่วนอะนาล็อกที่สำคัญเท่านั้น ทำให้ปล่อยให้ส่วนดิจิตัลเป็นการสแกนขอบเขต ยุทธศาสตร์เชิงเศรษฐกิจของชุดอุปกรณ์บางนี้เป็นที่น่าพอใจ ลดต้นทุนและระยะเวลานำเข้า ในขณะเดียวกันก็ให้การครอบคลุมที่จำเป็นสำหรับการออกแบบทั้งหมด