बोर्ड भेजने से पहले विनिर्माण दोष पकड़ने का दबाव अस्वीकार्य है। एक महत्वपूर्ण सिस्टम में छुट गई एक एकल खामी उस परीक्षण से कहीं अधिक लागत कर सकती है जो उसे पकड़ लेती। यह वास्तविकता कई इंजीनियरिंग टीमों को इन-सर्किट टेस्टिंग (ICT) की ओर ले जाती है, जो कवरेज के लिए लंबे समय से सोची जाने वाली स्वर्ण मानक विधि है। पूर्ण ICT बोर्ड पर लगभग प्रत्येक नोड तक व्यापक पहुंच प्रदान करता है, जो कि सैद्धांतिक अधिकतम सीमा से करीब दोष पहचान दर का वादा करता है। उच्च मात्रा उत्पादन के लिए, निवेश समझ में आता है; फिक्स्चर इंजीनियरिंग और परीक्षण उपकरण के स्थिर लागतों का अमोर्टाइजेशन हजारों इकाइयों में होता है, जिससे प्रति इकाई बोझ न्यूनतम स्तर पर आ जाता है।

लेकिन उत्पादन मात्रा घटने पर अर्थशास्त्र पलट जाता है। सौ से कम इकाइयों पर चलने वाले उत्पादन के लिए, ICT की शक्तियां ही जवाबदेह बन जाती हैं। प्रत्येक बोर्ड डिज़ाइन के लिए आवश्यक कस्टम फिक्स्चर एक तीव्र, स्थिर इंजीनियरिंग लागत वहन करता है जो स्केल नहीं करता। लीड टाइम बढ़ते हैं क्योंकि फिक्स्चर डिज़ाइन, निर्मित और डिबग किए जाते हैं। डिज़ाइन पुनरावृत्तियों, जो नए उत्पाद की शुरुआत में सामान्य हैं, पूरी तरह से फिक्स्चर को निरस्त कर देती हैं, cycle को शुरू करना मजबूर कर देती हैं। Bester PCBA पर, हमने इस गणित को सैकड़ों प्रोजेक्ट्स में खेलते देखा है। 200 से 300 इकाइयों से कम रन के लिए, पूर्ण ICT शायद ही अपने बहुमूल्य साबित होता है।

वैकल्पिक उपाय कठोर परीक्षण से मना करने का नहीं है, बल्कि फिक्स्चर-निर्भर मॉडल को एक अधिक फुर्तीले, तेज़ रणनीति से बदलने का है, जो सीमा स्कैन, वेक्टर रहित परीक्षण, और केंद्रीकृत कार्यात्मक परीक्षण पर आधारित है। यह संयोजन तुलनीय दोष कवरेज प्रदान करता है, फिक्स्चर बाधा को समाप्त करता है, और जब दोष पाए जाते हैं तो तेज़ डिबग लूप प्रदान करता है। यह परिवर्तन वैचारिक नहीं है; यह गणितीय और यांत्रिक घर्षण का व्यावहारिक जवाब है जो ICT निम्न मात्रा, चुस्त उत्पादन पर डालता है।

आईसीटी अनुमThought और यह कहां टूटता है

इन-सर्किट परीक्षण उच्च मात्रा और स्थिर डिज़ाइनों के युग में उद्योग मानक बन गया। मॉडल सरल था: विशेष फिक्स्चर और उन्नत परीक्षक में भारी निवेश करें, फिर उस निवेश का उपयोग कर लाखों समान इकाइयों पर लाभ लें। प्रति इकाई परीक्षण समय सेकंड में मापा जाता है, इसलिए स्थिर लागतों को अवशोषित करने के बाद बोर्ड का अतिरिक्त लागत प्रभावी रूप से शून्य हो जाती है। एक उपभोक्ता इलेक्ट्रॉनिक्स निर्माता जो 50,000 इकाइयों का उत्पादन करता है, वह गणित को अडिग मानता है।

वह उत्पादन मॉडल टूट गया है। आधुनिक इलेक्ट्रॉनिक्स निर्माण अधिकतर बाजारों को उच्च मिलावट और कम मात्रा में सेवा प्रदान करता है। उत्पाद जीवनचक्र छोटे हैं, डिज़ाइन पुनरावृत्तियां अधिक हैं, और अनुकूलन एक प्रतिस्पर्धात्मक लाभ है। एक कंपनी हो सकता है कि एक संस्करण के 150 इकाइयां बनाए, डिज़ाइन को पुनः प्राप्त करें, फिर अगले के 200 बनाएं। यह अनुमान कि एक ही फिक्स्चर हजारों समान बोर्डों का परीक्षण करेगा, अब मान्य नहीं है। उच्च मात्रा में जो स्थिर लागतें न के बराबर थीं, वे अब कुछ सौ इकाइयों में फैलने पर दंडात्मक हो जाती हैं।

मॉडल टूट जाता है जब ICT ढांचा की कुल लागत जोखिम-समायोजित रणनीतियों की लागत से अधिक हो जाती है। वह सीमा मनमानी नहीं है। यह फिक्स्चर की लागत, इंजीनियरिंग समय, उत्पादन लीड टाइम, और फिक्स्चर रहित तरीकों से प्राप्त कवरेज का कार्य है। अधिकांश बोर्ड डिज़ाइनों के लिए, उस सीमा का निर्धारण 200 से 300 इकाइयों के बीच होता है।

इन-सर्किट टेस्टिंग का स्थिर लागत जाल

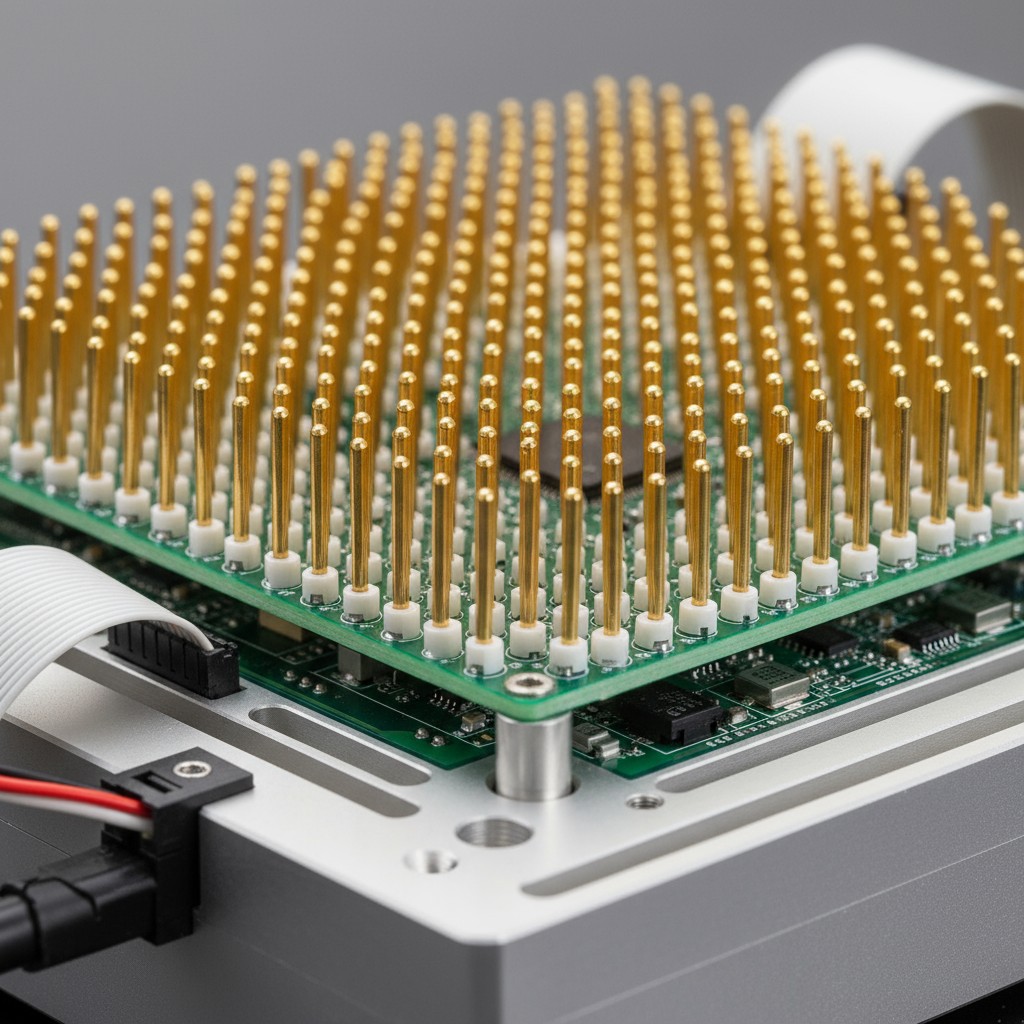

जबकि फिक्स्चर ICT की सबसे दृश्य लागत है, वास्तविक आर्थिक बोझ उससे कहीं अधिक व्यापक है। एक कस्टम ICT फिक्स्चर कोई स्टॉक में खरीदी जाने वाली वस्तु नहीं है; यह एक अभियांत्रिक अवशेष है, जिसे विशेष बोर्ड लेआउट के लिए डिज़ाइन किया गया है। डिज़ाइन प्रक्रिया में बोर्ड की नेटलिस्ट और घटक स्थानांतरण को एक यांत्रिक संरचना में अनुवाद करना होता है जिसमें वसंत-लोड टेस्ट प्रोब होते हैं, प्रत्येक विशेष टेस्ट पॉइंट के साथ मिलीमीटर के अंश में सटीकता से संरेखित। फिक्स्चर को घटक सहिष्णुता, बोर्ड की झुकाव, और प्रोब के पहनने का ध्यान रखना चाहिए। फिर इसे मान्य और डिबग किया जाना चाहिए—एक ऐसा भी process जो अक्सर प्रोब एक्सेस या सिग्नल अखंडता की अनदेखी की समस्याओं को उजागर करता है।

फिक्स्चर इंजीनियरिंग लागत और लीड टाइम्स

मध्यम जटिल फिक्स्चर के लिए इंजीनियरिंग लागत आमतौर पर $8,000 से $15,000 के बीच होती है। उच्च घनत्व बोर्डों के साथ सूक्ष्म-पिच घटक या सीमित परीक्षण बिंदु पहुंच के साथ, यह आंकड़ा $25,000 या उससे अधिक हो सकता है। यह पूरी तरह से उस अनुकूलित यांत्रिक और विद्युत इंटरफ़ेस की लागत है, जिसे बोर्ड को ICT उपकरण से जोड़ने के लिए आवश्यक है, स्वयं परीक्षक की पूंजीगत व्यय से अलग।

लीड टाइम भी बराबर महत्वपूर्ण है। जैसे ही एक बोर्ड डिज़ाइन अंतिम रूप दिया जाता है, फिक्स्चर डिज़ाइन और निर्माण में आमतौर पर दो से चार सप्ताह लगते हैं, जटिल डिज़ाइनों के लिए यह छह तक बढ़ सकता है। इस अवधि के दौरान, उत्पादन स्थगित हो जाता है। बोर्ड असेंबल किए जा सकते हैं, लेकिन उनका परीक्षण नहीं किया जा सकता है। वे इन्वेंट्री में बैठते हैं, इंतजार करते हैं। यदि इस अवधि के दौरान डिज़ाइन में परिवर्तन होता है—जो नई उत्पाद शुरुआत में सामान्य है—तो फिक्स्चर को संशोधित या रद्द करना पड़ता है। घड़ी रीसेट हो जाती है।

कम मात्रा में रन के लिए ब्रेकइवन गणित

कम मात्रा में रन के लिए आर्थिक फंसाव स्पष्ट हो जाता है जब फिक्स्चर की लागत को यूनिट गणना से विभाजित किया जाता है। $12,000 का फिक्स्चर 100 यूनिट रन के लिए प्रत्येक बोर्ड पर $120 बोझ जोड़ता है। $500 बिल ऑफ मटेरियल के साथ बोर्ड के लिए, यह 24 प्रतिशत परीक्षण ओवरहेड है। यदि ICT प्रक्रिया तेज भी है, तो आर्थिक दक्षता खराब होती है। वही फिक्स्चर 500 यूनिटों पर अमोर्टाइज़्ड होने पर प्रति यूनिट लागत $24 हो जाती है, जो एक अधिक स्वीकार्य पाँच प्रतिशत ओवरहेड है। अंतर पूरी तरह से मात्रा का कार्य है।

ब्रेकइवन पॉइंट वह जगह है जहां ICT की कुल लागत—इंजीनियरिंग, सेटअप, और लीड टाइम की अवसर लागत सहित—एक फिक्स्चर-रहित विकल्प की लागत के बराबर होती है। सीमा स्कैन, वेक्टरलेस परीक्षण, और एक लीन कार्यात्मक परीक्षण को मिलाकर एक रणनीति के लिए, ढांचे की लागत बहुत कम होती है। सीमा स्कैन के लिए कोई फिक्स्चर आवश्यक नहीं है, और वेक्टरलेस परीक्षण पुन: प्रयोग योग्य सेंसर्स का उपयोग करता है जो यांत्रिक संपर्क के बिना काम करते हैं। कोई भी कार्यात्मक परीक्षण फिक्स्चर आमतौर पर न्यूनतम और सामान्य होता है, न कि किसी बोर्ड-विशिष्ट कलाकृति जो कई सप्ताह के इंजीनियरिंग की आवश्यकता हो।

200 यूनिट्स से नीचे के उत्पादन वॉल्यूम पर, ICT की अर्थव्यवस्था गुम हो जाती है। 300 यूनिट्स से नीचे, मामला सीमांत होता है, जो बोर्ड की जटिलता पर निर्भर करता है। केवल 300 यूनिट्स से अधिक स्थिर, गैर-आवृत्त डिज़ाइनों के लिए ICT फिर से स्पष्ट आर्थिक समझ बनाने लगता है।

क्या है सीमारेखा स्कैन और बिना वेक्टर के परीक्षण वास्तव में

स्थापना-आधारित परीक्षण का विकल्प कठोरता में समझौता नहीं है बल्कि ऐसे तरीकों की ओर बदलाव है जो मौजूदा डिज़ाइन इन्फ्रास्ट्रक्चर और बिना संपर्क माप का लाभ उठाते हैं। इन टूल्स को उसी प्रवृत्ति को संबोधित करने के लिए विकसित किया गया था जो ICT को कमजोर करता है: बोर्ड की घनत्व में वृद्धि और भौतिक परीक्षण बिंदुओं तक पहुंच में कमी।

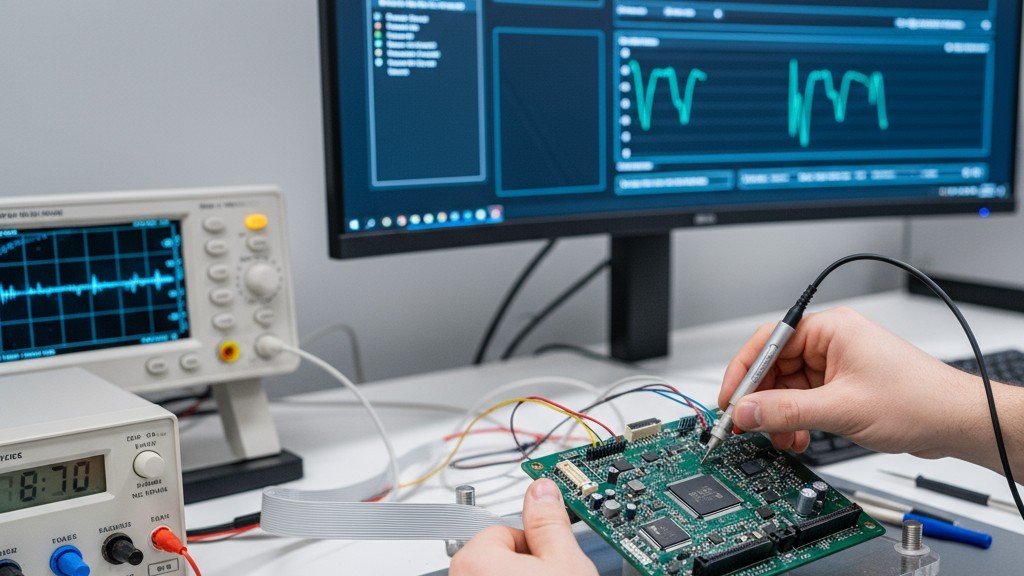

सीमा स्कान, जो IEEE 1149.1 मानक (आम तौर पर JTAG के रूप में जाना जाता है) में औपचारिक है, सीधे बोर्ड के एकीकृत सर्किटों में परीक्षण लॉजिक को एम्बेड करता है। संलग्न चिप्स में प्रत्येक इनपुट और आउटपुट पिन पर एक श्रृंखला होती है। परीक्षण के दौरान, एक सरल चार-तार इंटरफ़ेस इन चुड़ियों में पैटर्न को स्थानांतरित करता है, बोर्ड के नेट्स पर तर्क स्थितियों को नियंत्रित करता है। परिणामी स्थितियों को कैप्चर किया जाता है और विश्लेषण के लिए बाहर निकाला जाता है, जिससे परीक्षक को सिग्नल को नियंत्रित करने और निरीक्षण करने में मदद मिलती है, बिना भौतिक संपर्क के। यह अनुप्रयोगीय विधि शॉर्ट्स, ओपन और फंसे दोषों का पता लगाने में बहुत प्रभावी है।

वेक्तरलेस परीक्षण इसमे पूरक है, जो संधारित्र और प्रेरक मापन का उपयोग करके संपूर्ण बोर्ड में दोषों का पता लगाता है। बोर्ड के पास स्थित सेंसर ऐरे असेंबल किए गए घटकों और ट्रेसेस का इलेक्ट्रोमैग्नेटिक हस्ताक्षर मापता है। शॉर्ट्स मापने योग्य संधारित्र संयोजन बनाते हैं; ओपन चर इ impedance परिवर्तन दिखाते हैं। यह विधि तेज, गैर-संपर्क, और घटक की उपस्थिति, ध्रुवीयता, और लगभग मान का अनुमान लगाने में सक्षम है, जो खाली घटकों, उल्टे डायोड, या ब्रिज किए गए ट्रेसेस जैसे मिश्रित निर्माण दोषों को पकड़ने में प्रभावी है।

कवरेज तुलना: ट्रेड-ऑफ के पीछे आंकड़े

ICT को छोड़ने का मुख्य विरोध कवरेज है। जबकि ICT सिद्धांत रूप में, पर्याप्त परीक्षण बिंदु होने पर, बोर्ड पर हर नोड तक पहुंच सकता है, यह दावा कि विकल्प कमतर हैं, अधूरा है। असली सवाल यह है कि क्या वे उन दोषों को पकड़ने के लिए पर्याप्त कवरेज प्राप्त करते हैं जो वास्तव में होते हैं, और क्या एक केंद्रित कार्यात्मक परीक्षण शेष अंतर को पूरा कर सकता है।

क्या बाउंड्री स्कैन कवर करता है

बाउंड्री स्कैन कवरेज उस पर निर्भर करता है कि बोर्ड पर कितने कंपोनेंट्स JTAG मानक के अनुरूप हैं। डिजिटल लॉजिक से प्रभुत्व वाले बोर्डों—माइक्रोप्रोसेसर, FPGA, मेमोरी—के लिए कवरेज व्यापक है। स्कैन चेन इन उपकरणों के बीच इंटरकनेक्ट का परीक्षण कर सकता है, जिसमें शॉर्ट्स, ओपन, और स्टक-एट फॉल्ट के लिए 95 प्रतिशत से अधिक फॉल्ट डिटेक्शन दरें हैं। एक ऐसा बोर्ड जहां 80 प्रतिशत कंपोनेंट्स अनुरूप हैं, लगभग 70 से 85 प्रतिशत नेट कवरेज प्राप्त करेगा। एनालॉग सेक्शन्स, डिस्क्रीट कंपोनेंट्स, और विरासत भाग इस विधि से अदृश्य हैं। हालांकि, डिजिटल-भारी डिजाइनों के लिए, बॉउंड्री स्कैन अकेले ही इंटरकनेक्ट लेयर के लिए ICT के समान कवरेज प्रदान करता है, जहां अधिकांश असेंबली फॉल्ट्स होते हैं।

वेक्टरलेस परीक्षण में क्या जोड़ता है

वेक्टरलेस परीक्षण सीमांकन स्कैन द्वारा छोड़े गए अंतराल को पूरा करता है, विशेष रूप से निष्क्रिय घटकों और मोटे असेंबली दोषों के लिए। कैपेसिटिव माप can पता कर सकते हैं कि रेसिस्टर गायब हैं, कैपेसिटर मान गलत हैं, और डायोड उलटे हैं। जहां ICT के सीधे माप से कम सटीक है, यह सबसे सामान्य गलतियों के लिए एक प्रभावी स्क्रीन है: गलत घटक, गायब घटक, या गंभीर असमानता। इससे कुल_fault coverage में 10 से 20 प्रतिशत और जुड़ जाता है, जिससे उन हिस्सों के लिए एक संपर्क रहित सत्यापन स्तर प्रदान किया जाता है जिन्हें सीमा स्कैन नहीं देख सकता।

शेष अंतर और लीन कार्यात्मक परीक्षण इसे कैसे बंद करता है

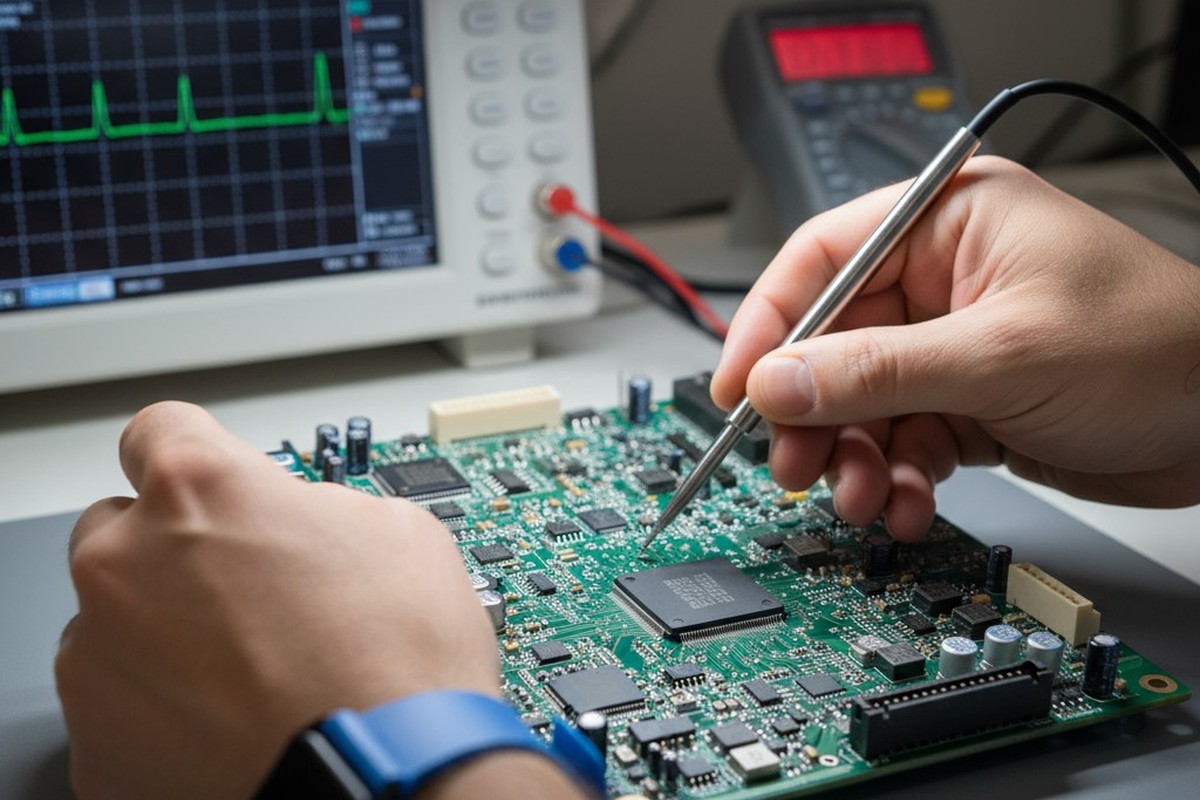

सीमा स्कान और वेक्टरलेस परीक्षण का संयोजन अभी भी कार्यात्मक सत्यापन और एनालॉग प्रदर्शन में एक अंतर छोड़ता है। एक घटक मौजूद हो सकता है और सही ढंग से जुड़ा हो सकता है, लेकिन अभी भी प्रणाली के भीतर ऑपरेट करने में विफल रह सकता है। एक पावर सप्लाई वोल्टेज प्रदान कर सकती है, लेकिन अत्यधिक रकेप के साथ। यही वह जगह है जहां एक लीन कार्यात्मक सर्किट परीक्षण (एफसीटी) अपनी भूमिका निभाता है। पूर्ण ICT सेटअप के विपरीत, एक लीन एफसीटी यह मान्य करता है कि बोर्ड यथार्थ परिस्थितियों में अपने इच्छित कार्य करता है। यह पावर को लागू करता है, इनपुट को उत्तेजित करता है, और आउटपुट को मापता है। एक मोटर नियंत्रक के लिए, यह PWM सिग्नल जेनरेशन की जांच कर सकता है; एक संचार बोर्ड के लिए, यह त्रुटि-मुक्त डेटा ट्रांसमिशन की जांच कर सकता है। कार्यात्मक परीक्षण संरचनात्मक परीक्षणों की पूर्ति करता है, उन दोषों को पकड़ता है जो अन्य तरीके नहीं देख सकते।

मिलकर, ये तीन तरीके आमतौर पर 85 से 95 प्रतिशत दोष कवरेज प्राप्त करते हैं। यह 100 प्रतिशत नहीं है, लेकिन व्यवहार में ICT भी नहीं है। परीक्षण बिंदु सीमाओं और जांच प्रहार के पहनने के कारण, वास्तविक दुनिया में ICT कवरेज इसकी सैद्धांतिक अधिकतम से कम होता है। कवरेज में यह अंतर लागत और लीड टाइम में किए गए नुकसान से बहुत कम है।

डिबग लूप का लाभ

परीक्षण कवरेज केवल मूल्य समीकरण का आधा हिस्सा है; दूसरा हिस्सा दोष पृथक्करण की गति और सटीकता है। एक परीक्षण जो दोष का पता लगाता है, लेकिन अस्पष्ट निदान प्रदान करता है, कारण खोजने में समय और लागत बढ़ाता है।

जबकि ICT दोष का संकेत करने में अच्छा है, इसकी निदान निराशाजनक रूप से अस्पष्ट हो सकती है। एक परीक्षक रिपोर्ट कर सकता है कि नोड 47 ग्राउंड से शॉर्टेड है, लेकिन यह क्यों या कहाँ है, इसकी व्याख्या नहीं करता। तकनीशियन को स्क्खेमैटिक ट्रेस करना, नेट का पता लगाना, और क्षेत्र का दृश्यों निरीक्षण करना पड़ता है—एक प्रक्रिया जो एक ज densely मल्टीलायर्ड बोर्ड पर घंटों खर्च कर सकती है।

सीमान्ता स्कैन निदान मौलिक रूप से अलग हैं। क्योंकि स्कैन चैन कंपोनेंट्स में एम्बेडेड है, टेस्टFaults को विशिष्ट पिन और उपकरणों तक सीमित कर देता है। दो नेट के बीच एक शॉर्ट को सही उपकरण पिन से पहचाना जाता है, जिससे खोज को कुछ वर्ग मिलीमीटर तक सीमित कर दिया जाता है। ओपन को निर्दिष्ट ड्राइवर और रिसीवर पेयर के बीच पता चलता है। डायग्नोस्टिक आउटपुट कोई फॉल्ट कोड नहीं है। यह एक नक्शा है। इस सटीकता का मतलब है कि ICT डेटा के साथ एक घंटे में डिबग करने वाले दोष को अक्सर 10 से 20 मिनट में सीमांत स्कैन से हल किया जा सकता है। एक सामान्य दोष दर के साथ 100-यूनिट रन के लिए, योग डिबग समय में बचत 10 घंटे से अधिक हो सकती है।

लीड टाइम और फ्लेक्सिबिलिटी: छुपी हुई कीमत

कम मात्रा के लिए ICT के खिलाफ आर्थिक तर्क प्रेरक हैं, लेकिन लीड टाइम का प्रतिबंध भी उतना ही महत्वपूर्ण है। दो से चार सप्ताह का फिक्स्चर इंजीनियरिंग प्रक्रिया डिजाइन फ्रीज और टेस्ट रेडीनेस के बीच एक अनिवार्य देरी लगाती है। नए उत्पाद के परिचय के लिए, जहां समय बाजार में पहुंचना जरूरी है, यह देरी अक्सर अस्वीकार्य होती है।

सीमान्ता स्कैन और वेक्टरलेस टेस्टिंग इस प्रतीक्षा को समाप्त कर देते हैं। टेस्ट सेटअप घंटों या दिनों में कॉन्फ़िगर किया जा सकता है, सप्ताह नहीं, जिससे बोर्ड असेंबली से टेस्ट और शिपमेंट तक लगातार प्रवाह में गुजर सकते हैं। यह लचीलापन तब महत्वपूर्ण होता है जब डिजाइनों में पुनरावृत्ति होती है। एक शुरुआती प्रोटोटाइप रन मुद्दों का पता लगा सकता है जिसमें बोर्ड लेआउट में बदलाव की आवश्यकता हो। ICT के साथ, हर संशोधन में एक नया या पुनः काम किया गया फिक्स्चर की आवश्यकता होती है, जिससे लागत और नेतृत्व समय फिर से लगते हैं। सीमान्ता स्कैन टेस्ट पैटर्न, जो नेटलिस्ट से जेनरेट होते हैं, स्वचालित रूप से डिज़ाइन के साथ अपडेट होती है। यह एक परीक्षण रणनीति बनाता है जो पुनरावृत्ति विकास का समर्थन करता है बजाय इसके कि इसे दंडित किया जाए।

कब अभी भी ICT चुनें

लेकिन कम मात्रा वाले ICT के खिलाफ मामला पूर्ण नहीं है। कुछ डिजाइनों और उत्पादन संदर्भों में अभी भी निवेश को उचित ठहराया जा सकता है।

उच्च घनत्व वाले एनालॉग या RF सेक्शनों वाले बोर्ड पूरी तरह फिक्स्चर-फ्री रणनीति के लिए खराब उम्मीदवार हैं। एनालॉग कंपोनेंट्स में सीमान्ता स्कैन लॉजिक का अभाव होता है, और महत्वपूर्ण प्रदर्शन विशेषताएँ जैसे लाभ या फ़ेज़ शोर संरचनात्मक रूप से सत्यापित नहीं की जा सकती हैं। यदि एनालॉग या RF सर्किटरी बोर्ड की कार्यक्षमता का 40 प्रतिशत से अधिक भाग का प्रतिनिधित्व करता है तो ICT का मामला बहुत मजबूत हो जाता है।

मेडिकल, एयरोस्पेस, और ऑटोमोटिव जैसे अनुपालन-आधारित उद्योग अक्सर उन विनियमों के तहत संचालित होते हैं जो विशिष्ट परीक्षण कवरेज या विधियों की अनिवार्यता करते हैं। यदि किसी मानक द्वारा इन- सर्किट परीक्षण या समकक्ष नोड-स्तर पहुंच की आवश्यकता होती है, तो वैकल्पिक रणनीतियाँ पर्याप्त नहीं हो सकती हैं। यहां, ICT की लागत बाजार में प्रवेश की एक अव्यवस्था विकल्प है।

अंत में, उच्च मात्रा उत्पादन के लिए स्पष्ट और प्रतिबद्ध मार्ग गणित बदल देता है। यदि प्रारंभिक 150-यूनिट रन छह महीनों के भीतर 1,000 यूनिट तक पहुंचने की उम्मीद है, तो फिक्स्चर की लागत कुल अपेक्षित मात्रा में वितरित हो जाती है। इसके लिए फरमान में उच्च विश्वास और स्थिर डिज़ाइन चाहिए—लेकिन इससे आरंभिक निवेश फायदेमंद साबित हो सकता है।

वैकल्पिक परीक्षण रणनीति का निर्माण

ICT को बदलना कोई आसान स्वैप नहीं है; यह परीक्षण वास्तुकला का पुन:कॉन्फ़िगरेशन है, जहां प्रत्येक सोपान उन दोषों को पकड़ता है जिन्हें दूसरों से नहीं देखा जा सकता।

प्रक्रिया को क्रमबद्ध होना चाहिए। पहली परत सीमा स्कैन है, जो तेज़ी से सभी अनुपालन उपकरणों पर चलता है ताकि बोर्ड के डिजिटल भागों पर इंटरकनेक्ट दोषों का पता लगाया जा सके। जो बोर्ड असफल होते हैं, उन्हें तुरंत पुनः कार्य के लिए चिह्नित किया जाता है, जिससे बाद में पावर लगाने पर आपदा दुर्घटना को रोका जा सके। दूसरी परत वेक्टरलेस टेस्टिंग है, जो पूरे बोर्ड पर चलता है ताकि गुम या गलत निष्क्रिय अवयवों, बड़े शॉर्ट्स, और पोलारिटी त्रुटियों का पता लगाया जा सके। यह स्कैन चैन के लिए अदृश्य कंपोनेंट्स और नेट्स को कवर करता है।

तीसरी और अंतिम परत एक केंद्रित कार्यात्मक परीक्षण है। संरचनात्मक दोषों को पहले ही फ़िल्टर करने के बाद, बोर्ड को शक्ति देकर इसकी महत्वपूर्ण कार्यक्षमताओं को सत्यापित किया जाता है कि वे यथार्थवादी परिचालन स्थितियों के तहत सही हैं। सीमा उस बोर्ड के उद्देश्य के अनुसार अनुकूलित की जाती है—जैसे डेटा अधिग्रहण बोर्ड पर ADC सटीकता का सत्यापन या पावर सप्लाई पर लोड विनियमन। इस क्रम में सुनिश्चित किया जाता है कि आपदा दोष जल्दी पकड़े जाएं और बिना नुकसान पहुंचाए, जिससे जटिल कार्यात्मक विफलताओं पर डिबग समय कम हो।

हाइब्रिड जटिलताएं वाले बोर्डों के लिए—जैसे घने डिजिटल कोर के आसपास एनालॉग सिग्नल कंडीशनिंग—एक हाइब्रिड रणनीति सबसे उपयुक्त हो सकती है। एक आंशिक ICT फिक्स्चर डिजाइन किया जा सकता है जो केवल महत्वपूर्ण एनालॉग सेक्शन का परीक्षण करे, और डिजिटल भाग को सीमा स्कैन के लिए छोड़ दे। आंशिक फिक्स्चर की अर्थव्यवस्था अधिक अनुकूल होती है, लागत और नेतृत्व समय को कम करते हुए संपूर्ण डिज़ाइन के लिए आवश्यक कवरेज प्रदान करती है।