जब एक डिज़ाइन फाइल इंजीनियरिंग कतार में आती है, तो हम पहले राउटिंग या कंपोनेंट प्लेसमेंट को नहीं देखते। हम पेस्ट मास्क लेयर को देखते हैं।

अधिकांश डिज़ाइनर इस लेयर को तांबे के पैड का प्रत्यक्ष अनुवाद मानते हैं: यदि बोर्ड पर कोई पैड है, तो स्टेंसिल में उससे मेल खाने वाला एक अपर्चर होना चाहिए। यह 1:1 तार्किक सुरुचिपूर्ण, सुसंगत, और CAD पर्यावरण में गणितीय रूप से पूर्ण है। यह भी आधुनिक मिश्र तकनीक बोर्डों पर असेंबली दोषों का सबसे सामान्य कारण है।

समस्या? एक Gerber फ़ाइल एक दो-आयामी मानचित्र है, लेकिन एक सोल्डर जॉइंट तीन-आयामी मात्रा है। जैसे ही हम स्क्रीन से उत्पादन क्षेत्र में जाते हैं, हम तरल गतिशीलता, सतह तनाव, और धातु पेस्ट को स्टील शीट के माध्यम से धकेलने की भौतिक सीमाओं से निपट रहे हैं।

यदि हम अपने ECAD सॉफ़्टवेयर के डिफ़ॉल्ट “100% कवरेज” आउटपुट के आधार पर बिना सोचे समझे स्टेंसिल काटते हैं, तो हम विफलता की गारंटी देते हैं। भारी कनेक्टर और फाइन-पिच माइक्रोचिप्स दोनों वाली बोर्ड पर, एक समान दृष्टिकोण आधे बोर्ड पर बहुत अधिक पेस्ट रहता है और बाकी आधा भूखा रहता है। हम अपने स्टेंसिल डेटा को कठिन बनाने के लिए नहीं बदलते; हम ऐसा इसलिए करते हैं क्योंकि भौतिकी इसकी मांग करती है।

सोल्डर एक मात्रा समस्या है

“कवरेज” को भूल जाइए। हमें क्यूबिक मिल्स में सोचना होगा।

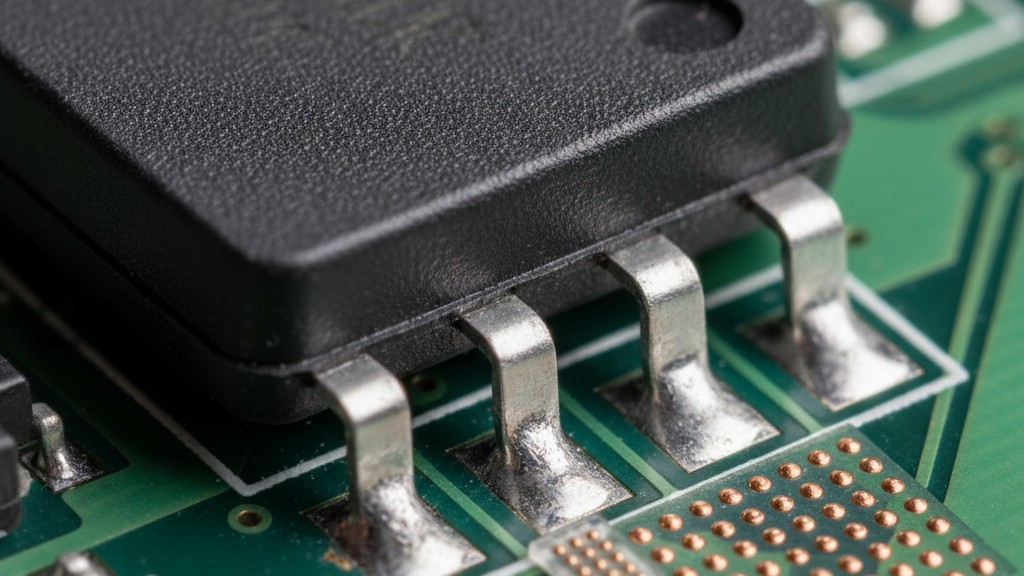

एक जॉइंट की यांत्रिक अखंडता — विशेष रूप से पावर कंपोनेंट्स और कनेक्टर्स के लिए — पूरी तरह से उस धातु फिलेट के वॉल्यूम पर निर्भर करती है। एक मानक सर्फेस माउंट पैड 5 मिल डिपॉजिट के साथ अच्छा दिख सकता है, लेकिन थ्रू-होल रीलॉफ हेडर या USB-C कनेक्टर एक अलग प्राणी हैं।

डिज़ाइनर अक्सर घबराते हैं जब एक कनेक्टर प्रोटोटाइप परीक्षण के दौरान टूट जाता है, मानते हुए कि भाग itself दोषपूर्ण है या हाउसिंग बहुत कमजोर है। वास्तव में, समस्या लगभग हमेशा स्टेंसिल मोटाई होती है। एक USB-C कनेक्टर में ऐसे कंकाल हैं जिनके नीचे पीबीसी के तीसरे भाग में गहराई से एंकर किए जाने की आवश्यकता होती है। यदि हम मानक 4 मिल या 5 मिल फॉयल का उपयोग करते हैं (जो अधिकांश सिग्नल बोर्ड के लिए सामान्य है), तो हम उस बर्रेल को भरने के लिए आवश्यक सोल्डर का केवल एक हिस्सा ही पहुंचाते हैं। पेस्ट सतह पर प्रिंट होता है, रिफ्लो होता है, और छेद में घुलमिल जाता है, जिससे एक कमजोर, भूखा मेनिस्कस बनता है जो पहली प्रविष्टि के तहत टूट जाता है।

इसे ठीक करने के लिए, हमें होल का कुल वॉल्यूम, पिन को घटाकर, फ़्लक्स बर्न-ऑफ के लिए 1TP1टी बैफ़र जोड़ने और स्टेंसिल अपर्चर को उल्टा इंजीनियर करने का हिसाब लगाना होगा ताकि पूरी मात्रा में पेस्ट पहुंच सके। अक्सर, बोर्ड पर पैड इतनी बड़ी नहीं होती कि वह उस गीले पेस्ट को पकड़ सके। यह हमें ओवरप्रिंट करने के लिए मजबूर करता है — जानबूझकर सोल्डर मास्क पर पेस्ट प्रिंट करना ताकि रीलॉफ के दौरान यह पैड पर वापस खिंच जाए।

क्षेत्रानुपात तल

जब बड़े भाग भूखमरी का सामना करते हैं, छोटे भागों को इसका विपरीत समस्या होती है: वे जाने से इनकार कर देते हैं। यहाँ “एरिया अनुपात” नियम उत्पादन योग्यता का कठोर आधार बन जाता है।

स्टेंसिल प्रिंटिंग दो शक्तियों के बीच एक युद्ध है: पेस्ट का सतह तनाव जो PCB पैड से चिपकता है, और स्टेंसिल एपर्चर के अंदर दीवारों से चिपकने वाले पेस्ट का घर्षण। पेस्ट को सफलतापूर्वक छोड़ने के लिए, पैड क्षेत्र आवेदन दीवारों से बहुत बड़ा होना चाहिए।

उद्योग मानक (IPC-7525) खतरे वाले क्षेत्र को 0.66 के अनुपात में सेट करता है। यदि यह अनुपात इससे नीचे गिरता है (मान लीजिए, 0.4mm पिच BGA या 01005 कैपेसिटर के लिए), तो पेस्ट स्टेंसिल के अंदर जाम हो जाता है बजाय बोर्ड पर जमा होने के। आप एक अच्छा प्रिंट प्राप्त करेंगे, शायद दो, और फिर एपर्चर बंद हो जाएंगे। स्वचालित ऑप्टिकल निरीक्षण (AOI) मशीन तुरंत “अपर्याप्त साेल्डर” का संकेत देना शुरू कर देगी।

हम इसे थोड़ा सा चकमा देने की कोशिश कर सकते हैं नैनो-कॉटिंग के साथ जो स्टील को हाइड्रोफोबिक बना देती हैं, प्रभावी रूप से एपर्चर की दीवारों को चिकनाई देकर, लेकिन यह एक अस्थायी समाधान है। ये कोटिंग्स 10,000 चक्र या आक्रामक अंडर-वाइप क्लीनिंग के बाद पहने लगते हैं। एकमात्र स्थायी इंजीनियरिंग समाधान ज्यामिति को बदलना है: या तो हम एपर्चर को बड़ा करते हैं (रिस्किंग ब्रिजिंग) या स्टेंसिल फॉयल को पतला करते हैं ताकि दीवार सतह क्षेत्र कम हो सके।

बड़ा भाग / छोटा भाग संघर्ष

अब हम आधुनिक इलेक्ट्रॉनिक्स असेम्बली का मुख्य संघर्ष: “बड़ा हिस्सा / छोटा हिस्सा” समस्या का सामना कर रहे हैं। आपके पास एक भारी D2PAK वोल्टेज रेगुलेटर हो सकता है जिसे गर्मी नष्ट करने के लिए बहुत सारा सोल्डर चाहिए, जो एक 0.35mm पिच वेफर- लेवल पैकेज के ठीक पास हो, जिसमें शॉर्टिंग से बचने के लिए एक सूक्ष्म पेस्ट का झाग चाहिए।

यदि हम “मानक” 5मिल स्टेंसिल फॉयल का उपयोग करें—जो कि 90% के कोट अनुरोधों के लिए डिफ़ॉल्ट विकल्प है—we इनमें से एक घटक को संकट में डालते हैं। 5मिल फॉयल D2PAK के लिए पर्याप्त वॉल्यूम प्रदान करता है, लेकिन यह छोटे वेफर चिप के लिए बहुत मोटा है; अनुपात गलत हो जाएगा, और पेस्ट छोड़ नहीं पाएगा। यदि हम छोटे चिप के लिए 3मिल फॉयल में स्विच करें, तो D2PAK भूखा रहेगा, जिसके कारण वायदे और थर्मल विफलताएँ होंगी।

डिजाइनर अक्सर पूछते हैं, “आप छोटे भाग के लिए एपर्चर आकार क्यों नहीं कम कर सकते?” हम कर सकते हैं, लेकिन क्षेत्र अनुपात को याद रखें: एपर्चर क्षेत्र को कम करते हुए जबकि फॉयल को मोटा रखें, सिर्फ अनुपात को और खराब कर देता है। X-अक्ष के समायोजन से Z-अक्ष की समस्या हल नहीं हो सकती।

इंजीनियरिंग टोपोग्राफी: द स्टेप स्टेंसल

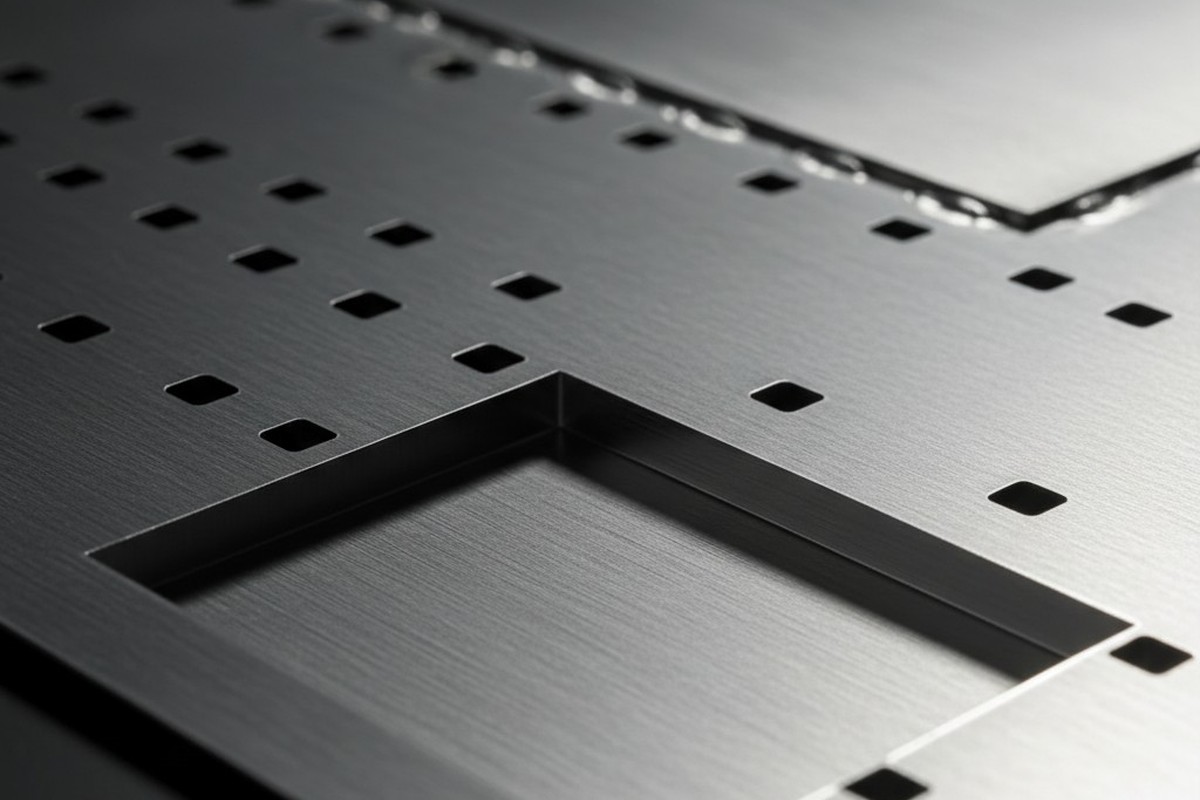

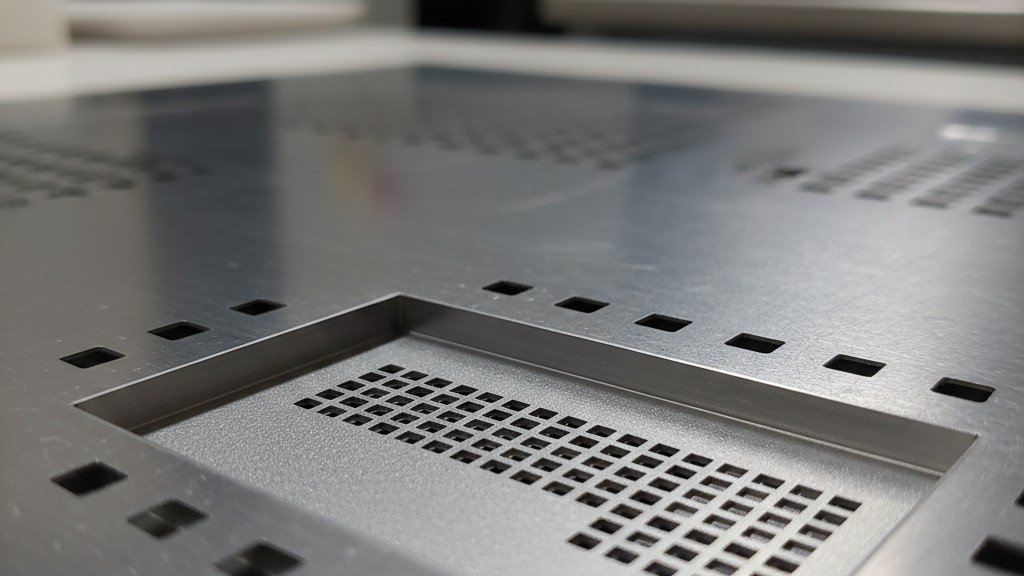

हमें स्टेंसिल को कम समान रूप से एक सपाट शीट की तरह नहीं, बल्कि एक टोपी वाले मानचित्र की तरह देखना है।

हम स्थानीय मोटाई क्षेत्रों बनाने के लिए स्टेप स्टेंसिल का उपयोग करते हैं। उस D2PAK या USB कनेक्टर के लिए, हम स्टेंसिल को “स्टेप अप” कर सकते हैं, स्टील का मोटा टैब (मान लीजिए, 6मिल या 8मिल) उस विशिष्ट क्षेत्र में वेल्डिंग कर सकते हैं। फाइन-पिच BGA के लिए, हम एक “स्टेप डाउन” पॉकेट की खदान करते हैं, जिससे मोटाई 3.5मिल या 3मिल तक कम हो जाती है, केवल उस घटक के फूटप्रिंट के लिए।

यह जादू नहीं है; इसमें सतर्क लेआउट की आवश्यकता है। सqueegee ब्लेड लचीला है, लेकिन यह तरल नहीं है। इसे संक्रमण स्थान की आवश्यकता होती है—आमतौर पर 50 से 100 मिल तक—ताकि यह स्टेप पर ऊपर या नीचे राइड कर सके बिना पेस्ट को स्किप किए या छेद से पोछे। हमें इन स्लॉट के क्षेत्रों को सावधानी से मानचित्रित करना होगा, यह सुनिश्चित करते हुए कि कोई भी महत्वपूर्ण घटक ढलान पर न बैठे। सही तरीक से करने पर, यह हमें शक्ति भागों के लिए विशाल मात्रा में पेस्ट प्रिंट करने और सूक्ष्म-घटक के लिए उच्च परिभाषा जमा करने की अनुमति देता है, एक ही पास में। यह एक “अविन्यास योग्य” बोर्ड को बदलकर एक ऐसा बनाता है जो 99% उपज पर चलता है।

विंडो पेन और आउटगैसिंग

ज्यामिति संशोधन सिर्फ मोटाई तक सीमित नहीं है। हमें फ्लक्स के व्यवहार से भी लड़ना पड़ता है।

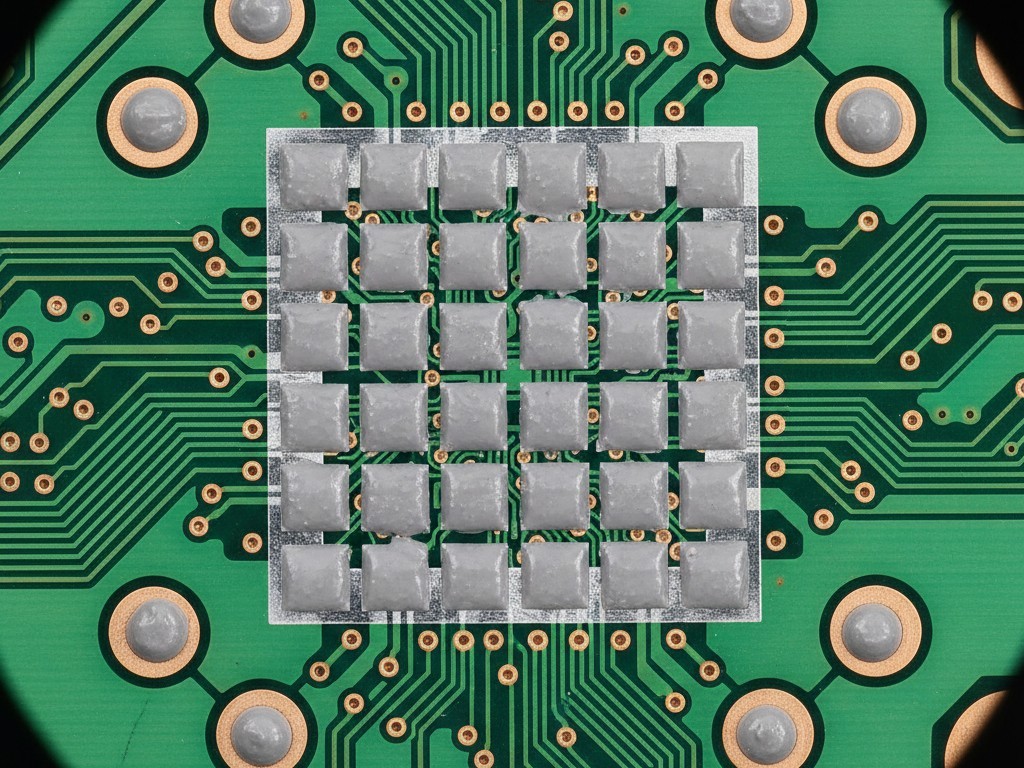

बड़े थर्मल पैड्स के तहत, जैसे कि QFNs या पावर FETs पर, डिज़ाइनर आमतौर पर कॉपर पैड के मिलान के लिए एक ठोस ब्लॉक का पेस्ट मास्क खींचते हैं। यदि हम इसे प्रिंट करते हैं, तो रीलो को दौरान जाल के नीचे वाष्पशील (flux vehicle) का एक बड़ा पूल फंस जाता है। जैसे ही फ्लक्स उबलता है, गैस का कहीं जाना नहीं होता, जिससे विशाल खाली स्थान बनते हैं—सोल्डर जॉइन में बायू बबल्स जो तापमान संचरण को रोकते हैं।

इसे रोकने के लिए, हम Gerber में ठोस ब्लॉक को नजरअंदाज करते हैं और एक “विंडो पेन” कमी लागू करते हैं। हम बड़े वर्गाकार उद्घाटन को छोटे वर्गों के जाल में तोड़ देते हैं, जो स्टील की 10-15 मिल की चैनलों से अलग होते हैं। ये चैनल आउटगैसिंग फ्लक्स के निकलने के लिए हाइवे के रूप में कार्य करते हैं। यह शक्ति इंजीनियरों के लिए प्रतिकूल लग सकता है जो अधिकतम थर्मल ट्रांसफर चाहते हैं, लेकिन प्रिंटिंग कम चिपकाना (अक्सर 60-70% कवरेज के बजाय 100%) वास्तव में परिणामस्वरूप होता है अधिक धातु से धातु संपर्क क्योंकि यह खाली करने की प्रक्रिया को समाप्त कर देता है।

संशोधन की अर्थशास्त्र

अक्सर लागत पर विरोध होता है। एक मानक लेजर-निर्मित स्टेंसिल की कीमत $150 से $200 हो सकती है। नैनो-कोटिंग वाले मल्टी-लेवल स्टेप स्टेंसिल की कीमत $350 से $450 तक हो सकती है। खरीदारी टीमें उस लाइन आइटम को देखती हैं और पूछती हैं कि क्या हम सिर्फ़ “इसे काम” कर सकते हैं मानक विकल्प के साथ।

विकल्प की लागत की तुलना में।

एक पुलित 0.4mm BGA को फिर से काम करना केवल कठिन नहीं है; अक्सर यह बिना बोर्ड या पड़ोसी कंपोनेंट्स को नुकसान पहुंचाए असंभव होता है। एक पूरी हुई यूनिट पर कटा हुआ कनेक्टर को बदलने की कीमत कच्चे पुर्जे से पचास गुना होती है। एक उचित स्टेंसिल की NRE (गैर-बारंबार इंजीनियरिंग) लागत एक बार की फीस है। एक हजार बोर्डों से सोल्डर को खींचने की लागत जो हमने भौतिकी को चुनौती देने की कोशिश की, बार-बार आने वाली, दर्दनाक और पूरी तरह से रोकी जा सकने वाली है। हम डेटा को संशोधित करते हैं क्योंकि पहली बार सही होने की लागत हमेशा बाद में सुधार करने की तुलना में कम होती है।