La pressione per individuare difetti di produzione prima che le schede vengano spedite è non negoziabile. Un singolo difetto sfuggito in un sistema critico può costare esponenzialmente più del testing che l'avrebbe rilevato. Questa realtà spinge molte squadre di ingegneria verso il testing in-circuit (ICT) come metodo predefinito, un modo a lungo ritenuto lo standard d'oro per la copertura. L'ICT completo offre accesso totale a quasi ogni nodo di una scheda, promettendo tassi di rilevamento dei difetti vicini al massimo teorico. Per produzioni di grande volume, l'investimento ha senso; i costi fissi di ingegnerizzazione delle fixture e delle apparecchiature di testing si ammortizzano su migliaia di unità, riducendo l'onere per singola unità a livelli trascurabili.

Ma l'economia si capovolge quando i volumi di produzione diminuiscono. Per produzioni sotto alcune centinaia di unità, le stesse forze dell'ICT diventano svantaggi. La fixture personalizzata richiesta per ogni progettazione di scheda comporta un alto costo fisso di ingegneria che non si scala. I tempi di produzione si allungano mentre le fixture vengono progettate, costruite e debugate. Le iterazioni di progettazione, comuni nell'introduzione di nuovi prodotti, invalidano le fixture completamente, costringendo il ciclo a ricominciare. In PCBA, abbiamo visto questa matematica in azione in centinaia di progetti. Per produzioni sotto le 200-300 unità, l'ICT completo raramente vale il suo costo.

L'alternativa non è abbandonare il testing rigoroso, ma sostituire il modello dipendente dalla fixture con una strategia più snella e veloce basata su boundary scan, testing senza vettori e test funzionali mirati. Questa combinazione offre una copertura dei difetti paragonabile, elimina il collo di bottiglia della fixture e fornisce un ciclo di debug più rapido quando vengono trovati difetti. Questo cambiamento non è ideologico; è una risposta pratica alle attriti matematici e meccanici che l'ICT impone alla produzione agile e a basso volume.

L'assunzione ICT e dove si rompe

Il testing in-circuit è diventato lo standard del settore in un'epoca di progetti ad alto volume e stabili. Il modello era semplice: investire pesantemente in anticipo in una fixture di test personalizzata e in un tester sofisticato, poi sfruttare quell'investimento su decine di migliaia di unità identiche. Con i tempi di test per unità misurati in secondi, il costo marginale per scheda era praticamente zero dopo l'assorbimento dei costi fissi. Per un produttore di elettronica di consumo che produce 50.000 unità dello stesso SKU, il calcolo era ineguagliabile.

Quel modello di produzione si è fratturato. La moderna produzione di elettronica serve sempre più mercati con alta varietà e basso volume. I cicli di vita del prodotto sono più brevi, le iterazioni di progettazione più frequenti, e la personalizzazione un vantaggio competitivo. Un'azienda potrebbe produrre 150 unità di una variante, iterare il progetto, poi produrre 200 della successiva. L'assunzione che una singola fixture testerà migliaia di schede identiche non è più valida. I costi fissi che erano trascurabili in alta produzione diventano penalizzanti se distribuiti su poche centinaia di unità.

Il modello si rompe quando il costo totale dell'infrastruttura ICT supera il costo, rettificato per il rischio, delle strategie alternative. Questa soglia non è arbitraria. È una funzione del costo della fixture, del tempo di ingegneria, del tempo di produzione, e della copertura raggiungibile con metodi senza fixture. Per la maggior parte dei progetti di schede, quella soglia si colloca tra 200 e 300 unità.

La trappola dei costi fissi del testing in-circuit

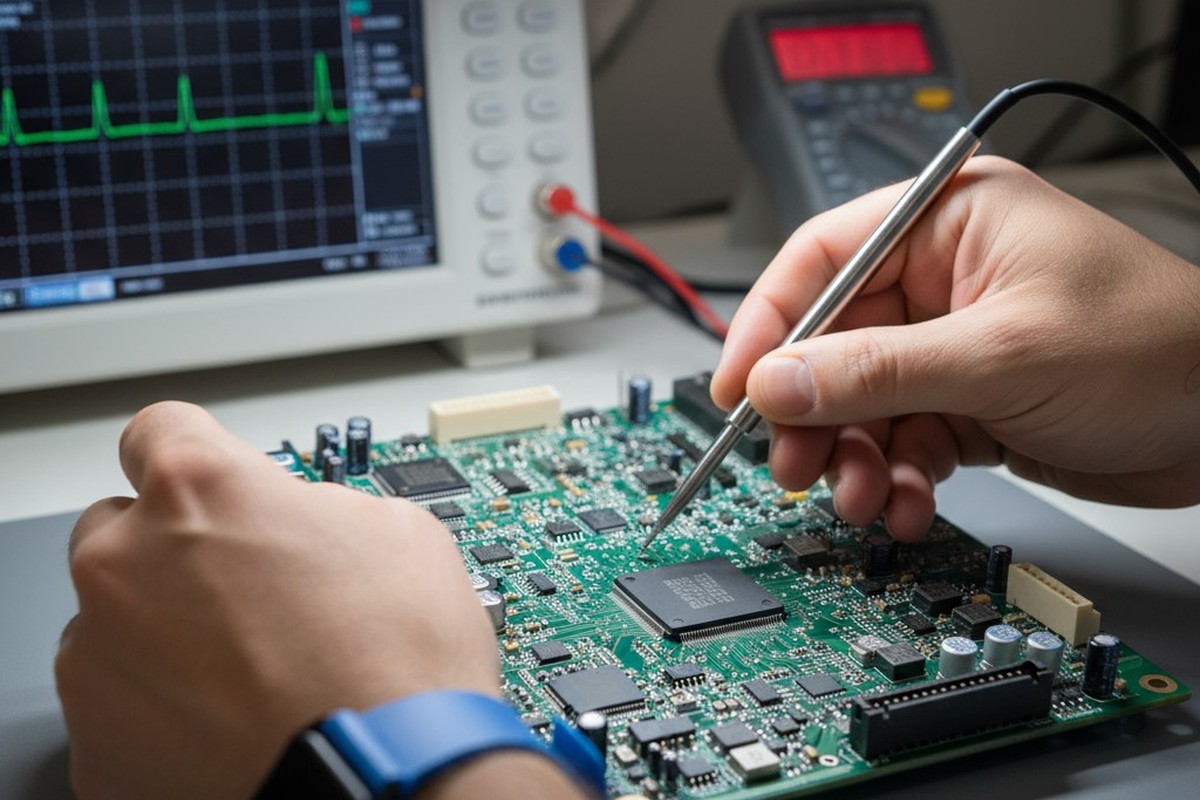

Mentre la fixture è il costo più visibile dell'ICT, il vero onere economico è molto più ampio. Una fixture ICT personalizzata non è un acquisto da scaffale; è un artefatto ingegnerizzato, costruito appositamente per un layout di scheda specifico. Il processo di progettazione richiede di tradurre la netlist e la disposizione dei componenti della scheda in una struttura meccanica dotata di sonde di test a molla, ognuna allineata a un punto di test specifico con precisione millimetrica. La fixture deve considerare tolleranze dei componenti, deformazioni della scheda e usura delle sonde. Deve quindi essere validata e debugata—un processo che spesso rivela problemi imprevisti di accesso alle sonde o integrità del segnale.

Costi di Ingegneria delle Fixture e Tempi di Consegna

Il costo di ingegneria per un supporto moderatamente complesso generalmente si aggira tra 8.000 e 15.000 $. Schede ad alta densità con componenti a passo fine o con accesso limitato ai punti di test possono portare questa cifra a 25.000 $ o più. Si tratta esclusivamente del costo dell'interfaccia meccanica ed elettrica personalizzata necessaria per connettere la scheda all'attrezzatura ICT, separata dalla spesa capitale del tester stesso.

Il tempo di consegna è altrettanto importante. Dal momento in cui si finalizza il progetto di una scheda, la progettazione e la fabbricazione del supporto di solito richiedono da due a quattro settimane, estendendosi fino a sei per progetti complessi. Durante questo periodo, la produzione è in stallo. Le schede possono essere assemblate, ma non possono essere testate. Rimangono in inventario, in attesa. Se il progetto cambia durante questa finestra—una situazione comune nelle nuove introduzioni di prodotti—il supporto deve essere revisionato o scartato. Il tempo ricomincia da capo.

Il calcolo del punto di pareggio per i bassi volumi di produzione

La trappola economica diventa evidente quando i costi del supporto vengono divisi per il numero di unità. Un supporto da 12.000 $ per una produzione di 100 unità aggiunge un onere di 120 $ a ogni scheda. Per una scheda con una distinta base di 500 $, ciò rappresenta un overhead di test del 24 percento. Anche se il processo ICT è veloce, l'efficienza economica è scarsa. Lo stesso supporto ammortizzato su 500 unità abbassa il costo per unità a 24 $, con un overhead molto più accettabile del cinque percento. La differenza è puramente una funzione del volume.

Il punto di pareggio è dove il costo totale dell'ICT—comprese ingegneria, configurazione e il costo opportunità del tempo di consegna—eguaglia il costo di un'alternativa senza supporto. Per una strategia che combina boundary scan, testing senza vettori e un test funzionale snello, il costo dell'infrastruttura è drasticamente inferiore. Il boundary scan non richiede supporto, e il testing senza vettori utilizza sensori riutilizzabili che funzionano senza contatto meccanico. Qualsiasi supporto funzionale è tipicamente minimo e generico, non un artefatto specifico della scheda che richiede settimane di ingegneria.

A volumi di produzione inferiori alle 200 unità, l'economia dell'ICT si sgretola. Sotto le 300 unità, la questione è marginale, dipendente dalla complessità della scheda. Solo sopra le 300 unità, per progetti stabili e non iterativi, l'ICT inizia a tornare a un senso economico chiaro.

Cosa sono effettivamente il Boundary Scan e il Test senza vettori

L'alternativa ai test basati su fixture non è un compromesso sulla rigorosità, ma un passaggio a metodi che sfruttano l'infrastruttura di progettazione esistente e la misurazione senza contatto. Questi strumenti sono stati sviluppati per rispondere alla stessa tendenza che minaccia l'ICT: aumento della densità delle schede e diminuzione dell'accesso ai punti di prova fisici.

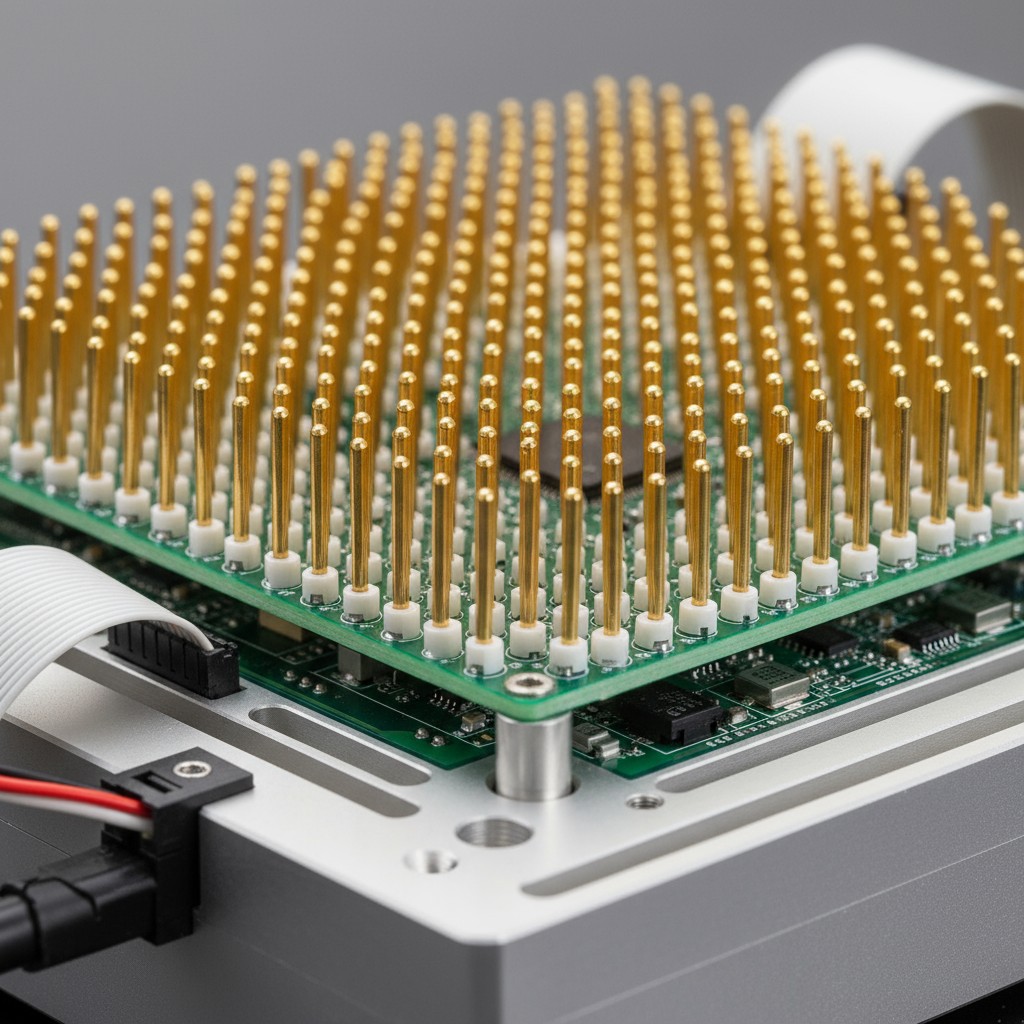

Il boundary scan, formalizzato nello standard IEEE 1149.1 (comunemente noto come JTAG), incorpora la logica di test direttamente nei circuiti integrati di una scheda. I chip conformi includono una catena di celle a ogni pin di ingresso e uscita. Durante un test, un'interfaccia a quattro fili semplice sposta schemi in queste celle, controllando gli stati logici sulle reti della scheda. Gli stati risultanti vengono catturati e trasmessi fuori per l'analisi, consentendo al tester di controllare e osservare i segnali a livello di pin senza contatto fisico. Questo metodo non invasivo è molto efficace nel rilevare cortocircuiti, aperture e guasti di blocco tra dispositivi conformi.

Il testing senza vettori integra questo metodo utilizzando misurazioni capacitive e induttive per rilevare guasti su tutta la scheda. Una matrice di sensori posizionata vicino alla scheda misura la firma elettromagnetica dei componenti e delle tracce assemblate. I cortocircuiti generano un accoppiamento capacitivo misurabile; le aperture mostrano cambiamenti di impedenza caratteristici. Il metodo è rapido, senza contatto e può dedurre la presenza dei componenti, la polarità e il valore approssimativo, rendendolo efficace nel catturare difetti di produzione grossolani come componenti mancanti, diodi invertiti o tracce collegate in modo errato.

Confronto di copertura: i numeri dietro allo scambio

L'obiezione principale all'abbandono dell'ICT è la copertura. Mentre l'ICT può, in linea di principio, accedere a ogni nodo di una scheda con abbastanza punti di test, l'affermazione che le alternative siano inferiori è incompleta. La vera domanda è se ottengano una copertura sufficiente per rilevare i guasti che effettivamente si verificano, e se un test funzionale mirato possa colmare il restante divario.

Cosa copre il Boundary Scan

La copertura della scansione di confine dipende da quanti componenti sulla scheda sono conformi allo standard JTAG. Per schede dominate dalla logica digitale—microprocessori, FPGA, memoria—la copertura è estesa. La catena di scansione può testare l'interconnessione tra questi dispositivi con tassi di rilevamento dei guasti superiori al 95 percento per cortocircuiti, aperture e guasti stuck-at. Una scheda in cui l'80 percento dei componenti è conforme otterrà circa il 70-85 percento di copertura netta. Le sezioni analogiche, i componenti discreti e le parti legacy sono invisibili a questo metodo. Tuttavia, per i progetti con forte contenuto digitale, la scansione di confine da sola offre una copertura paragonabile all'ICT per il livello di interconnessione, dove si verificano la maggior parte dei guasti di assemblaggio.

Cosa aggiunge il Testing senza Vettori

Il testing senza vettore colma le lacune lasciate dalla scansione di confine, in particolare per componenti passivi e difetti di assemblaggio grossolani. Le misurazioni capacitivi possono rilevare resistenze mancanti, valori di condensatore incorretti e diodi invertiti. Pur essendo meno precise delle misurazioni dirette dell’ICT, rappresentano un’ottima verifica per gli errori più comuni: componente sbagliato, componente mancante o grave disallineamento. Questo aggiunge un altro 10-20 percento alla copertura totale di guasti, offrendo uno strato di verifica senza contatto per le parti che la scansione di confine non può vedere.

Il divario residuo e come il test funzionale snello lo colma

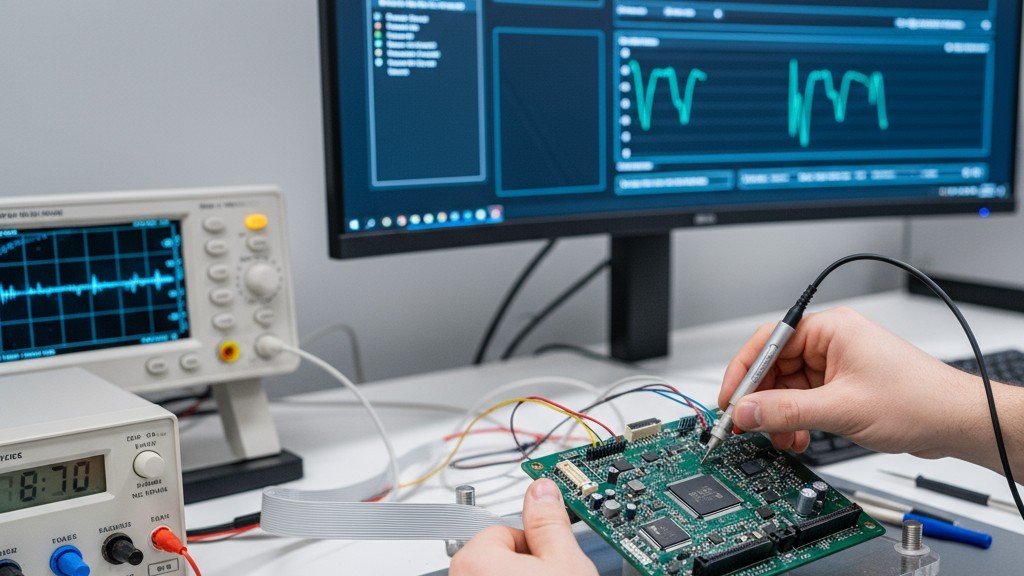

La combinazione di boundary scan e testing senza vettori lascia ancora un divario nella validazione funzionale e nelle prestazioni analogiche. Un componente può essere presente e correttamente collegato, ma ancora fallire nel funzionare secondo le specifiche. Una fonte di alimentazione potrebbe fornire tensione ma con un'oscillazione eccessiva. È qui che entra in gioco un test di circuito funzionale snello (FCT). A differenza di un setup ICT completo, un FCT snello convalida che la scheda svolga la funzione prevista in condizioni realistiche. Applica alimentazione, stimola gli ingressi e misura le uscite. Per un controller motore, potrebbe verificare la generazione del segnale PWM; per una scheda di comunicazione, potrebbe controllare la trasmissione di dati senza errori. Il test funzionale completa i test strutturali, individuando guasti che gli altri metodi non possono vedere.

Combinati, questi tre metodi raggiungono tipicamente una copertura dei guasti dell'85-95 percento. Non è il 100 percento, ma nemmeno l'ICT nella pratica. A causa delle limitazioni dei punti di test e dell'usura delle sonde, la copertura ICT del mondo reale spesso è inferiore al massimo teorico. La differenza nella copertura è molto inferiore alla penalizzazione in termini di costo e tempi di consegna.

Vantaggio del ciclo di debug

La copertura dei test è solo metà dell'equazione del valore; l'altra metà è la velocità e la precisione nell'isolamento dei guasti. Un test che rileva un guasto ma fornisce diagnosi vaghe aumenta il tempo e il costo necessari per trovare la causa principale.

Mentre l'ICT è ottimo nel segnalare i guasti, le sue diagnosi possono essere frustrantemente vaghe. Un tester potrebbe segnalare che il nodo 47 è collegato a massa, ma non spiega il perché o il dove. Il tecnico deve tracciare lo schema, individuare la rete e ispezionare visivamente l'area—un processo che può richiedere ore su una scheda complessa a più strati.

Le diagnosi di scansione di boundary sono fondamentalmente diverse. Poiché la catena di scansione è incorporata nei componenti, il test isola i difetti a pin e dispositivi specifici. Un cortocircuito tra due reti viene identificato dai pin esatti del dispositivo coinvolti, riducendo la ricerca a poche millimetri quadrati. Le aperture vengono rilevate tra specifiche coppie di driver e riceventi. L'output diagnostico non è un codice di errore. È una mappa. Questa precisione significa che un difetto che richiede un'ora di debug con dati ICT può spesso essere risolto in 10-20 minuti con boundary scan. Per una produzione di 100 unità con un tasso di difetti tipico, il tempo di debug cumulativo risparmiato può superare le 10 ore.

Lead time e flessibilità: il valore nascosto

L'argomento economico contro l'ICT per bassi volumi è convincente, ma la penalità del tempo di consegna è altrettanto significativa. Il processo di ingegnerizzazione del dispositivo in due-sei settimane impone un ritardo obbligatorio tra il blocco del progetto e la prontezza al test. Per l'introduzione di un nuovo prodotto, dove il time-to-market è critico, questo ritardo è spesso inaccettabile.

Boundary scan e i test senza vettori eliminano questa attesa. La configurazione del test può essere preparata in ore o giorni, non settimane, consentendo alle schede di passare dall'assemblaggio al test e alla spedizione in un flusso continuo. Questa flessibilità è fondamentale quando i disegni si iterano. Un primo prototipo può rivelare problemi che richiedono modifiche al layout della scheda. Con l'ICT, ogni revisione richiede un nuovo o rielaborato dispositivo di fissaggio, comportando nuovamente i costi e i tempi di consegna. I modelli di test boundary scan, generati dal netlist, si aggiornano automaticamente con il progetto. Ciò crea una strategia di test che supporta lo sviluppo iterativo anziché penalizzarlo.

Quando scegliere ancora l'ICT

Ma il caso contro l'ICT a basso volume non è assoluto. Alcuni disegni e contesti di produzione ancora giustificano l'investimento.

Le schede con sezioni analogiche o RF ad alta densità sono cattive candidate per una strategia puramente senza dispositivo. I componenti analogici mancano della logica di boundary scan e caratteristiche di prestazione critiche come guadagno o rumore di fase non possono essere verificate strutturalmente. Se il circuito analogico o RF rappresenta più del 40 percento delle funzionalità della scheda, il caso per l'ICT si rafforza notevolmente.

Le industrie guidate dalla conformità, come medicale, aerospaziale e automotive, spesso operano sotto normative che richiedono una copertura di test o metodi specifici. Se uno standard di regolamentazione richiede test in-circuit o accesso a livello di nodo equivalente, strategie alternative potrebbero non risultare sufficienti. Qui, il costo dell'ICT è un costo non negoziabile per l'ingresso nel mercato.

Infine, un percorso chiaro e deciso verso la produzione in volumi elevati cambia le regole del gioco. Se una prima produzione di 150 unità è prevista per scalare fino a 1.000 unità entro sei mesi, il costo del dispositivo di fissaggio si ammortizza sull'intero volume previsto. Questo richiede alta fiducia nelle previsioni e un progetto stabile, ma può rendere l'investimento iniziale conveniente.

Costruire la strategia alternativa di testing

Sostituire l'ICT non è una semplice sostituzione; è una ristrutturazione dell'architettura del test in una strategia stratificata, dove ogni strato rileva i difetti che gli altri potrebbero perdere.

Il processo dovrebbe essere sequenziale. Il primo strato è il boundary scan, che si esegue rapidamente su tutte le device conformi per rilevare difetti di interconnessione sulle parti digitali della scheda. Le schede che falliscono vengono segnalate per una correzione immediata, evitando fallimenti catastrofici quando viene applicata l'alimentazione più tardi. Il secondo strato è il test senza vettori, che viene eseguito su tutta la scheda per rilevare componenti passivi mancanti o errati, cortocircuiti grossolani e errori di polarità. Copre i componenti e le reti invisibili alla catena di scansione.

Il terzo e ultimo strato è un test funzionale mirato. Con i difetti strutturali già filtrati, la scheda viene alimentata per convalidare le sue funzioni critiche in condizioni operative realistiche. La portata è adattata allo scopo della scheda—verifica della precisione dell'ADC su una scheda di acquisizione dati o regolazione del carico su una alimentazione. Questa sequenza garantisce che i difetti catastrofici siano individuati precocemente e in modo non distruttivo, riducendo al minimo il tempo di debug sui guasti funzionali più complessi.

Per schede con complessità ibrida—ad esempio, un core digitale denso circondato da condizionamento analogico—potrebbe essere preferibile una strategia ibrida. È possibile progettare un dispositivo di fissaggio ICT parziale per sondare solo la sezione critica analogica, lasciando che la parte digitale venga verificata con boundary scan. L'economia di un dispositivo parziale è più favorevole, riducendo costi e tempi di consegna mentre si garantisce la copertura necessaria per tutto il progetto.