De druk om fabricatiefouten te vangen voordat de borden verzonden worden, is niet onderhandelbaar. Een enkele ontsnapte defect in een kritisch systeem kan exponentieel meer kosten dan de test die het had kunnen detecteren. Deze realiteit drijft veel engineeringteams naar in-circuit testen (ICT) als standaard, een methode die lang werd beschouwd als de gouden standaard voor dekking. Volledige ICT biedt uitgebreide toegang tot bijna elke node op een bord, met belofte van foutdetectierates die de theoretische maximum benaderen. Voor grootschalige productie is de investering zinvol; de vaste kosten van fixture-engineering en testapparatuur worden verdeeld over duizenden eenheden, waardoor de kosten per eenheid tot verwaarloosbare niveaus dalen.

Maar de economie keert om wanneer de productievolumes dalen. Voor producties van minder dan enkele honderden eenheden worden de sterktes van ICT juist nadelen. De op maat gemaakte fixture die nodig is voor elk bordontwerp brengt een sterke vaste engineeringskost met zich mee die niet schaalt. Levertijden rekken op terwijl fixtures worden ontworpen, gebouwd en gedebugd. Ontwerprondes, gebruikelijk bij nieuwe productintroducties, maken fixtures volledig onbruikbaar, waardoor de cyclus moet worden herhaald. Bij Bester PCBA hebben wij dit mathematische gedrag gezien in honderden projecten. Voor producties onder de 200 tot 300 eenheden verdient volledige ICT zelden zijn kost.

Het alternatief is niet het verlaten van rigoureus testen, maar het vervangen van het fixture-afhankelijke model door een slanker, sneller strategie gebaseerd op boundary scan, vectorloos testen en gerichte functionele tests. Deze combinatie levert vergelijkbare foutdekking, verwijdert de bottleneck in de fixture en biedt een snellere debug-loop wanneer fouten worden gevonden. Deze verschuiving is geen ideologie; het is een praktische reactie op de mathematische en mechanische frictie die ICT oplegt voor lage volumes, agile productie.

De ICT-aanname en waar deze breekt

In-circuit testen werd de industrienorm in een tijdperk van grootschalige, stabiele ontwerpen. Het model was simpel: investeer zwaar vooraf in een op maat gemaakte testfixture en een geavanceerde tester, en benut die investering bij tienduizenden identieke eenheden. Met per-eenheid-testtijden gemeten in seconden was de marginale kost per bord effectief nul nadat de vaste kosten waren inbegrepen. Voor een consumentenelektronicafabrikant die 50.000 eenheden van hetzelfde SKU produceert, was de wiskunde onweerlegbaar.

Dat productiemodel is gebroken. Moderne elektronica-productie bedient steeds meer markten met een hoge mix en laag volume. Productlevenscycli worden korter, ontwerpiteraties frequenter, en personalisatie is een concurrentievoordeel. Een bedrijf kan 150 eenheden van één variant produceren, het ontwerp aanpassen, en vervolgens 200 van de volgende. De veronderstelling dat een enkele fixture duizenden identieke borden kan testen, geldt niet meer. De vaste kosten die in hoge volumes verwaarloosbaar waren, worden pijnlijk wanneer ze worden uitgespreid over enkele honderden eenheden.

Het model faalt wanneer de totale kosten van ICT-infrastructuur de risico-gecorrigeerde kosten van alternatieve strategieën overschrijden. Die drempel is niet arbitrair. Het is afhankelijk van fixturekosten, engineeringtijd, productietijd en de dekking die haalbaar is met fixture-loze methoden. Voor de meeste bordontwerpen ligt die drempel tussen 200 en 300 eenheden.

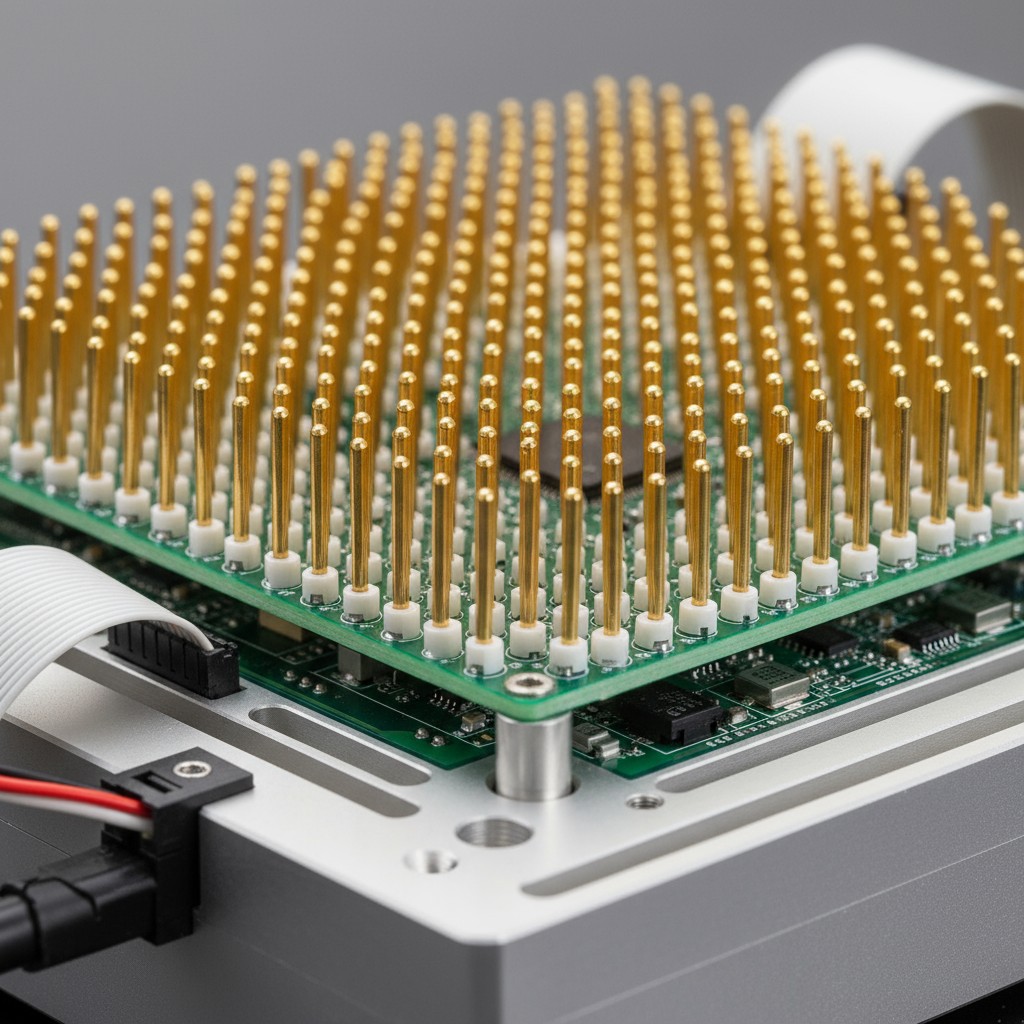

De vaste kostenval van in-circuit testen

Hoewel de fixture de meest zichtbare kosten van ICT is, ligt de ware economische last veel breder. Een op maat gemaakte ICT-fixture is geen standaard aankoop; het is een engineering-artifact, purpose-built voor een specifiek bordontwerp. Het ontwerp proces vereist het vertalen van de netlist en componentplaatsing van het bord naar een mechanische structuur die bezaaid is met veerspannende testprobes, elk afgestemd op een specifiek testpunt met sub-millimeter precisie. De fixture moet rekening houden met toleranties van componenten, warping van het bord en slijtage van probes. Het moet vervolgens worden gevalideerd en gedebugd — een proces dat vaak onvoorziene problemen aan het licht brengt met probe toegang of signaalintegriteit.

Fixture Engineering Kosten en Doorlooptijden

De ingenieurkosten voor een matig complexe fixture liggen meestal tussen $8.000 en $15.000. Hoog-dichtheidsplaten met fijne-pitch componenten of beperkte testpunttoegang kunnen dat bedrag omhoog duwen tot $25.000 of meer. Dit is puur de kostprijs van de op maat gemaakte mechanische en elektrische interface die nodig is om het bord aan de ICT-uitrusting te verbinden, los van de kapitaalkosten van de tester zelf.

De doorlooptijd is even belangrijk. Vanaf het moment dat een ontwerp van een bord definitief is, vereist het ontwerp en de fabricage van de fixture meestal twee tot vier weken, uitlopend tot zes voor complexe ontwerpen. Tijdens deze periode ligt de productie stil. Borden kunnen worden geassembleerd, maar ze kunnen niet worden getest. Ze liggen in voorraad, wachtend. Als het ontwerp tijdens deze periode verandert—een veelvoorkomend verschijnsel bij nieuwe productintroducties—moet de fixture worden herzien of weggegooid. De klok wordt opnieuw gezet.

De breakeven-berekening voor lage volume runs

De economische valstrik wordt duidelijk wanneer de kosten van de fixture worden gedeeld door het aantal eenheden. Een fixture van $12.000 voor een run van 100 stuks voegt een last van $120 toe aan elk bord. Voor een bord met een stuklijst van $500 is dat een test overhead van 24 procent. Zelfs als het ICT-proces snel is, is de economische efficiëntie slecht. Diezelfde fixture, afgeschreven over 500 eenheden, verlaagt de kost per stuk tot $24, een veel acceptabeler overhead van vijf procent. Het verschil is puur een functie van volume.

Het breekpunt is waar de totale kosten van ICT—including engineering, opzet en de opportuniteitskosten van de doorlooptijd—gelijk zijn aan de kosten van een fixtureloze alternatieve aanpak. Voor een strategie die boundary scan, vectorloos testen en een lean functioneel test combineert, zijn de infrastructuurkosten aanzienlijk lager. Boundary scan vereist geen fixture, en vectorloos testen gebruikt herbruikbare sensoren die werken zonder mechanisch contact. Elke functionele testfixture is doorgaans minimaal en generiek, niet een bord-specifiek artefact dat wekenlang engineering vereist.

Bij productvolumes onder de 200 stuks loopt de economie van ICT vast. Onder de 300 stuks is het marginaal, afhankelijk van de complexiteit van het bord. Pas boven de 300 stuks, voor stabiele, niet-iteratieve ontwerpen, wordt ICT weer economisch zinvol.

Wat Boundary Scan en Vectorless Testing werkelijk zijn

Het alternatief voor fixture-gebaseerd testen is geen compromis in strengheid, maar een verschuiving naar methoden die bestaande ontwerp-infrastructuur en contactloze metingen benutten. Deze tools zijn ontwikkeld om dezelfde trend aan te pakken die ICT ondermijnt: toenemende plaatdichtheid en afgenomen toegang tot fysieke testpunten.

Boundary scan, formeel vastgelegd in de IEEE 1149.1 standaard (bekend als JTAG), integreert testlogica direct in de geïntegreerde schakelingen van een bord. Conformistische chips bevatten een keten van cellen bij elke invoer- en uitvoerpins. Tijdens een test schakelt een eenvoudige vierdradige interface patronen in deze cellen, waarmee de logische staten op de netwerken van het bord worden geregeld. De resulterende staten worden vastgelegd en uitgezet voor analyse, waardoor de tester signalen op de pin-niveau kan controleren en observeren zonder fysieke contact. Deze niet-invasieve methode is zeer effectief bij het detecteren van kortsluitingen, open verbindingen en 'stuck-at' foutenmidden compatibele apparaten.

Vectorloos testen vult dit aan door gebruik te maken van capacitieve en inductieve metingen om fouten op het hele bord te detecteren. Een sensorsysteem nabij het bord meet de elektromagnetische ondertekening van geassembleerde componenten en tracés. Kortsluitingen veroorzaken meetbare capacitieve koppeling; open verbindingen tonen karakteristieke impedantie veranderingen. De methode is snel, niet-contact, en kan de aanwezigheid, polariteit en geschatte waarde van componenten afleiden, wat effectief is bij het opsporen van grote manufactuurfouten zoals ontbrekende componenten, omgekeerde diodes of overbrugde tracés.

Dekkingvergelijking: De cijfers achter de afweging

Het belangrijkste bezwaar tegen het afschaffen van ICT is de dekking. Hoewel ICT in principe elk knooppunt op een bord kan bereiken met voldoende testpunten, is de bewering dat alternatieven inferieur zijn onvolledig. De echte vraag is of zij voldoende dekking bereiken om de fouten die daadwerkelijk voorkomen te detecteren, en of een gerichte functionele test de resterende kloof kan dichten.

Wat Boundary Scan dekt

Boundary scan-dekking hangt af van hoeveel componenten op het bord voldoen aan de JTAG-standaard. Voor borden die gedomineerd worden door digitale logica—microprocessors, FPGAs, geheugen—is de dekking uitgebreid. De scan-keten kan de onderlinge verbinding tussen deze apparaten testen met foutdetectiepercentages die meer dan 95 procent overschrijden voor kortsluitingen, open verbindingen en stuck-at fouten. Een bord waarbij 80 procent van de componenten voldoen, bereikt ongeveer 70 tot 85 procent netto dekking. Analoge secties, discrete componenten en legacy-onderdelen zijn onzichtbaar voor deze methode. Echter, voor digitale zware ontwerpen biedt boundary scan alleen al dekking die vergelijkbaar is met ICT voor de onderlinge verbindinglaag, waar de meeste assemblagefouten voorkomen.

Wat Vectorless Testing Toevoegt

Vectorloos testen vult de hiaten op die boundary scan achterlaat, vooral voor passieve componenten en grove samenstellingsfouten. Capacitatieve metingen kunnen ontbrekende weerstanden, verkeerde condensatorwaarden en omgekeerde diodes detecteren. Hoewel minder precies dan de directe metingen van ICT, is het een effectieve screening voor de meest voorkomende fouten: verkeerd onderdeel, ontbrekend onderdeel of ernstige verkeerde uitlijning. Dit voegt nog eens 10 tot 20 procent toe aan de totale foutdekking, en biedt een niet-contact verificatielaag voor onderdelen die boundary scan niet kan zien.

De resterende kloof en hoe lean functioneel testen deze overbrugt

De combinatie van boundary scan en vectorloos testen laat nog steeds een kloof in functionele validatie en analoge prestaties. Een component kan aanwezig en correct verbonden zijn, maar toch niet binnen specificaties functioneren. Een stroomvoorziening kan voltage leveren, maar met overmatige ruis. Hier speelt een lean functionele circuittest (FCT) zijn rol. In tegenstelling tot een volledige ICT-opstelling, valideert een lean FCT dat het bord zijn bedoelde functie onder realistische omstandigheden uitvoert. Het levert stroom, stimuleert ingangen en meet uitgangen. Voor een motorcontroller kan het de generering van PWM-signalen verifiëren; voor een communicatiebord kan het foutloze gegevensoverdracht controleren. De functionele test vult de structurele tests aan, en vangt fouten op die andere methoden niet kunnen zien.

Deze drie methoden samen bereiken doorgaans 85 tot 95 procent foutdekking. Dit is niet 100 procent, maar ook ICT in de praktijk niet. Door testpuntbeperkingen en probe-wear ligt de werkelijke ICT-dekking vaak lager dan het theoretische maximum. Het verschil in dekking is veel kleiner dan de kosten- en doorlooptijdpenalty.

Het Debug Loop-voordeel

Testdekking is slechts de helft van de waarde-equatie; de andere helft is de snelheid en precisie van foutisolatie. Een test die een fout detecteert maar vage diagnostiek geeft, verhoogt de tijd en kosten die nodig zijn om de oorzaak te vinden.

Hoewel ICT uitstekend is in het signaleren van fouten, kunnen de diagnosticering frustrerend vaag zijn. Een tester kan rapporteren dat node 47 kortgesloten is op aarde, maar het legt niet uit waarom of waar precies. De technicus moet de schakeling traceren, de net vinden, en visueel de omgeving inspecteren — een proces dat uren kan kosten op een dicht, multi-laags bord.

Diagnostiek met boundary scan is fundamenteel anders. Omdat de scan-keten geïntegreerd is in de componenten, beperkt de test de fouten tot specifieke pinnen en apparaten. Een korte tussen twee netwerken wordt geïdentificeerd door de exacte apparaatpin involved, waardoor de zoektocht wordt beperkt tot een paar vierkante millimeters. Openingen worden gedetecteerd tussen specifieke driver- en ontvangerparen. De diagnostische output is geen foutcode. Het is een kaart. Deze precisie betekent dat een fout die een uur kost om te debuggen met ICT-gegevens vaak in 10 tot 20 minuten kan worden opgelost met boundary scan. Voor een productie van 100 eenheden met een typisch defectpercentage kan de totale besparing op debug-tijd meer dan 10 uur bedragen.

Lead Time en Flexibiliteit: De Verborgen Waarde

Het economische argument tegen ICT voor lage volumes is overtuigend, maar de vertraging door doorlooptijd is net zo belangrijk. Het proces van het ontwerpen van fixtures, dat twee tot vier weken duurt, legt een verplichte vertraging op tussen het vastleggen van het ontwerp en de testgereedheid. Voor de introductie van nieuwe producten, waar time-to-market cruciaal is, is deze vertraging vaak onaanvaardbaar.

Boundary scan en vectorloos testen elimineren deze wachttijd. De testopstelling kan in uren of dagen worden geconfigureerd, niet in weken, waardoor borden soepel van assemblage naar test en verzending kunnen gaan. Deze flexibiliteit is cruciaal wanneer ontwerpen itereren. Een vroege prototype-run kan problemen aan het licht brengen die layoutwijzigingen vereisen. Met ICT vereist elke revisie een nieuwe of herwerkte fixture, met daarmee gepaard gaande kosten en doorlooptijd. Boundary scan-testpatronen, gegenereerd vanuit de netlist, worden automatisch bijgewerkt met het ontwerp. Dit creëert een teststrategie die iteratieve ontwikkeling ondersteunt in plaats van bestraft.

Wanneer nog steeds Kiezen voor ICT

Maar het argument tegen low-volume ICT is niet absoluut. Bepaalde ontwerpen en productiecontexten rechtvaardigen nog steeds de investering.

Borden met hoog-dichtheid analoge of RF-secties zijn slechte kandidaten voor een puur fixtureloze strategie. Analoge componenten missen boundary scan-logica, en kritische prestatiekenmerken zoals gain of fase-ruis kunnen niet structureel worden geverifieerd. Als analoge of RF-circuits meer dan 40 procent van de functionaliteit van het bord uitmaken, wordt de zaak voor ICT aanzienlijk versterkt.

Voldoenheidsgerichte industrieën zoals medisch, ruimtevaart en automotive opereren vaak onder regels die specifieke testdekking of methoden vereisen. Als een geldende standaard in-circuit testen of equivalent node-level toegang vereist, zijn alternatieve strategieën mogelijk niet toereikend. Hier is de kostenpost van ICT een niet-onderhandelbare kostenpost voor markttoegang.

Tot slot verandert een duidelijke en vastbesloten route naar grootschalige productie de berekening. Als een eerste run van 150 eenheden wordt verwacht op te schalen tot 1.000 eenheden binnen zes maanden, wordt de fixturekost afgeschreven over het totale verwachte volume. Dit vereist hoog vertrouwen in de voorspelling en een stabiel ontwerp, maar het kan de initiële investering de moeite waard maken.

Het bouwen van de alternatieve teststrategie

Het vervangen van ICT is geen eenvoudige vervanging; het is een herconfiguratie van de testarchitectuur naar een gelaagde strategie, waarbij elke laag fouten opvangt die de andere mogelijk missen.

Het proces moet sequentieel verlopen. De eerste laag is boundary scan, die snel wordt uitgevoerd op alle compatibele apparaten om interconnectfouten in de digitale delen van het bord te vangen. Borden die falen, worden voor directe herwerking gemarkeerd, waardoor catastrophische fouten bij later gebruik worden voorkomen. De tweede laag is vectorloos testen, dat over het hele bord wordt uitgevoerd om ontbrekende of onjuiste passieve componenten, grove kortsluitingen en polariteitfouten op te sporen. Het dekt de componenten en nets die onzichtbaar zijn voor de scan-keten.

De derde en laatste laag is een gerichte functionele test. Met structurele fouten al geëlimineerd, wordt het bord ingeschakeld om kritieke functies te valideren onder realistische operationele omstandigheden. De scope is afgestemd op het doel van het bord — bijvoorbeeld het verifiëren van ADC-nauwkeurigheid op een data-acquisitiebord of spanningsregelingsfunctie op een voeding. Deze volgorde zorgt ervoor dat catastrophe fouten vroeg worden ontdekt en niet-destructief, waardoor debug-tijd voor de meer complexe functionele fouten wordt geminimaliseerd.

Voor borden met hybride complexiteit — bijvoorbeeld een dicht digitaal kernbord omgeven door analoge signaalconditionering — kan een hybride strategie het beste zijn. Een gedeeltelijke ICT-fixture kan worden ontworpen om alleen het kritische analytische gedeelte te testen, terwijl het digitale deel wordt overgelaten aan boundary scan. De economieën van een gedeeltelijke fixture zijn gunstiger, waardoor kosten en doorlooptijd worden verminderd, terwijl toch de benodigde dekking voor het hele ontwerp wordt geboden.