Na fabricação de alta confiabilidade, há um conforto perigoso na marca de verificação verde. Um lote de placas de cobre pesado para um inversor de tração EV sai da linha, passa na Inspeção Automatizada por Raio-X (AXI) e é enviado ao cliente. A papelada está impecável. Os requisitos da Classe 3 do IPC-A-610 — frequentemente reverenciados como o padrão ouro — foram cumpridos. No entanto, três meses depois, essas mesmas placas falham no campo, sofrendo ciclos térmicos até a morte porque os FETs de potência estão delaminando. A desconexão aqui não é uma falha da máquina em medir. É uma falha do padrão em levar em conta a física. Uma placa que é legalmente segura ainda pode estar fisicamente condenada.

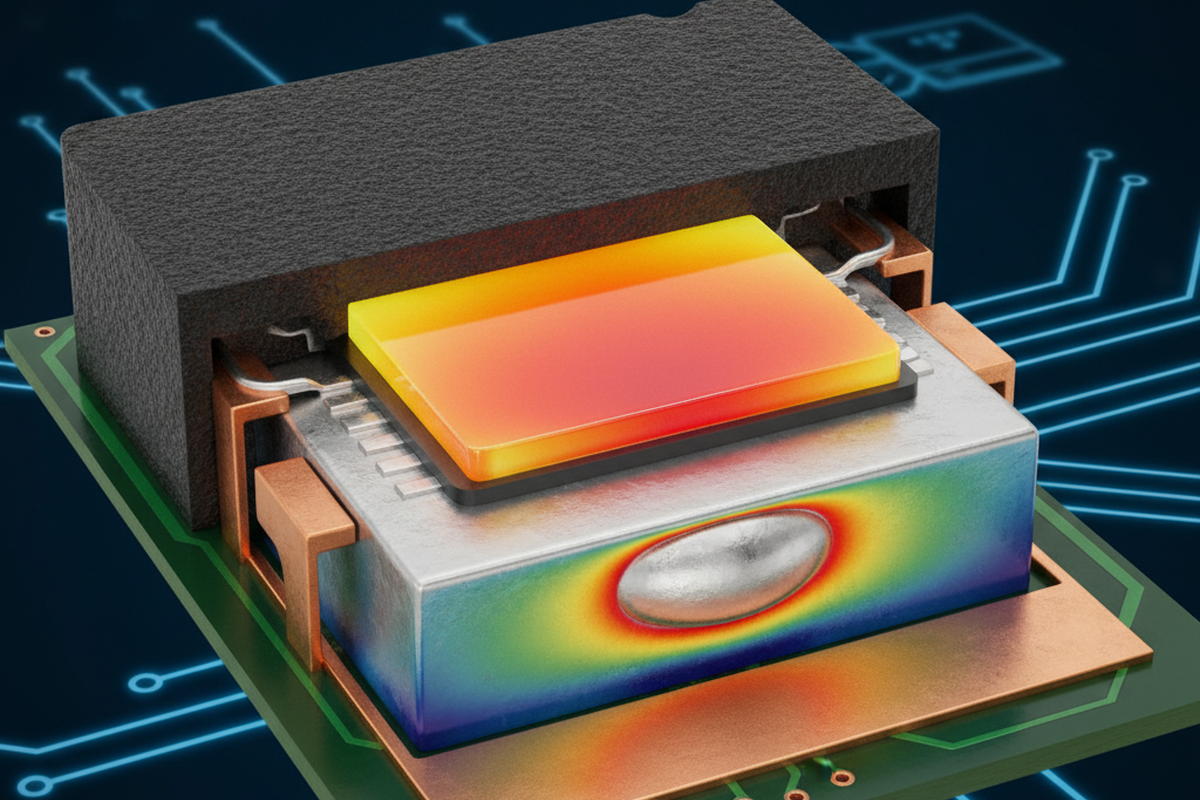

O problema muitas vezes está em como definimos uma junta de solda “boa” para componentes de potência. Algoritmos padrão de inspeção focam fortemente na porcentagem total de vazios — calculando o volume de gás preso na solda em relação à área total da almofada. Se a especificação permite 25% de vazios e a máquina mede 18%, a placa passa. Mas a termodinâmica não negocia pontos percentuais. Analisamos retornos de campo onde aquele “aceitável” 18% de vazios não estava disperso aleatoriamente; estava acumulado diretamente sob o ponto quente do chip de silício, atuando como um isolante térmico perfeito. O calor, incapaz de passar pelo vazio, elevou a temperatura da junção (Tj) muito além da área segura de operação. A porcentagem estava boa, mas a localização foi fatal.

O Problema da Terra Plana: Por Que o Raio-X 2D Perde o Ponto

Esses defeitos passam despercebidos em grande parte por causa das ferramentas usadas para classificá-los. Muitos fabricantes contratados ainda dependem de sistemas padrão de raio-X de transmissão 2D. Essas máquinas projetam raios-X através de toda a espessura da placa e capturam a sombra resultante em um detector. Embora adequadas para verificar curtos em um resistor simples, essa abordagem achata o mundo de um conjunto complexo de potência em um único plano. Em uma placa dupla face, componentes na parte inferior interferem na imagem da parte superior, criando uma imagem ruidosa e ambígua que os algoritmos têm dificuldade em interpretar.

O problema se agrava ao lidar com BGAs ou BTCs (Componentes de Terminação Inferior), onde a estrutura vertical da junta importa. Em uma imagem 2D, um vazio aparece como um ponto claro, mas a imagem não pode dizer onde esse vazio está posicionado verticalmente. É uma bolha inofensiva no volume da solda, ou é um “vazio planar” que essencialmente desconecta a interface do componente? Vimos casos diagnosticados erroneamente como “solda insuficiente” onde o vazio estava concentrado inteiramente na interface intermetálica, criando uma ligação mecânica fraca e um gargalo térmico. Sem capacidades 3D como Laminografia ou Tomografia Computadorizada (CT) para fatiar os dados em camadas, um inspetor está essencialmente adivinhando a integridade do caminho térmico. Você não pode classificar o que não pode ver em três dimensões.

Topologia Térmica: Localização é Mais Importante que Percentual

Quando o objetivo é a dissipação de calor, a topologia dos vazios importa infinitamente mais que o volume total. Pense no caminho térmico como uma rodovia para o calor, viajando do chip, através da fixação do chip, para o leadframe, pela junta de solda e finalmente para a almofada térmica e vias da PCB. Um vazio é um bloqueio na estrada. Se você tem dez pequenos vazios espalhados pela periferia de uma almofada térmica D2PAK, a “rodovia” ainda está aberta no centro, e o calor flui eficientemente da fonte. Esse cenário pode tecnicamente registrar 15% de vazios. Por outro lado, um único vazio grande centrado diretamente sob o chip pode registrar apenas 8% de vazios totais, mas bloqueia a rota arterial principal para o fluxo de calor.

Essa distinção é crítica para peças de alta densidade de potência como IGBTs ou LEDs de alta luminosidade. Em uma análise de postes de iluminação que falhavam prematuramente, as placas dos drivers mostraram níveis de vazios que tecnicamente passavam nos critérios padrão de inspeção. No entanto, a imagem térmica revelou temperaturas de junção subindo 30°C acima do limite de projeto. Os vazios agiam como “queijo suíço” na pior disposição possível, aumentando a impedância térmica ($R_{th}$) da junta. Claro, a junta de solda é apenas um elo na cadeia; se a superfície externa do dissipador não for plana ou o Material de Interface Térmica (TIM) estiver mal aplicado, uma junta de solda perfeita não salvará a placa. Mas como engenheiros de processo de PCBA, a interface de solda é a variável que controlamos. Garantir um caminho térmico contínuo é a única métrica que importa.

Uma Heurística de Classificação Melhor

Superar a mentalidade de “marcar caixa” requer uma estratégia de classificação baseada na continuidade térmica em vez de limites simples de vazios. Bester PCBA recomenda abandonar o “Aprovado/Reprovado” binário baseado em um único número percentual em favor de critérios de classificação baseados em zonas para almofadas de potência. Isso envolve definir uma “zona crítica” — tipicamente os 50% centrais da almofada térmica onde o chip está — e aplicar limites de vazios muito mais rigorosos nessa área específica, permitindo tolerâncias mais flexíveis na periferia.

Essa abordagem requer programação mais sofisticada dos equipamentos AXI, mas alinha os critérios de inspeção com a realidade física. Procuramos a “área de contato interfacial” — a quantidade de conexão garantida de solda diretamente sob a fonte de calor. Não existe um número mágico que se aplique a todo projeto; um chip lógico de baixa potência pode sobreviver com 40% de vazios, enquanto um transistor de potência GaN pode falhar com 10% se estiver no lugar errado. A classificação deve ser consciente do contexto. Se o algoritmo não puder ser ajustado a esse nível de nuance, os resultados da “área cinzenta” — placas que tecnicamente passam mas parecem suspeitas — devem ser sinalizados para revisão manual por um técnico que entenda o caminho térmico, em vez de serem aprovados automaticamente.

Prevenção na Fonte

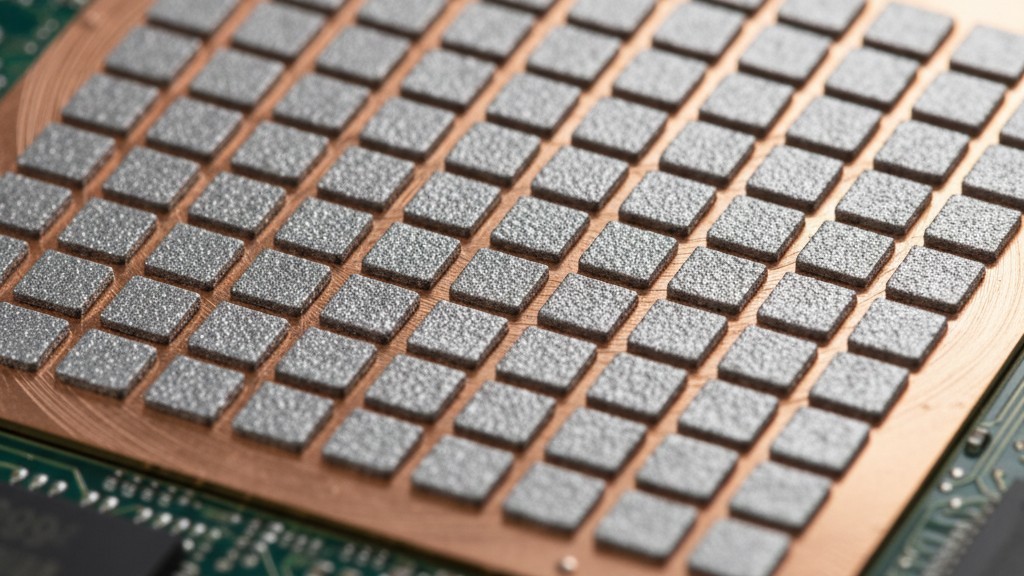

A melhor maneira de avaliar um vazio é preveni-lo de se formar em primeiro lugar. Altas contagens de vazios em pads térmicos raramente são acidentes aleatórios; geralmente são a assinatura de uma violação de processo ou design. O culpado mais comum é o design do estêncil. Uma abertura grande e aberta para um pad térmico QFN permite que muita pasta seja aplicada, que então libera gases durante o reflow. Se esse gás não tiver para onde escapar, forma um vazio gigante. A correção padrão é "window-paning" da abertura — dividir o grande quadrado em quadrados menores com espaços entre eles — para criar canais para os voláteis escaparem.

O design da placa PCB nua desempenha um papel igualmente importante. Frequentemente vemos projetistas colocando vias abertas e não preenchidas dentro do pad térmico. Durante o reflow, a gravidade e a ação capilar puxam a solda quente para dentro desses furos — um fenômeno conhecido como capilaridade da solda — deixando o componente flutuando sobre solda insuficiente. Isso leva a vazios massivos e conexão ruim. Se vias térmicas forem necessárias no pad, elas devem ser cobertas na parte traseira ou preenchidas e tampadas para evitar esse roubo de solda. Nenhuma quantidade de avaliação por raio-X pode consertar uma placa onde a solda fisicamente escorreu.

O Veredicto

Confiabilidade não é um certificado que você pendura na parede. É a capacidade física de um dispositivo sobreviver ao seu ambiente operacional. Seguir estritamente os limites de vazios da Classe IPC 2 ou 3 fornece uma proteção legal, mas não muda as leis da termodinâmica. Para eletrônica de potência, os critérios padrão de avaliação frequentemente são insuficientes. Ao mudar o foco de "percentual total de vazios" para "integridade do caminho térmico", e ao utilizar ferramentas de inspeção 3D que revelam a verdadeira estrutura da junta, podemos parar de enviar placas destinadas a queimar. O custo de uma inspeção mais rigorosa é sempre menor que o custo de um recall.