A pressão para identificar falhas de fabricação antes que as placas sejam enviadas é inegociável. Um único defeito escapado em um sistema crítico pode custar exponencialmente mais do que os testes que o detectariam. Essa realidade leva muitas equipes de engenharia a adotarem o teste em circuito (ICT) como padrão, um método há muito considerado o padrão-ouro para cobertura. O ICT completo oferece acesso abrangente a quase todos os nós de uma placa, prometendo taxas de detecção de falhas que se aproximam do máximo teórico. Para produção de grande volume, o investimento faz sentido; os custos fixos de engenharia de fixture e equipamentos de teste são amortizados em milhares de unidades, reduzindo a carga por unidade a níveis negligenciáveis.

Mas a economia muda quando os volumes de produção caem. Para produções abaixo de algumas centenas de unidades, as próprias vantagens do ICT tornam-se responsabilidades. A fixture personalizada necessária para cada projeto de placa possui um custo fixo de engenharia elevado que não escala. Os tempos de lead se estendem enquanto as fixtures são projetadas, construídas e depuradas. As iterações de design, comuns na introdução de novos produtos, invalidam as fixtures completamente, forçando o ciclo a recomeçar. Na Bester PCBA, testemunhamos essa matemática se desenrolar em centenas de projetos. Para lotes abaixo de 200 a 300 unidades, o ICT completo raramente paga seu custo.

A alternativa não é abandonar testes rigorosos, mas substituir o modelo dependente de fixture por uma estratégia mais enxuta e rápida, baseada em boundary scan, testes sem vetores e testes funcionais focados. Essa combinação oferece uma cobertura de falhas comparável, elimina o gargalo da fixture e proporciona um ciclo de depuração mais rápido quando falhas são encontradas. Essa mudança não é ideológica; é uma resposta prática à fricção matemática e mecânica que o ICT impõe a uma produção de baixo volume e ágil.

A Suposição ICT e Onde Ela Fracassa

O teste em circuito tornou-se o padrão da indústria em uma era de designs de alto volume e estabilidade. O modelo era simples: investir pesadamente inicialmente em uma fixture de teste personalizada e em um testador sofisticado, depois aproveitar esse investimento em dezenas de milhares de unidades idênticas. Com tempos de teste por unidade medidos em segundos, o custo marginal por placa era efetivamente zero após a absorção dos custos fixos. Para um fabricante de eletrônicos de consumo produzindo 50.000 unidades do mesmo SKU, a matemática era inquestionável.

Esse modelo de produção se quebrou. A fabricação moderna de eletrônicos atende cada vez mais a mercados com alto mix e baixo volume. Ciclos de vida de produto mais curtos, iterações de design mais frequentes e personalização como vantagem competitiva. Uma empresa pode produzir 150 unidades de uma variante, iterar o design e depois produzir 200 da próxima. A suposição de que uma única fixture testará milhares de placas idênticas não é mais válida. Os custos fixos que eram negligenciáveis em altos volumes tornam-se punitivos quando distribuídos por algumas centenas de unidades.

O modelo quebra onde o custo total da infraestrutura ICT ultrapassa o custo ajustado ao risco de estratégias alternativas. Esse limite não é arbitrário. É uma função do custo da fixture, do tempo de engenharia, do prazo de produção e da cobertura alcançável por métodos sem fixture. Para a maioria dos projetos de placa, esse limite fica entre 200 e 300 unidades.

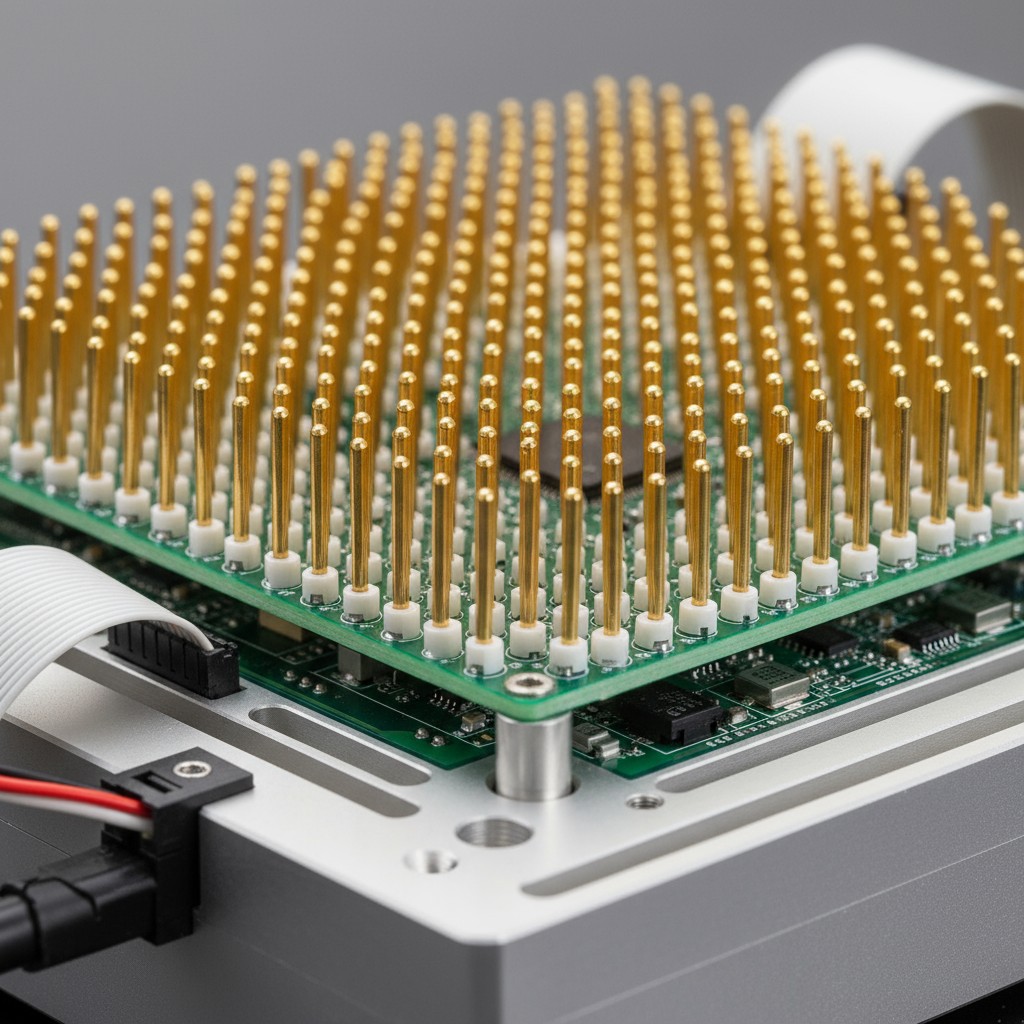

A Armadilha do Custo Fixo dos Testes em Circuito

Embora a fixture seja o custo mais visível do ICT, o peso econômico real é muito mais amplo. Uma fixture ICT personalizada não é uma compra de prateleira; é um artefato engenheirado, projetado especificamente para um layout de placa. O processo de design requer traduzir a netlist e a disposição dos componentes da placa em uma estrutura mecânica munida de sondas de teste com mola, cada uma alinhada a um ponto de teste específico com precisão de sub-milimétrica. A fixture deve levar em conta tolerâncias de componentes, deformações da placa e desgaste das sondas. Depois, deve ser validada e depurada — um processo que frequentemente revela problemas imprevistos com o acesso às sondas ou integridade do sinal.

Custos de Engenharia das Fixtures e Tempos de Lead

O custo de engenharia para uma fixação moderadamente complexa normalmente fica entre $8.000 e $15.000. Placas de alta densidade com componentes de passo fino ou acesso limitado a pontos de teste podem elevar essa cifra para $25.000 ou mais. Isso é puramente o custo da interface mecânica e elétrica personalizada necessária para conectar a placa ao equipamento ICT, separado da despesa de capital do próprio testador.

O tempo de espera é igualmente importante. Desde o momento em que um projeto de placa é finalizado, o design e a fabricação do fixture normalmente requerem de duas a quatro semanas, estendendo-se até seis para projetos complexos. Durante esse período, a produção fica paralisada. As placas podem ser montadas, mas não podem ser testadas. Elas ficam em estoque, esperando. Se o projeto mudar durante esse período—uma ocorrência comum na introdução de novos produtos—o fixture deve ser revisado ou descartado. O relógio reinicia.

A Matemática do Ponto de Equilíbrio para Produções em Baixo Volume

A armadilha econômica fica clara quando os custos do fixture são divididos pelo número de unidades. Um fixture de $12.000 para uma produção de 100 unidades adiciona uma carga de $120 a cada placa. Para uma placa com uma lista de materiais de $500, isso representa uma sobrecarga de teste de 24%. Mesmo se o processo ICT for rápido, a eficiência econômica é baixa. O mesmo fixture amortizado sobre 500 unidades reduz o custo por unidade para $24, uma sobrecarga de cinco por cento muito mais aceitável. A diferença é puramente uma função de volume.

O ponto de equilíbrio é onde o custo total do ICT—incluindo engenharia, configuração e o custo de oportunidade do tempo de espera—iguala-se ao custo de uma alternativa sem fixture. Para uma estratégia que combina escaneamento de limite, teste sem vetor e um teste funcional enxuto, o custo de infraestrutura é drasticamente menor. O escaneamento de limite não requer fixture, e o teste sem vetor usa sensores reutilizáveis que funcionam sem contato mecânico. Qualquer fixture de teste funcional é tipicamente mínimo e genérico, não um artefato específico de placa que requer semanas de engenharia.

Em volumes de produção abaixo de 200 unidades, a economia do ICT entra em colapso. Abaixo de 300 unidades, o caso é marginal, dependendo da complexidade da placa. Apenas acima de 300 unidades para projetos estáveis, não iterativos, o ICT começa a fazer sentido econômico novamente.

O que São o Boundary Scan e o Teste Sem Vetores na Verdade

A alternativa aos testes baseados em fixtures não é um compromisso com o rigor, mas uma mudança para métodos que aproveitam a infraestrutura de design existente e medição sem contato. Essas ferramentas foram desenvolvidas para enfrentar a mesma tendência que enfraquece a TIC: aumento da densidade da placa e redução do acesso a pontos de teste físicos.

O escaneamento de limite, formalizado na norma IEEE 1149.1 (comumente conhecido como JTAG), incorpora a lógica de teste diretamente nos circuitos integrados de uma placa. Chips compatíveis incluem uma cadeia de células em cada pino de entrada e saída. Durante um teste, uma interface de quatro fios transfere padrões para essas células, controlando os estados lógicos nas redes da placa. Os estados resultantes são capturados e deslocados para fora para análise, permitindo que o testador controle e observe sinais no nível de pino sem contato físico. Este método não invasivo é altamente eficaz na detecção de curtos, abertos e falhas grudadas entre dispositivos compatíveis.

O teste sem vetor complementa isso usando medições capacitivas e indutivas para detectar falhas em toda a placa. Um array de sensores posicionado perto da placa mede a assinatura eletromagnética de componentes e trilhas montados. Curto-circuitos criam acoplamento capacitivo mensurável; aberturas mostram mudanças características na impedância. O método é rápido, sem contato e pode inferir a presença, polaridade e valor aproximado de componentes, tornando-se eficaz na captura de defeitos de fabricação grosseiros, como componentes ausentes, diodos invertidos ou trilhas bridgadas.

Comparação de Cobertura: Os Números por Trás do Compromisso

A objeção principal ao abandono do ICT é a cobertura. Embora o ICT possa, em princípio, acessar todos os nós de uma placa com pontos de teste suficientes, a alegação de que alternativas são inferiores está incompleta. A questão real é se elas atingem cobertura suficiente para detectar as falhas que realmente ocorrem, e se um teste funcional focado pode fechar a lacuna restante.

O que a verificação de limite cobre

A cobertura de varredura de limite depende de quantos componentes na placa são compatíveis com o padrão JTAG. Para placas dominadas por lógica digital—microprocessadores, FPGAs, memória—a cobertura é extensa. A cadeia de varredura pode testar a interconexão entre esses dispositivos com taxas de detecção de falhas superiores a 95 por cento para curtos, aberturas e falhas de stuck-at. Uma placa onde 80 por cento dos componentes são compatíveis alcançará aproximadamente 70 a 85 por cento de cobertura líquida. Secções analógicas, componentes discretos e peças legadas são invisíveis a este método. No entanto, para projetos de alta digitalidade, a varredura de limite por si só entrega uma cobertura comparável à ICT para a camada de interconexão, onde ocorrem a maioria das falhas de montagem.

O que o Teste Sem Vetores Adiciona

Testes sem vetores preenchem as lacunas deixadas pela varredura de limite, particularmente para componentes passivos e defeitos grosseiros de montagem. Medições capacitivas podem detectar resistores ausentes, valores incorretos de capacitores e diodos invertidos. Embora menos precisas do que as medições diretas do ICT, elas são uma camada de verificação eficaz para os erros mais comuns: componente errado, componente ausente ou desalinhamento severo. Isso acrescenta de 10 a 20 por cento à cobertura total de falhas, fornecendo uma camada de verificação sem contato para peças que a varredura de limite não consegue detectar.

A Lacuna Restante e Como o Teste Funcional Enxuto a Fecha

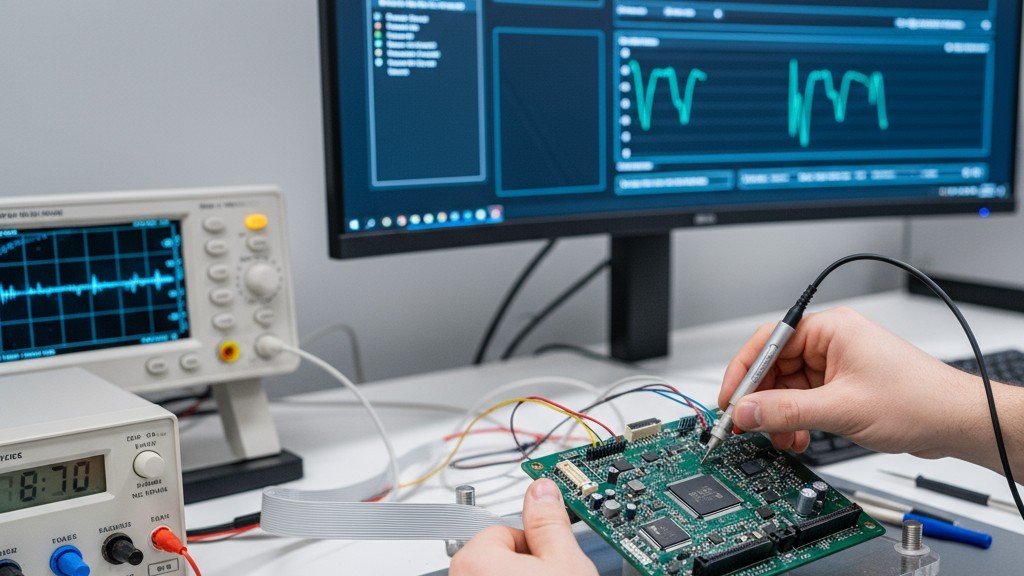

A combinação de escaneamento de limite e teste sem vetor ainda deixa uma lacuna na validação funcional e no desempenho analógico. Um componente pode estar presente e conectado corretamente, mas ainda assim falhar em operar dentro das especificações. Uma fonte de alimentação pode fornecer tensão, mas com ruído excessivo. É aqui que um teste de circuito funcional enxuto (FCT) desempenha seu papel. Diferentemente de uma configuração completa de ICT, um FCT enxuto valida se a placa realiza sua função pretendida sob condições realísticas. Ele fornece energia, estimula entradas e mede saídas. Para um controlador de motor, pode verificar a geração de sinal PWM; para uma placa de comunicação, pode verificar a transmissão de dados sem erros. O teste funcional complementa os testes estruturais, capturando falhas que outros métodos não conseguem detectar.

Combinados, esses três métodos geralmente alcançam de 85 a 95 por cento de cobertura de falhas. Isso não é 100 por cento, mas tampouco o ICT na prática. Devido às limitações nos pontos de teste e ao desgaste da sonda, a cobertura real do ICT muitas vezes fica aquém de seu máximo teórico. A diferença na cobertura é muito menor do que a penalidade em custo e tempo de entrega.

A Vantagem do Ciclo de Depuração

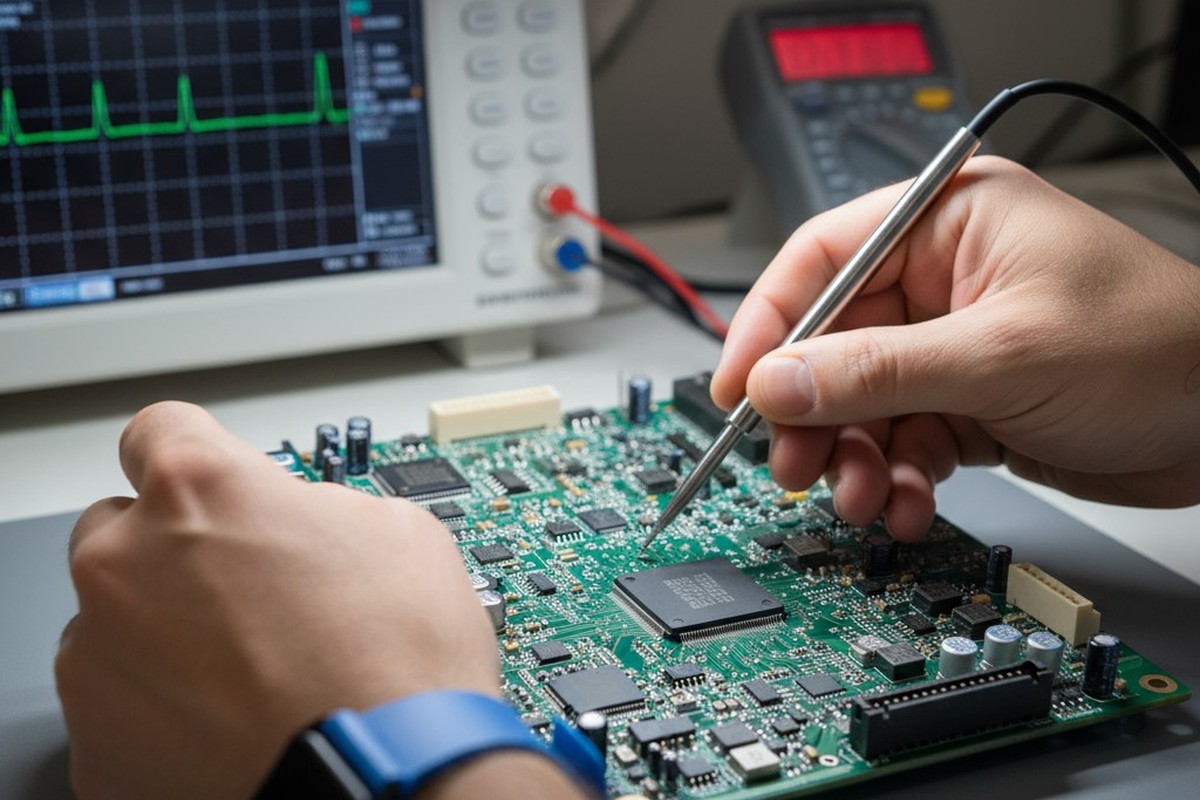

A cobertura do teste é apenas metade da equação do valor; a outra metade é a velocidade e precisão do isolamento de falhas. Um teste que detecta uma falha, mas fornece diagnósticos vagos, aumenta o tempo e o custo necessários para encontrar a causa raiz.

Embora o ICT seja excelente em sinalizar falhas, seus diagnósticos podem ser frustrantemente vagos. Um testador pode relatar que o nó 47 está encurtado ao terra, mas não explica o porquê ou onde. O técnico precisa rastrear o esquema, localizar a rede e inspecionar visualmente a área—um processo que pode consumir horas em uma placa densa e multilayer.

As varreduras de diagnóstico por boundary scan são fundamentalmente diferentes. Como a cadeia de varredura está embutida nos componentes, o teste isola falhas em pinos e dispositivos específicos. Um curto entre dois condutores é identificado pelos pinos exatos do dispositivo envolvidos, restringindo a busca a alguns milímetros quadrados. Aberturas são detectadas entre pares específicos de driver e receptor. A saída do diagnóstico não é um código de falha. É um mapa. Essa precisão significa que uma falha que leva uma hora para ser depurada com dados de ICT pode muitas vezes ser resolvida em 10 a 20 minutos com boundary scan. Para uma produção de 100 unidades com uma taxa de defeito típica, o tempo cumulativo de depuração economizado pode exceder 10 horas.

Tempo de Lead e Flexibilidade: O Valor Oculto

O argumento econômico contra ICT para baixos volumes é convincente, mas a penalidade de tempo de lead é igualmente significativa. O processo de engenharia do fixture de duas a quatro semanas impõe um atraso obrigatório entre o congelamento do projeto e a preparação para o teste. Para a introdução de novos produtos, onde o tempo para o mercado é crítico, esse atraso muitas vezes é inaceitável.

Boundary scan e testes sem vetores eliminam essa espera. A configuração do teste pode ser feita em horas ou dias, não em semanas, permitindo que as placas avancem de montagem para teste para envio em um fluxo contínuo. Essa flexibilidade é crucial quando os projetos iteram. Uma primeira rodada de protótipo pode revelar problemas que exigem alterações no layout da placa. Com ICT, cada revisão exige um novo fixture ou um fixture refeito, incurando custos e tempo de lead novamente. Os padrões de teste de boundary scan, gerados a partir da netlist, são atualizados automaticamente com o projeto. Isso cria uma estratégia de teste que apoia o desenvolvimento iterativo, em vez de penalizá-lo.

Quando ainda escolher ICT

Mas o argumento contra ICT de baixo volume não é absoluto. Certos projetos e contextos de produção ainda justificam o investimento.

Placas com seções analógicas ou RF de alta densidade são más candidatas para uma estratégia puramente sem fixture. Componentes analógicos não possuem lógica de boundary scan, e características críticas de desempenho como ganho ou ruído de fase não podem ser verificadas estruturalmente. Se o circuito analógico ou RF representa mais de 40 por cento da funcionalidade da placa, o argumento a favor de ICT se fortalece consideravelmente.

Indústrias impulsionadas por conformidade, como médica, aeroespacial e automotiva, frequentemente operam sob regulamentações que exigem cobertura ou métodos específicos de teste. Se uma norma reguladora requer testes in-circuit ou acesso equivalente ao nível de nó, estratégias alternativas podem não ser suficientes. Aqui, o custo do ICT é um custo inegociável de entrada no mercado.

Finalmente, um caminho claro e comprometido para a produção de alto volume muda os cálculos. Se uma primeira produção de 150 unidades for projetada para escalar para 1.000 unidades em seis meses, o custo do fixture é amortizado ao longo do volume total esperado. Isso exige alta confiança na previsão e um projeto estável, mas pode tornar o investimento inicial justificado.

Construindo a Estratégia de Teste Alternativa

Substituir ICT não é uma troca simples; é uma reconfiguração da arquitetura de teste em uma estratégia em camadas, onde cada camada captura falhas que as outras poderiam perder.

O processo deve ser sequencial. A primeira camada é boundary scan, que roda rapidamente em todos os dispositivos compatíveis para detectar falhas de interconexão nas partes digitais da placa. As placas que falham são sinalizadas para retrabalho imediato, evitando falhas catastróficas quando a energia é aplicada posteriormente. A segunda camada é teste sem vetores, que roda por toda a placa para detectar componentes passivos ausentes ou incorretos, curtos grosseiros e erros de polaridade. Ela cobre os componentes e redes invisíveis à cadeia de varredura.

A terceira e última camada é um teste funcional focado. Com as falhas estruturais já filtradas, a placa é ligada para validar suas funções críticas sob condições realistas de operação. O escopo é ajustado ao propósito da placa — verificando a precisão do ADC em uma placa de aquisição de dados ou a regulação de carga em uma fonte de alimentação. Essa sequência garante que falhas catastróficas sejam detectadas precocemente e de forma não destrutiva, minimizando o tempo de depuração nas falhas funcionais mais complexas.

Para placas com complexidade híbrida — por exemplo, um núcleo digital denso cercado por condicionamento de sinal analógico — uma estratégia híbrida pode ser a melhor. Um fixture parcial de ICT pode ser projetado para sondar apenas a seção analógica crítica, deixando a parte digital para boundary scan. A economia de um fixture parcial é mais favorável, reduzindo custos e tempo de lead, ao mesmo tempo em que fornece a cobertura necessária para todo o projeto.