Давление поймать производственные дефекты до отгрузки плат — это неотъемлемо. Единственный уклонённый дефект в критической системе может стоить ощутимо больше, чем тестирование, которое его обнаружило бы. Эта реальность побуждает многие инженерные команды использовать тестирование в цепи (ICT) по умолчанию, метод, давно признанный золотым стандартом по покрытию. Полное ICT обеспечивает всесторонний доступ почти ко всем узлам на плате, обещая показатели обнаружения дефектов, приближающиеся к теоретическому максимуму. Для производства в больших объемах инвестиции оправданы; фиксированные затраты на разработку приспособлений и тестовое оборудование амортизируются за тысячи единиц, снижая нагрузку на каждую единицу до ничтожных уровней.

Но экономика меняется при снижении объёмов производства. Для партий менее нескольких сотен устройств, преимущества ICT становятся недостатками. Заказное приспособление, необходимое для каждого проекта платы, требует больших фиксированных затрат на инженерию, которые не масштабируются. Время выполнения растёт по мере разработки, сборки и отладки приспособлений. Итерации дизайна, распространённые при внедрении новых продуктов, полностью аннулируют эффективность приспособлений, заставляя цикл начинать заново. В компании Bester PCBA мы наблюдали, как эти расчёты реализуются на сотнях проектов. Для партий менее 200-300 устройств полное ICT редко оправдывает свои затраты.

Альтернатива — не отказаться от строгого тестирования, а заменить модель, основанную на приспособлениях, более рациональной и быстрой стратегией, основанной на границевом сканировании, тестировании без векторов и сосредоточенном функциональном тестировании. Эта комбинация обеспечивает сопоставимое покрытие дефектов, устраняет узкое место в приспособлениях и обеспечивает более быстрый цикл отладки при обнаружении дефектов. Этот переход не идеологичен; это практический ответ на математическое и механическое трение, которое ICT накладывает на малые серии и гибкое производство.

Допущение ICT и его прерывания

В цепное тестирование стало стандартом отрасли в эпоху массового, стабильного проектирования. Модель была проста: вкладывайте крупные суммы вначале в индивидуальное приспособление и сложное тестовое оборудование, а затем используйте эти инвестиции для производства десятков тысяч одинаковых устройств. При времени тестирования на единицу в секундах, переменные издержки на плату были практически нулевыми после покрытия фиксированных затрат. Для производителя потребительской электроники, выпускающего 50 000 единиц одного товарного знака, математика была неоспоримой.

Эта производственная модель сломалась. Современное производство электроники всё чаще обслуживает рынки с высоким ассортиментом и низкими объемами. Сроки жизни продуктов короче, итерации дизайна — чаще, а настройка на заказ — конкурентное преимущество. Компания может выпускать 150 единиц одного варианта, менять дизайн, а потом производить 200 другого. Предположение, что одно приспособление будет тестировать тысячи одинаковых плат, больше не работает. Фиксированные затраты, которые были пренебрежимо малы при больших объёмах, становятся обременительными при нескольких сотнях единиц.

Модель прерывается там, где общая стоимость инфраструктуры ICT превышает риск-скорректированную стоимость альтернативных стратегий. Этот порог не произволен. Он зависит от стоимости приспособления, времени инженеринга, времени производства и охвата, достигаемого методами без приспособлений. Для большинства проектов плат этот порог находится между 200 и 300 единицами.

Ловушка фиксированных затрат при тестировании в цепи

Хотя приспособление — самая заметная статья расходов ICT, настоящие экономические издержки гораздо шире. Индивидуальное приспособление для ICT — это не готовый товар; это инженерный артефакт, специально созданный под конкретную компоновку платы. Процесс проектирования включает в себя перевод сетевого списка и размещения компонентов в механическую структуру с пружинящими тестовыми зондами, каждый из которых точно выровнен по конкретной точке тестирования с точностью менее миллиметра. Приспособление должно учитывать допуски компонентов, деформацию платы и износ зондов. Затем оно должно пройти проверку и отладку — процесс, который часто выявляет неожиданные проблемы с доступом к зонтам или целостностью сигнала.

Затраты на проектирование приспособлений и сроки их изготовления

Инженерные расходы на изготовление относительно сложного приспособления обычно составляют от $8 000 до $15 000. Высокоплотные платы с тонкоп pitch компонентами или ограниченным доступом к тестовым точкам могут поднять эту сумму до $25 000 и выше. Это чисто стоимость индивидуального механического и электрического интерфейса, необходимого для соединения платы с оборудованием ICT, не считая капитальных затрат на тестер.

Время выполнения также имеет большое значение. С момента завершения проектирования платы обычно требуется от двух до четырёх недель на разработку и изготовление приспособления, а при сложных дизайнах — до шести. В этот период производство приостановлено. Платы могут быть собраны, но не могут пройти тестирование. Они находятся на складе в ожидании. Если дизайн изменится в этот период — что часто случается при запуске новых продуктов — приспособление должно быть пересмотрено или выброшено. Время сбрасывается.

Экономическая точка безубыточности для небольших серий

Экономическая ловушка становится очевидной, когда стоимость приспособления делится на количество единиц. Приспособление стоимостью $12 000 для серии из 100 штук вносит нагрузку в $120 на каждую плату. Для платы с стоимостью материалов $500 это составляет 24 процента накладных расходов на тестирование. Даже если процесс ICT быстрый, экономическая эффективность низкая. Тот же самый инструмент, распределённый на 500 единиц, снижает себестоимость до $24 за единицу, что гораздо более приемлемо — пятитеневой накладной расход. Разница зависит только от объёма производства.

Точка безубыточности — это тот момент, когда общие затраты на ICT — включая инженерные работы, подготовку и альтернативные затраты времени — равны стоимости безинструментальной альтернативы. Для стратегии, сочетающей пограничный сканинг, безвекторное тестирование и легкий функциональный тест, инфраструктурные затраты значительно ниже. Пограничное сканирование не требует приспособления, а безвекторное тестирование использует многоразовые сенсоры, работающие без механического контакта. Любое функциональное тестовое приспособление обычно минимально и универсально, а не является платой-артефактом, требующим нескольких недель инженерных работ.

При объёмах производства менее 200 единиц эффективность ICT падает. При менее чем 300 единицах ситуация несколько сомнительна и зависит от сложности платы. Только при более чем 300 единицах для стабильных, не итеративных дизайнов ICT снова становится экономически оправданным.

Что такое пограничное сканирование и векторное тестирование на самом деле

Альтернативой тестированию на основе фикстур является не компромисс в строгом соблюдении требований, а переход к методам, использующим существующую инфраструктуру дизайна и бесконтактные измерения. Эти инструменты были разработаны для решения той же проблемы, которая подрывает ИКТ: увеличение плотности платы и сокращение доступа к физическим точкам тестирования.

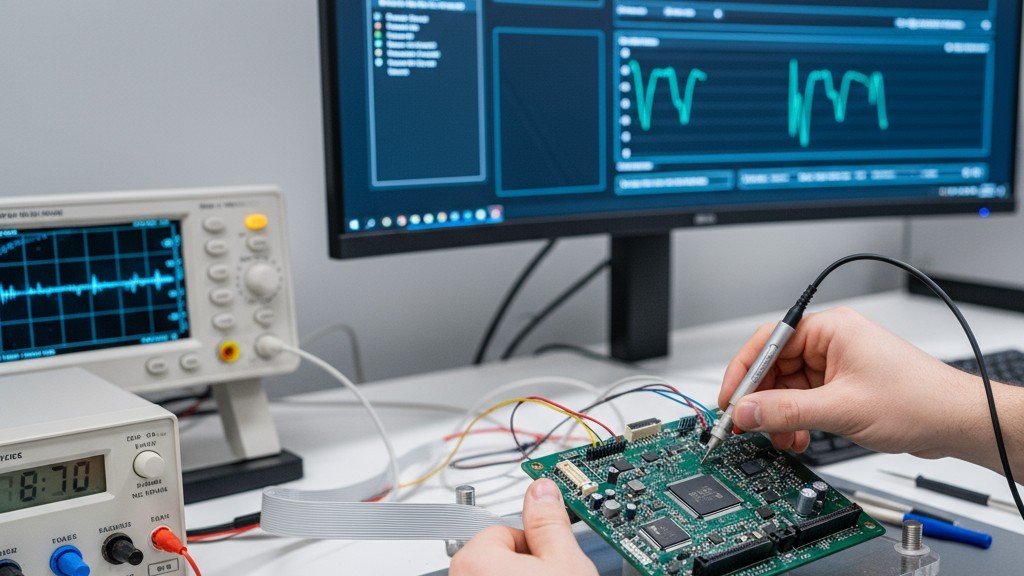

Пограничное сканирование, формализованное в стандарте IEEE 1149.1 (часто называемом JTAG), внедряет тестовую логику прямо в интегральные схемы платы. Совместимые чипы включают цепочку ячеек на каждом входе и выходе. Во время теста четыре провода через простое интерфейсное соединение передают паттерны в эти ячейки, контролируя логические состояния на сетях платы. Полученные состояния захватываются и передаются для анализа, позволяя тестеру управлять и наблюдать сигналы на уровне выводов без физического контакта. Этот неинвазивный метод очень эффективен для обнаружения коротких замыканий, разрывов и зависших-в-месте неисправностей между совместимыми устройствами.

Безвекторное тестирование дополняет это, используя емкостные и индуктивные измерения для обнаружения дефектов по всей плате. Массив датчиков, расположенный рядом с платой, измеряет электромагнитную сигнатуру собранных компонентов и трасс. Короткие замыкания создают измеримую емкостную связь; разрывы показывают характерные изменения импеданса. Метод быстр, безконтактный и может определять наличие компонентов, полярность и примерное значение, что делает его эффективным в обнаружении грубых производственных дефектов, таких как отсутствующие компоненты, перепутанные диоды или мости на трассах.

Сравнение охвата: цифры, стоящие за компромиссом

Основное возражение против отказа от ICT — это охват. В то время как ICT в принципе может получить доступ к каждой точке на плате, достаточно тестовых точек, утверждение, что альтернативы хуже, неполно. Важный вопрос — достигают ли они достаточного охвата, чтобы уловить фактические дефекты, и может ли узконаправленный функциональный тест закрыть оставшуюся непокрытую часть.

Что покрывает граничное сканирование

Покрытие пограничного сканирования зависит от того, сколько компонентов на плате соответствуют стандарту JTAG. Для плат, покрываемых в основном цифровой логикой — микропроцессорами, FPGA, памятью — покрытие обширное. Цепочка сканирования может тестировать межсоединения между этими устройствами с уровнем обнаружения неисправностей свыше 95 процентов для замыканий, разрывов и застрявших состояний. Плата, где 80 процентов компонентов соответствуют стандарту, достигнет примерно 70-85 процентов чистого покрытия. Аналоговые секции, дискретные компоненты и устаревшие части не видимы для этого метода. Однако для проектов, насыщенных цифровой логикой, пограничное сканирование само по себе обеспечивает покрытие, сравнимое с ICT, для слоя межсоединений, где происходят большинство ошибок сборки.

Что добавляет тестирование без векторов

Тестирование без векторов заполняет пробелы, оставшиеся после сканирования границ, особенно для пассивных компонентов и грубых дефектов сборки. Измерения емкости могут обнаружить отсутствующие резисторы, неправильные значения конденсаторов и обратные диоды. Хотя это менее точно, чем прямые измерения ICT, это эффективное средство обнаружения наиболее распространенных ошибок: неправильный компонент, отсутствующий компонент или тяжелое неправильное выравнивание. Это добавляет еще 10-20 процентов к общему охвату дефектов, обеспечивая слой неконтактной проверки для деталей, которые не видны при сканировании границ.

Оставшаяся пропасть и как узконаправленный функциональный тест её закрывает

Комбинация пограничного сканирования и безвекторного тестирования всё ещё оставляет разрыв в функциональной проверке и аналоговой производительности. Компонент может быть присутствует и подключён правильно, но всё равно не работать в соответствии со спецификациями. Источник питания может выдавать напряжение, но с чрезмерными колебаниями. Здесь играет свою роль узконаправленный функциональный тест (FCT). В отличие от полного набора ICT, узконаправленный FCT проверяет, работает ли плата в соответствии со своим предназначением при реалистичных условиях. Он подает питание, стимулирует входы и измеряет выходы. Для мотора это может быть проверка генерации сигнала PWM; для коммуникационной платы — проверка передачи данных без ошибок. Функциональный тест дополняет структурные тесты, выявляя дефекты, которые другие методы не могут заметить.

В совокупности эти три метода обычно достигают от 85 до 95 процентов охвата дефектов. Это не 100 процентов, но и ICT в практике не достигает его. Из-за ограничений тестовых точек и износа зондов реальное покрытие ICT часто уступает теоретическому максимуму. Разница в охвате значительно меньше, чем штраф за стоимость и сроки.

Преимущества цикла отладки

Покрытие тестом — только половина ценностной составляющей; другой аспект — скорость и точность локализации дефекта. Тест, обнаруживающий дефект, но дающий размытые диагностики, увеличивает время и затраты на поиск причины.

Хотя ICT отлично выявляет дефекты, его диагностика может быть довольно размыта. Тестер могут сообщить, что узел 47 замкнут на землю, но не объяснить почему или где именно. Техник должен проследить схему, найти сеть и визуально осмотреть область — процесс, который может занимать часы на плотной многослойной плате.

Диагностика границового сканирования принципиально отличается. Поскольку цепь сканирования встроена в компоненты, тест локализует неисправности до конкретных контактов и устройств. Короткое замыкание между двумя сетями определяется по точным контактам устройства, сокращая поиск до нескольких квадратных миллиметров. Открытые цепи обнаруживаются между конкретными парами драйверов и приемников. Выходной сигнал диагностики — не код ошибки, а карта. Эта точность означает, что неисправность, которую при отладке ICT можно было бы устранить за час, с помощью границового сканирования может быть решена за 10-20 минут. При запуске 100 единиц с типичной частотой дефектов суммарное время отладки, которое удастся сэкономить, может превысить 10 часов.

Время выполнения и гибкость: скрытая ценность

Экономический аргумент против ICT при малых тиражах убедителен, но штраф за время ожидания так же значителен. Процесс инженерных работ с фиксатором, рассчитанный на два-четыре недели, вводит обязательную задержку между заморозкой проекта и готовностью к тестированию. При выводе новых продуктов на рынок, где критически важно время выхода, эта задержка часто неприемлема.

Границовое сканирование и тестирование без векторов устраняют эту задержку. Настройка теста может быть выполнена за часы или дни, а не за недели, позволяя платам проходить от сборки к тестированию и отгрузке в непрерывном потоке. Эта гибкость особенно важна при итерациях разработки. Ранний прототип может выявить проблемы, требующие изменений в расположении элементов на плате. С ICT каждое изменение требует новой или переделанной фиксации, что снова влечет за собой затраты и сроки. Тестовые схемы границового сканирования, генерируемые из netlist, автоматически обновляются вместе с дизайном. Это создает стратегию тестирования, которая поддерживает итеративную разработку, а не мешает ей.

Когда всё ещё выбирают ICT

Но аргумент против маломасштабного ICT не является абсолютным. Некоторые дизайны и производственные контексты все еще оправдывают инвестиции.

Платины с высокой плотностью аналоговых или RF-секций плохо подходят для полностью фиксационного подхода. Аналоговые компоненты не имеют логики границового сканирования, и важные характеристики, такие как коэффициент усиления или фазовой шум, не могут быть проверены структурно. Если аналоговая или RF-ц circuitry составляет более 40 процентов функциональности платы, аргумент в пользу ICT значительно усиливается.

Индустрии, регулируемые требования, такие как медицина, аэрокосмическая промышленность и автомобильная промышленность, часто действуют в рамках правил, требующих конкретного охвата тестами или методов. Если стандарт требует ин-кит-тестирования или эквивалентного доступа на уровне узлов, альтернативные стратегии могут оказаться недостаточными. В таких случаях стоимость ICT является неизбежной платой за выход на рынок.

Наконец, ясный и решительный путь к производству большого объема меняет все расчеты. Если первоначальный запуск из 150 единиц ожидается масштабировать до 1000 за шесть месяцев, стоимость фиксатора распределяется на весь предполагаемый объем. Это требует высокого доверия к прогнозу и стабильного дизайна, но может сделать первоначальные инвестиции оправданными.

Создание альтернативной стратегии тестирования

Замена ICT — это не просто простая замена; это переустановка тестовой архитектуры в слоистую стратегию, где каждый слой обнаруживает неисправности, которые могут пропустить другие.

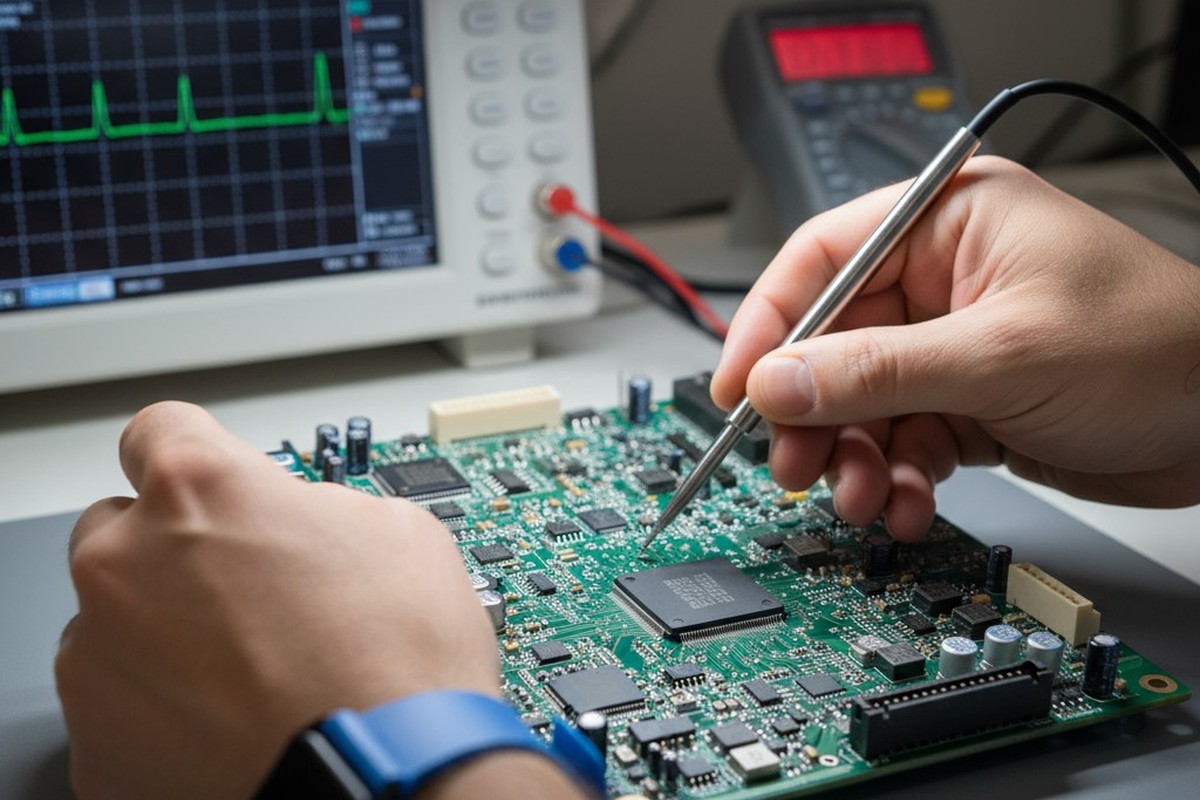

Процесс должен быть последовательным. Первый слой — границовое сканирование, которое быстро выполняется на всех совместимых устройствах для обнаружения межсоединительных неисправностей в цифровых частях платы. Платы, которые не проходят, отмечаются для немедленных доработок, что предотвращает катастрофические сбои при последующем включении питания. Второй слой — тестирование без векторов, которое проводится по всей плате для обнаружения отсутствующих или неправильных пассивных компонентов, грубых коротких замыканий и ошибок полярности. Оно охватывает компоненты и сети, невидимые для цепи сканирования.

Третий и последний слой — это сфокусированный функциональный тест. После фильтрации структурных неисправностей плата включается для проверки ее ключевых функций в условиях, приближенных к реальным. Область тестирования адаптируется к назначению платы — например, для проверки точности АЦП на плате сбора данных или регулировки нагрузки на блок питания. Эта последовательность обеспечивает раннее обнаружение катастрофических неисправностей и без разрушения, минимизируя время отладки более сложных функциональных отказов.

Для плат со сложной гибридной архитектурой — например, плотное цифровое ядро, окруженное аналоговой обработкой сигналов — может подойти гибридная стратегия. Можно разработать частичную фиксацию ICT, предназначенную только для критической аналоговой части, оставляя цифровую — для границового сканирования. Экономические преимущества частичной фиксации более благоприятны, снижая стоимость и сроки, при этом обеспечивая необходимое покрытие всей разработки.