La pression pour détecter les défauts de fabrication avant l’expédition des cartes est non négociable. Un seul défaut échappé dans un système critique peut coûter exponentiellement plus que le test qui l’aurait détecté. Cette réalité pousse de nombreuses équipes d’ingénierie vers les tests en circuit (ICT) comme norme, une méthode longtemps considérée comme la référence en matière de couverture. L’ICT complète offre un accès approfondi à presque chaque nœud d’une carte, promettant des taux de détection de défauts proches du maximum théorique. Pour la production à volume élevé, l’investissement a du sens ; les coûts fixes liés à la conception des fixeurs et à l’équipement de test sont amortis sur des milliers d’unités, réduisant la charge par unité à des niveaux négligeables.

Mais l’économie change lorsque les volumes de production diminuent. Pour des séries inférieures à quelques centaines d’unités, les forces mêmes de l’ICT deviennent des inconvénients. La conception sur mesure du fixateur nécessaire pour chaque design de carte implique un coût fixe d’ingénierie élevé, qui ne s’adapte pas. Les délais s’allongent pendant la conception, la fabrication et le débogage des fixateurs. Les itérations de conception, courantes lors de l’introduction de nouveaux produits, invalidant totalement les fixateurs, forçant à recommencer le cycle. Chez Bester PCBA, nous avons suivi cette logique dans des centaines de projets. Pour des séries inférieures à 200 ou 300 unités, le coût complet de l’ICT ne justifie pas son prix.

L’alternative n’est pas d’abandonner les tests rigoureux, mais de remplacer le modèle basé sur le fixateur par une stratégie plus légère et plus rapide, reposant sur la balayage par limite, les tests sans vecteur, et les tests fonctionnels ciblés. Cette combinaison offre une couverture de défaut comparable, élimine le goulot d’étranglement du fixateur, et permet un cycle de débogage plus rapide lorsque des défauts sont détectés. Ce changement n’est pas idéologique ; c’est une réponse pratique à la friction mathématique et mécanique que l’ICT impose aux productions à faible volume et agiles.

L’hypothèse ICT et ses limites

Le test en circuit est devenu la norme industrielle à une époque de conceptions à volume élevé et stables. Le modèle était simple : investir massivement à l’avance dans un fixateur personnalisé et un testeur sophistiqué, puis exploiter cet investissement sur des dizaines de milliers d’unités identiques. Avec des temps de test par unité mesurés en secondes, le coût marginal par carte était effectivement nul après l’absorption des coûts fixes. Pour un fabricant d’électronique grand public produisant 50 000 unités du même SKU, le calcul était imparable.

Ce modèle de production s’est fracturé. La fabrication électronique moderne sert de plus en plus des marchés à forte diversité et faible volume. Les cycles de vie des produits sont plus courts, les itérations de conception plus fréquentes, et la personnalisation un avantage compétitif. Une entreprise peut produire 150 unités d’une variante, faire évoluer la conception, puis produire 200 de la suivante. L’hypothèse qu’un seul fixateur testera des milliers de cartes identiques n’est plus valable. Les coûts fixes, insignifiants en haute volume, deviennent punissants lorsqu’ils sont répartis sur quelques centaines d’unités.

Le modèle échoue lorsque le coût total de l’infrastructure ICT dépasse le coût ajusté au risque des stratégies alternatives. Ce seuil n’est pas arbitraire. Il dépend du coût du fixateur, du temps d’ingénierie, du délai de fabrication, et de la couverture pouvant être atteinte par des méthodes sans fixateurs. Pour la plupart des designs de cartes, ce seuil se situe entre 200 et 300 unités.

Le piège du coût fixe des tests en circuit

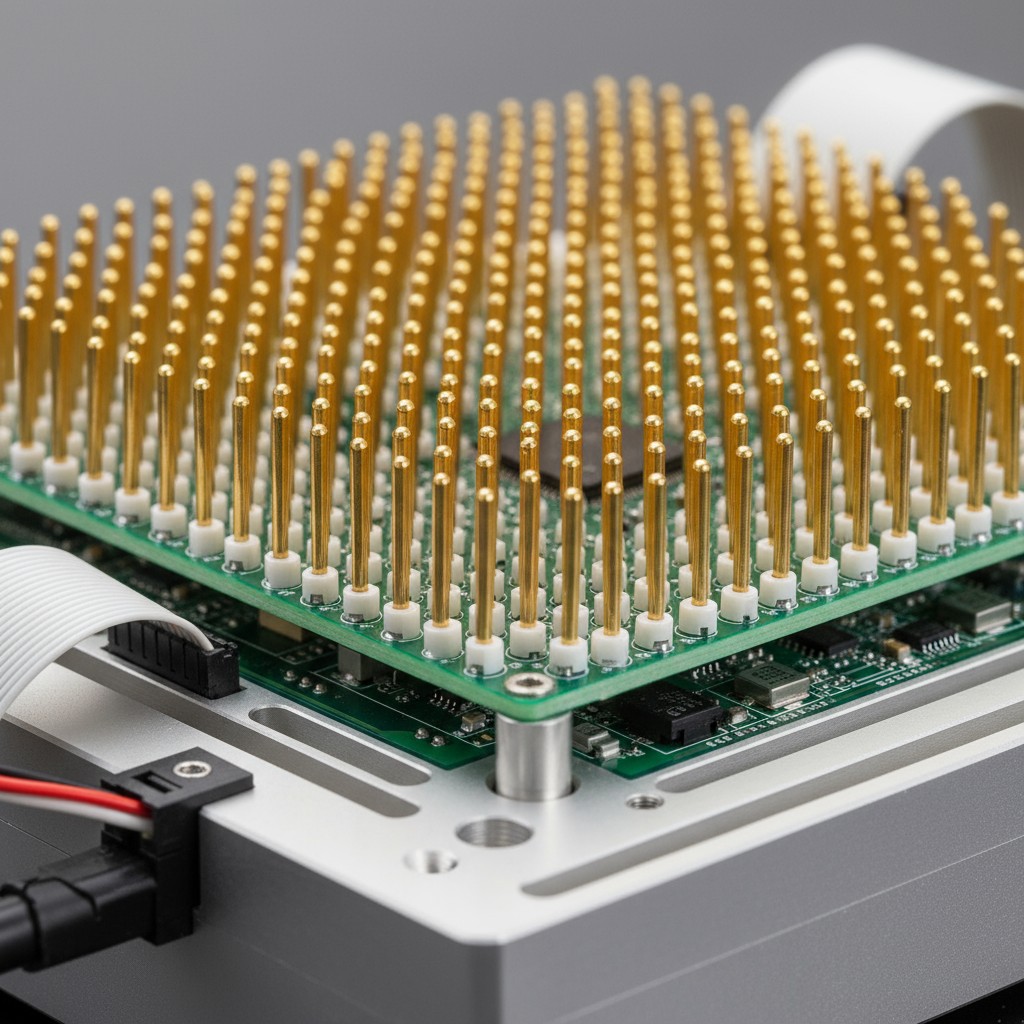

Bien que le fixateur soit le coût le plus visible de l’ICT, la charge économique réelle est bien plus large. Un fixateur ICT personnalisé n’est pas un achat standard ; c’est un artefact conçu sur mesure, spécifiquement pour le layout de la carte. Le processus de conception nécessite de traduire la netlist et le placement des composants en une structure mécanique équipée de contacts à ressort, alignés avec précision sur chaque point de test. Le fixateur doit tenir compte des tolérances des composants, du délaminage de la carte, et de l’usure des probes. Il doit ensuite être validé et débogué — un processus qui révèle souvent des problèmes imprévus avec l’accès aux probes ou l’intégrité du signal.

Coûts d’ingénierie des fixateurs et délais

Le coût d'ingénierie pour une fixation modérément complexe se situe généralement entre $8 000 et $15 000. Les plaques à haute densité avec des composants à finition fine ou un accès limité aux points de test peuvent faire grimper ce chiffre à $25 000 ou plus. Il s'agit purement du coût de l'interface mécanique et électrique personnalisée nécessaire pour connecter la carte à l'équipement ICT, séparé de la dépense en capital du testeur lui-même.

Le délai d'exécution est tout aussi important. Dès que la conception d'une carte est finalisée, la conception et la fabrication du fixture prennent généralement entre deux et quatre semaines, s'étendant jusqu'à six pour les conceptions complexes. Pendant cette période, la production est suspendue. Les cartes peuvent être assemblées, mais elles ne peuvent pas être testées. Elles restent en inventaire, en attente. Si la conception change pendant cette période — ce qui est courant lors de l'introduction de nouveaux produits — le fixture doit être modifié ou jeté. Le compteur se remet à zéro.

La formule du point mort pour les productions à faible volume

Le piège économique devient évident lorsque le coût du fixture est divisé par le nombre d'unités. Un fixture à $12 000 pour une production de 100 unités ajoute une charge de $120 à chaque carte. Pour une carte avec un devis de $500 en matériaux, cela représente 24 % de surcoût pour le test. Même si le processus ICT est rapide, l'efficacité économique est faible. Le même fixture amorti sur 500 unités réduit le coût par unité à $24, une surcharge beaucoup plus acceptable de cinq pour cent. La différence est purement une question de volume.

Le point de rentabilité est l'endroit où le coût total de l'ICT — comprenant l'ingénierie, la configuration et le coût d'opportunité du délai d'exécution — égalise le coût d'une alternative sans fixture. Pour une stratégie combinant la détection par détection de limite, les tests sans vecteurs, et un test fonctionnel léger, le coût de l'infrastructure est considérablement inférieur. La détection par détection de limite ne nécessite pas de fixture, et les tests sans vecteurs utilisent des capteurs réutilisables qui fonctionnent sans contact mécanique. Tout fixture de test fonctionnel est généralement minimal et générique, et ne nécessite pas plusieurs semaines d'ingénierie spécifique à une carte.

Pour des volumes de production inférieurs à 200 unités, l'économie de l'ICT s'effondre. En dessous de 300 unités, le cas est marginal, dépendant de la complexité de la carte. Ce n'est qu'au-dessus de 300 unités pour des conceptions stables et non itératives que l'ICT commence à redevenir économiquement viable.

Ce qu'est réellement le Boundary Scan et le Test sans vecteur

L'alternative aux tests basés sur des fixtures n'est pas un compromis en matière de rigueur, mais un passage à des méthodes qui exploitent l'infrastructure de conception existante et la mesure sans contact. Ces outils ont été développés pour répondre à la même tendance qui mine la ICT : augmentation de la densité des circuits et réduction de l'accès aux points de test physiques.

La détection par détection de limite, formalisée dans la norme IEEE 1149.1 (connue couramment sous le nom de JTAG), intègre la logique de test directement dans les circuits intégrés d'une carte. Les puces conformes incluent une chaîne de cellules à chaque pin d'entrée et de sortie. Lors d'un test, une interface à quatre fils transfère des motifs dans ces cellules, contrôlant les états logiques sur les réseaux de la carte. Les états résultants sont capturés et transférés pour analyse, permettant au testeur de contrôler et d'observer les signaux au niveau des pins sans contact physique. Cette méthode non invasive est très efficace pour détecter les courts-circuits, les ouvertures et les défauts de type stuck-at entre les dispositifs conformes.

Les tests sans vecteurs complètent cela en utilisant des mesures capacitatives et inductives pour détecter les défauts sur toute la carte. Un réseau de capteurs placé à proximité de la carte mesure la signature électromagnétique des composants et tracés assemblés. Les courts créent un couplage capacitif mesurable ; les ouvertures présentent des changements caractéristiques d'impédance. La méthode est rapide, sans contact, et peut déduire la présence de composants, leur polarité et leur valeur approximative, ce qui la rend efficace pour détecter les défauts grossiers de fabrication tels que composants manquants, diodes inversées, ou traces pontées.

Comparaison de la couverture : les chiffres derrière le compromis

L'objection principale à l'abandon de l'ICT est la couverture. Bien que l'ICT puisse, en principe, accéder à chaque nœud d'une carte avec suffisamment de points de test, l'affirmation selon laquelle les alternatives sont inférieures est incomplète. La véritable question est de savoir si elles atteignent une couverture suffisante pour attraper les défauts qui se produisent réellement, et si un test fonctionnel ciblé peut combler l'écart restant.

Ce que couvre Boundary Scan

La couverture du scan de frontière dépend du nombre de composants sur la carte qui sont conformes à la norme JTAG. Pour les cartes dominées par la logique numérique — microprocesseurs, FPGAs, mémoire — la couverture est étendue. La chaîne de scan peut tester l'interconnexion entre ces dispositifs avec des taux de détection de défauts dépassant 95 pour cent pour les courts-circuits, les ouvertures et les défauts

Ce que l'analyse sans vecteur apporte

Les tests sans vecteur comblent les lacunes laissées par la détection par scan de bord, en particulier pour les composants passifs et les défauts majeurs d'assemblage. Les mesures capacitives peuvent détecter les résistances manquantes, les valeurs de condensateurs incorrectes et les diodes inversées. Moins précises que les mesures directes de l’ICT, elles constituent néanmoins un filtre efficace pour les erreurs les plus courantes : composant erroné, composant manquant ou mauvais alignement. Cela ajoute de 10 à 20 pour cent à la couverture totale des défauts, offrant une couche de vérification sans contact pour les pièces que le scan de bord ne peut pas voir.

L'écart restant et comment le test fonctionnel léger le comble

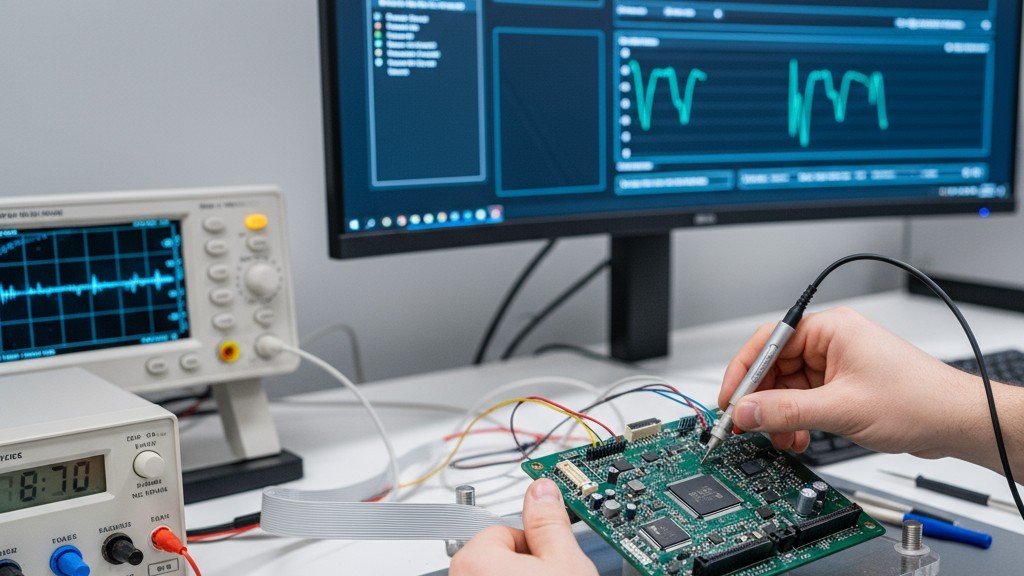

La combinaison de la détection par détection de limite et des tests sans vecteurs laisse encore un écart dans la validation fonctionnelle et la performance analogique. Un composant peut être présent et connecté correctement mais ne pas fonctionner conformément aux spécifications. Une alimentation pourrait fournir une tension mais avec un bruit excessif. C'est là qu'un test fonctionnel léger (FCT) joue son rôle. Contrairement à une configuration ICT complète, un FCT léger valide que la carte remplit sa fonction prévue dans des conditions réalistes. Il applique la puissance, stimule les entrées, et mesure les sorties. Pour un contrôleur de moteur, il pourrait vérifier la génération de signal PWM ; pour une carte de communication, il pourrait vérifier la transmission de données sans erreur. Le test fonctionnel complète les tests structurels, en détectant les défauts que les autres méthodes ne peuvent pas voir.

Combinés, ces trois méthodes atteignent généralement une couverture de défaillance de 85 à 95 %. Ce n’est pas 100 %, mais ce n’est pas non plus le cas en pratique pour l'ICT. En raison des limitations des points de test et de l'usure des sondes, la couverture réelle de l'ICT est souvent inférieure à son maximum théorique. La différence de couverture est bien plus faible que la pénalité de coût et de délai.

L’avantage de la boucle de débogage

La couverture de test n'est que la moitié de l'équation de la valeur ; l'autre moitié est la rapidité et la précision de l'isolation des défauts. Un test qui détecte un défaut mais fournit un diagnostic vague augmente le temps et le coût nécessaires pour en trouver la cause racine.

Alors que l'ICT est efficace pour signaler les défauts, ses diagnostics peuvent être frustrantement vagues. Un testeur peut indiquer que le nœud 47 est en court-circuit à la masse, mais il n'explique pas pourquoi ou où. Le technicien doit suivre le schéma, localiser le réseau, et inspecter visuellement la zone — un processus qui peut durer des heures sur une carte dense à plusieurs couches.

Les diagnostics par balayage de limite sont fondamentalement différents. Parce que la chaîne de balayage est intégrée dans les composants, le test identifie les défauts à des broches et des appareils spécifiques. Un court-circuit entre deux nets est identifié par les broches exactes de l’appareil impliquées, limitant la recherche à quelques millimètres carrés. Les ouvertures sont détectées entre des paires spécifiques de conducteurs et de récepteurs. La sortie du diagnostic n’est pas un code de défaut. C’est une carte. Cette précision signifie qu’un défaut qui prend une heure à déboguer avec des données ICT peut souvent être résolu en 10 à 20 minutes avec le balayage de limite. Pour une production de 100 unités avec un taux de défaut typique, le temps de débogage cumulé économisé peut dépasser 10 heures.

Délai de livraison et flexibilité : la valeur cachée

L’argument économique contre l’ICT pour de faibles volumes est convaincant, mais la pénalité de délai de production l’est tout autant. Le processus d’ingénierie de la fixation de deux à quatre semaines impose un délai obligatoire entre la gelée du design et la préparation du test. Pour l’introduction de nouveaux produits, où le délai de mise sur le marché est critique, ce délai est souvent inacceptable.

Le balayage de limite et le test sans vecteur éliminent cette attente. La configuration du test peut être effectuée en heures ou en jours, et non en semaines, permettant aux cartes de passer de l’assemblage au test puis à l’expédition en flux continu. Cette flexibilité est cruciale lorsque les conceptions évoluent. Une première série de prototypes peut révéler des problèmes nécessitant des changements de conception des circuits. Avec l’ICT, chaque révision exige une nouvelle fixation ou une fixation retravaillée, entraînant à nouveau le coût et le délai de production. Les schémas de test de balayage de limite, générés à partir de la netlist, se mettent à jour automatiquement avec la conception. Cela crée une stratégie de test qui soutient le développement itératif plutôt que de le pénaliser.

Quand choisir encore l'ICT

Mais le cas contre l’ICT à faible volume n’est pas absolu. Certaines conceptions et contextes de production justifient encore l’investissement.

Les cartes avec des sections analogiques ou RF à haute densité sont de mauvais candidates pour une stratégie purement sans fixation. Les composants analogiques manquent de logique de balayage de limite, et des caractéristiques de performance critiques comme le gain ou le bruit de phase ne peuvent pas être vérifiées structurellement. Si la circuiterie analogique ou RF représente plus de 40 pour cent de la fonctionnalité de la carte, le cas pour l’ICT devient considérablement plus solide.

Les industries soumises à des réglementations telles que médical, aérospatial et automobile opèrent souvent selon des règles qui imposent une couverture ou des méthodes de test spécifiques. Si une norme de référence exige un test en circuit ou un accès équivalent au niveau des nœuds, les stratégies alternatives peuvent ne pas suffire. Ici, le coût de l’ICT est un coût non négociable pour l’entrée sur le marché.

Enfin, une voie claire et engagée vers une production à volume élevé modifie les calculs. Si une première série de 150 unités doit atteindre 1 000 unités en six mois, le coût de la fixation est amorti sur le volume total prévu. Cela nécessite une grande confiance dans la prévision et une conception stable, mais cela peut rendre l’investissement initial rentable.

Construire la stratégie de test alternative

Remplacer l’ICT n’est pas une simple substitution ; c’est une reconfiguration de l’architecture de test en une stratégie stratifiée, où chaque couche détecte les défauts que les autres pourraient manquer.

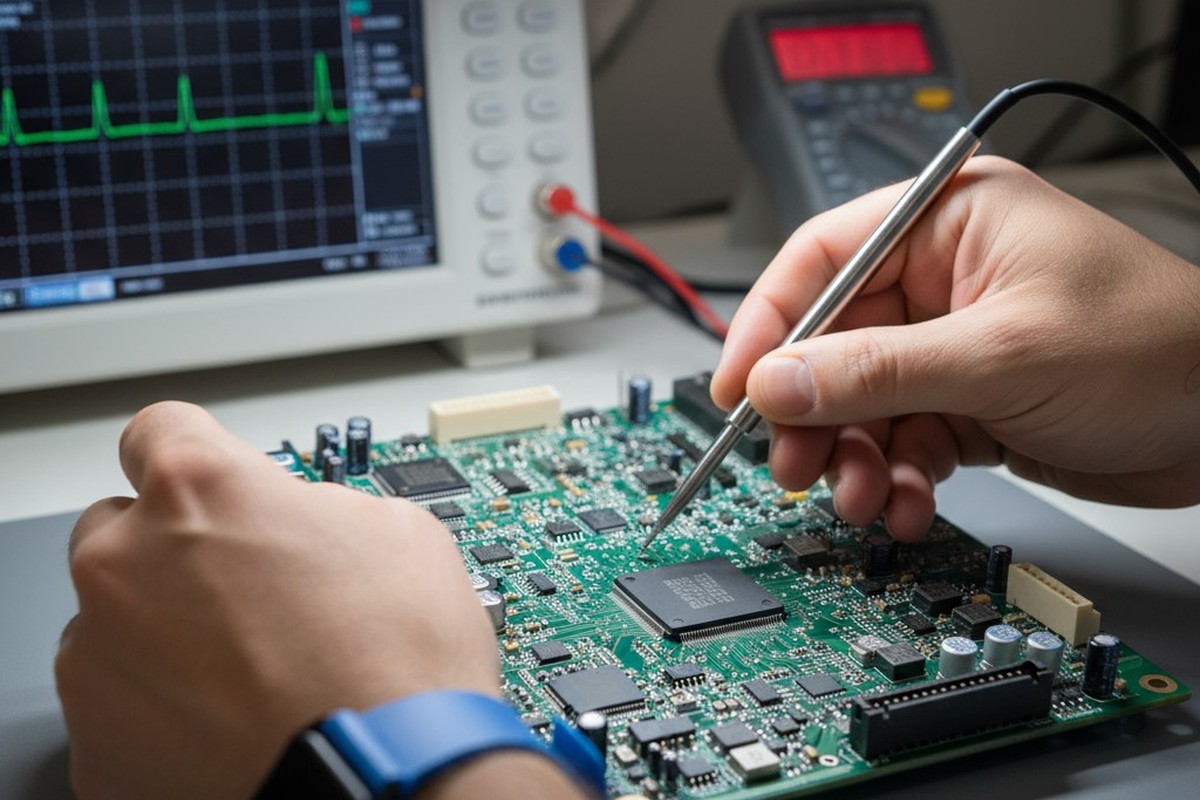

Le processus doit être séquentiel. La première couche est le balayage de limite, qui s’exécute rapidement sur tous les dispositifs conformes pour détecter les défauts d’interconnexion sur les parties numériques de la carte. Les cartes qui échouent sont signalées pour une reprise immédiate, évitant ainsi des échecs catastrophiques lors de l’application ultérieure de l’alimentation. La seconde couche est le test sans vecteur, qui fonctionne sur toute la carte pour détecter les composants passifs manquants ou incorrects, les courts-circuits importants et les erreurs de polarité. Elle couvre les composants et nets invisibles pour la chaîne de balayage.

La troisième et dernière couche est un test fonctionnel ciblé. Avec les défauts structurels déjà filtrés, la carte est alimentée pour valider ses fonctions critiques dans des conditions opérationnelles réalistes. La portée est adaptée à l’objectif de la carte — vérification de la précision de l’ADC sur une carte d’acquisition de données ou régulation de charge sur une alimentation. Cette séquence garantit que les défauts catastrophiques sont détectés tôt et de manière non destructive, minimisant le temps de débogage sur les défaillances fonctionnelles plus complexes.

Pour les cartes avec une complexité hybride — par exemple un noyau numérique dense entouré d’un conditionnement de signal analogique — une stratégie hybride peut être la meilleure. Une fixation ICT partielle peut être conçue pour sonder uniquement la section analogique critique, laissant la partie numérique au balayage de limite. L’économie d’une fixation partielle est plus favorable, réduisant le coût et le délai tout en fournissant la couverture nécessaire pour l’ensemble du design.