एक मृत प्रोटोटाइप की चुप्पी भारी होती है। यह सिर्फ फैन की आवाज या डिबग इंटरफ़ेस पर डार्क LED का अभाव नहीं है। यह तुरंत ही, लागत का नीचे गिरना का हिसाब है। जब एक प्रोटोटाइप बोर्ड प्रारंभ में सफल नहीं होता—शायद BGA सही तरह से असेंबली के दौरान बैठ नहीं पाया, या कोई डिज़ाइन दोष स्वैप की मांग करता है—तो तुरंत ध्यान बड़े, काले वर्ग पर केंद्रित हो जाता है, जो PCB के केंद्र में होता है।

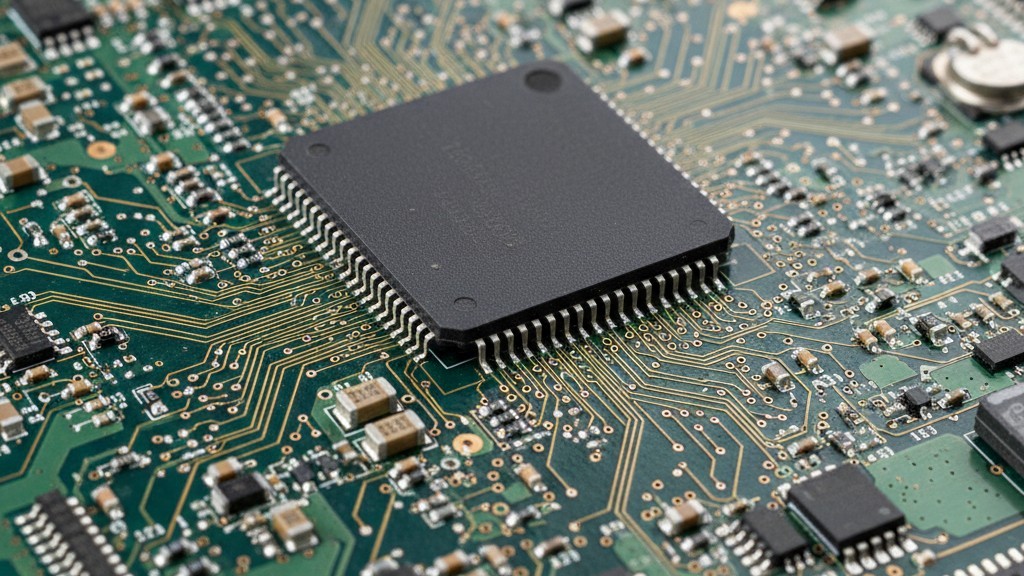

उच्च-विश्वसनीयता क्षेत्रों में, उस वर्ग में अक्सर हाई-एंड FPGA होता है, जैसे Xilinx Kintex UltraScale या Intel Stratix 10। ये वस्तुएं कमोडिटी घटक नहीं हैं; ये आस्तियां हैं। आपूर्ति श्रृंखला के संकट के समय में, उस एक मिट्टी को बदलने में 52 सप्ताह का लीड टाइम या एक ब्रोकर बाजार मार्कअप हो सकता है जो परियोजना के बजट को तोड़ देता है। अपने आप में, एक 12-लेयर स्टैक-अप जिसमें ब्लाइंड और बरीड वायस होते हैं, उत्पादन और असेंबली लागत में $5,000 का प्रतिनिधित्व कर सकता है। पुनर्निर्माण मानक मरम्मत नहीं है। यह एक बचाव संचालन है जिसमें संपूर्ण विकास समय रद्द हो सकता है।

भौतिकी कोई मोलभाव नहीं करता

एक खतरनाक भ्रांति बनी रहती है कि Ball Grid Array (BGA) हटाने का काम बस गरमी लगाना है जब तक सोल्ड पिघल न जाए। यह रवैया प्रोटोटाइप को नष्ट कर देता है। हाथ में गर्मी बंदूकें, जबकि ट्यूबिंग सिकुड़ने के लिए शानदार हैं, हाई-डेंसिटी इंटरकनेक्ट्स के लिए विनाश के उपकरण हैं।

भौतिकी तापीय मात्रा और तापीय विस्तार सहगुणाक CTE पर निर्भर करती है। एक आधुनिक FPGA एक बोर्ड पर बैठता है जिसमें कॉपर ग्राउंड प्लेन के साथ विशेष रूप से डिज़ाइन किया गया है जो गर्मी को फैलाने के लिए है। यदि आप शीर्ष भाग को गरम हवा से उड़ा देते हैं बिना नीचे गर्म किए, तो आप एक लंबवत थर्मल ग्रेडिएंट बनाते हैं। ऊपर का भाग फैलता है जबकि नीचे ठंडा और कठोर रहता है। परिणाम विकृति है। जैसे-जैसे बोर्ड मुड़ा, यह सोल्डर जॉइंट्स के खिलाफ खींचता है। यदि ताप स्रोत अनियंत्रित है, तो आप “पैड क्रैटरिंग” का जोखिम उठाते हैं—अर्थात्, फाइबरग्लास लैमिनेट से कॉपर पैड्स को फाड़ देना। एक बार यदि आंतरिक ट्रेस से पैड फट जाता है, तो बोर्ड बेकार हो जाता है। कोई जंपर वायर भारी गति वाली डिफेरेंशियल जोड़ी, 10 Gbps पर, को भरोसेमंद रूप से ठीक नहीं कर सकता।

इसी कारण इंजीनियरों को एक “स्थानीय उत्पादन” दृष्टिकोण अपनाना चाहिए। लक्ष्य है मूल रिफ्लो प्रोफ़ाइल की नकल करना—विशेष तापमान वक्र जो बोर्ड ने विनिर्माण ओवन में देखा—पूरा असेंबली को एक सोख तापमान (आम तौर पर लगभग 150°C से 170°C) पर लाना ताकि फ्लक्स सक्रिय हो सके और PCB के तापमान को समान कर सके। तभी चाहिए कि आप प्रॉपर्टी का स्थानीयकृत ऊर्जा उस हिस्से पर लगाएं ताकि उसे 217°C के लिक्विडस पॉइंट से ऊपर ले जाया जा सके। भौतिकी डेडलाइन की अनदेखी करती है; यदि तापीय रैंप बहुत तेज़ है, तो अंदर फंसे नमी भाप में फैल जाती है, जिससे पैकेज डेलामिनेट हो सकता है या “पॉपकॉर्न” बन सकता है। फटा हुआ चिप एक मृत चिप है।

प्रक्रिया: नियंत्रित हस्तक्षेप

एक $2,000 घटक की सुरक्षा कठोरता की मांग करती है। प्रक्रिया शुरू होती है कुछ दिन पहले ही, नमी प्रबंधन के साथ पुनर्निर्माण। जब तक बोर्ड को शुष्क बॉक्स में न रखा गया हो जिसमें नमी संकेतक सुरक्षित स्तर पढ़ रहे हों, उसे बेक करना चाहिए। मानक IPC-1601 प्रोटोकॉल बोर्ड और घटक से नमी को निकालने के लिए बेकिंग की सलाह देते हैं ताकि उस भाप-दबाव डेलामिनेशन से बचा जा सके। इस कदम को छोड़ना अक्सर कई हफ्तों बाद दिखाई देने वाली अदृश्य असफलताओं का सबसे सामान्य कारण है।

एक बार जब बोर्ड सूख जाता है, तो यह एक समर्पित पुनर्निर्माण प्रणाली में स्थानांतरित हो जाता है—आम तौर पर एक मशीन जिसमें स्प्लिट-विज़न ऑप्टिक्स, बॉटम-साइड इंफ्रारेड प्रीहीटर, और एक कंप्यूटर-नियंत्रित टॉप कंवेंक्शन नोजल होता है। यह प्रक्रिया स्वचालन द्वारा संचालित होती है, न कि मैनुअल अनुभव द्वारा। एक थर्मोकूपल अक्सर एक बलिदानी बोर्ड से जुड़ा होता है ताकि तापमान प्रोफ़ाइल को बिल्कुल माप सके। हमें यह जानना जरूरी है कि जब मशीन 230°C कहती है, तो उस 35x35mm ग्रिड के केंद्र के नीचे सोल्डर बॉल्स वास्तव में रिफ्लो तक पहुंच रहे हैं, न कि पास के हीट सिंक के कारण ठंडे बैठने के कारण।

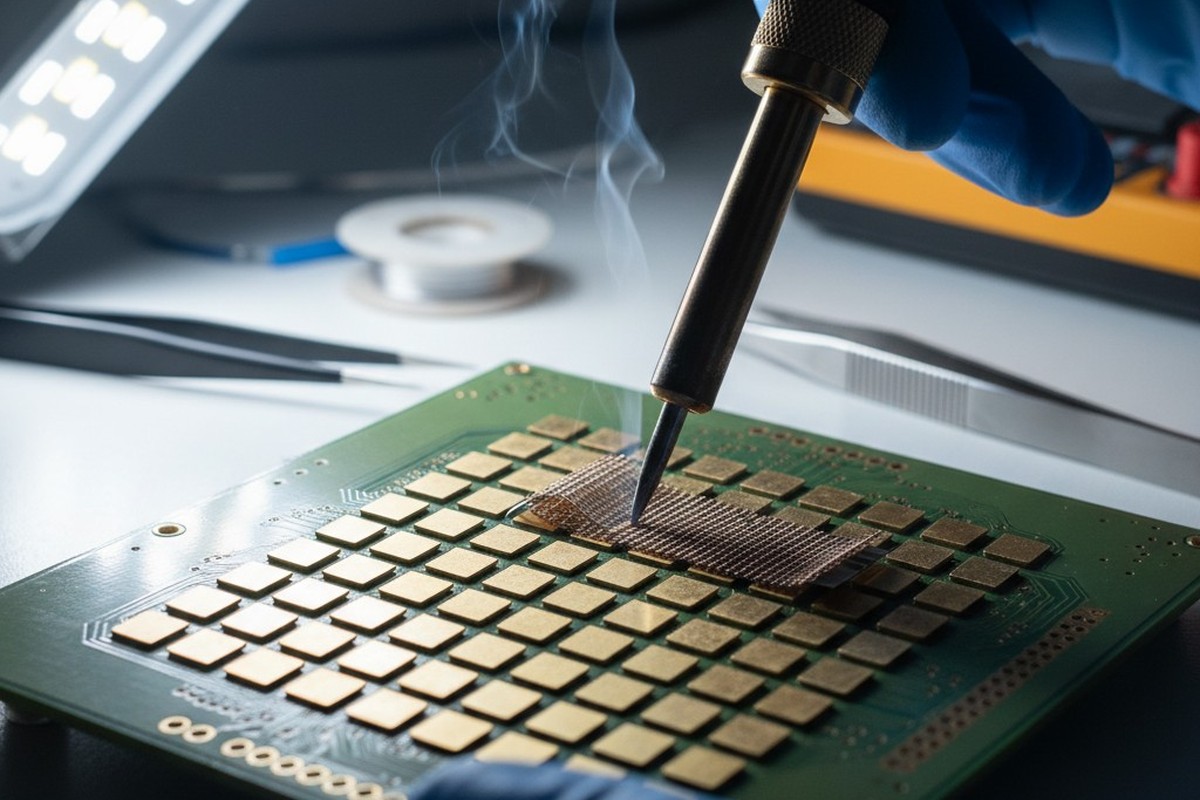

अपनी खुद की हटाई हुई प्रक्रिया यदि प्रोफ़ाइल सही हो तो कम उत्साहजनक होती है। वैक्यूम नोजल नीचे उतरता है, सोल्डर तरल हो जाता है, और घटक शून्य बल के साथ खड़ा हो जाता है। उसके बाद चिंता का स्तर तुरंत बढ़ जाता है: साइट ड्रेसिंग। इसमें पुराने सोल्डर को हाथ से PCB पैड से निकालना शामिल है, सोल्डरिंग आयरन और विकिंग ब्रैड का उपयोग कर। यहाँ तकनीशियन के हाथ सबसे महत्वपूर्ण होते हैं। आयरन को पैड्स के ऊपर “फ़्लोट” करना चाहिए; किसी भी नीचे की ओर दबाव से पैड उठ सकता है, जो सामान्यतः बोर्ड के लिए घातक होता है। यदि lifted पैड के लिए epoxy मरम्मत विधियाँ मौजूद हैं, तो मरम्मत द्वारा उत्पन्न प्रतिबाधा (इंपीडेंस) असामान्य रूप से उच्च-आवृत्ति FPGA लाइनों के लिए अस्वीकार्य हो सकती है। पैड्स को pristine, सामान और कॉपर-ब्राइट होना चाहिए ताकि नया या पुनःबैलेज्ड चिप रखा जा सके।

रीबैलिंग समीकरण

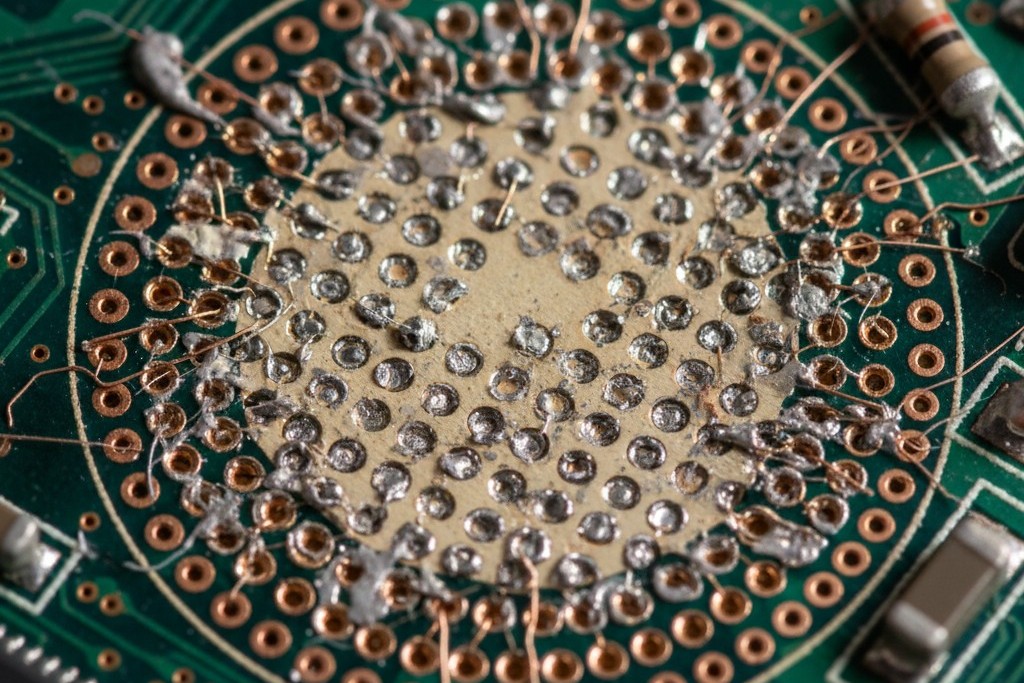

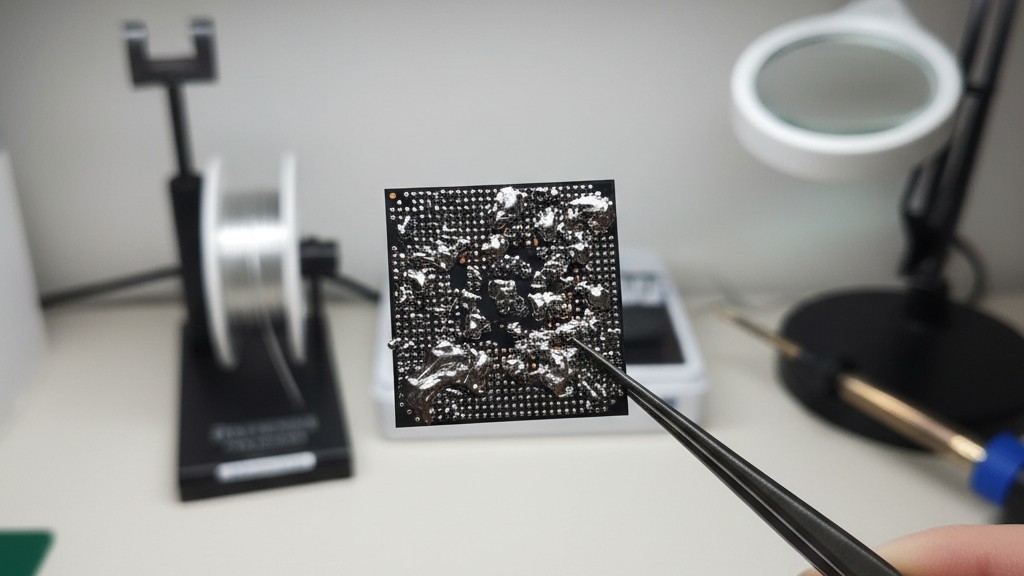

कभी-कभी लक्ष्य नया चिप नहीं होता, बल्कि कहीं और उपयोग के लिए एक मृत बोर्ड से पुरानी चिप को बचाना या कनेक्शन विफलता वाली चिप को फिर से बैठाना होता है। यह पुनः बॉलिंग का उप-शास्त्र पेश करता है। एक हटा दी गई BGA के नीचे गंदगी और अनियमित सोल्डर के ढेर बचे होते हैं। इन्हें साफ़ करना चाहिए और नई सोल्डर स्फेरें जोड़नी चाहिए।

यह एक शुद्ध ROI गणना है। एक $5 वस्तु माइक्रोकंट्रोलर की पुनः बॉलिंग वित्तीय रूप से बकवास है; श्रम घंटे घटक लागत से अधिक हैं। लेकिन एक Virtex UltraScale+ जिसकी कीमत $15,000 है, के लिए पुनः बॉलिंग अनिवार्य है। प्रक्रिया में चिप के फुटप्रिंट से मेल खाने वाले विशिष्ट स्टैंसिल, एक टक्कायुक्त फ्लक्स, और हजारों पहले से निर्मित सोल्डर स्फेरें (अक्सर 0.4mm या 0.5mm व्यास में) को मैन्युअली डालना और संरेखित करना शामिल है।

असम्भावना से इनकार नहीं किया जा सकता। हर बार जब सिलिकॉन डाइ को रिफ्लो साइकल से गुजरना पड़ता है—240°C तक गर्म करना और ठंडा करना—थेर्मल तनाव इकट्ठा होता है। सिलिकॉन डाइ, पैकेज सब्सट्रेट, और PCB के बीच थर्मल विस्तार का मेल न होना बल दिखाता है। जबकि एक चिप सामान्यतः दो या तीन रिफ्लो साइकल का सामना कर सकती है (प्रारंभिक असेंबली, हटाना, पुनः बॉलिंग, प्लेसमेंट), परिणाम की गारंटी कभी नहीं है। हम सही प्रोफ़ाइलिंग से जोखिम कम कर सकते हैं, लेकिन हम सामग्री की थकान सीमा नहीं बदल सकते।

पुनः कार्य करने का निर्णय आमतौर पर “बदलें बनाम पुनः प्राप्त करें” अनुपात पर निर्भर करता है। यदि सिलिकॉन की स्थानांतरणीयता नहीं है या यदि बोर्ड कई सप्ताह की अनूठी विनिर्माण समय का प्रतिनिधित्व करता है, तो एक उचित थर्मल प्रोफ़ाइल में निवेश और कुशल ऑपरेटर का समय शुरू करने की तुलना में बहुत कम है। उपकरण—प्री-हीटर्स, विज़न सिस्टम, नाइट्रोजन-इनर्टेड रिफ्लो हेड—इस तरह से डिज़ाइन किए गए हैं कि वे एक तबाही को मानक अभियांत्रिकीनि विलंब में बदल दें।