Ketika file desain masuk ke antrean rekayasa, kita tidak memeriksa routing atau penempatan komponen terlebih dahulu. Kita melihat lapisan Mask Paste.

Kebanyakan perancang memperlakukan lapisan ini sebagai terjemahan langsung dari dudukan tembaga: jika ada dudukan di papan, harus ada aperture berukuran sama dalam cetakan. Logika 1:1 ini rapi, bersih, dan sempurna secara matematis dalam lingkungan CAD. Ini juga merupakan penyebab paling umum kerusakan rakitan pada papan teknologi campuran modern.

Masalahnya? File Gerber adalah peta dua dimensi, tetapi sambungan solder adalah volume tiga dimensi. Begitu kita beralih dari layar ke lantai pembuatan, kita berurusan dengan dinamika fluida, tegangan permukaan, dan keterbatasan fisik mendorong pasta logam melalui lembaran baja.

Jika kita buta-membuat potongan cetakan berdasarkan output default “100% coverage” dari perangkat lunak ECAD Anda, kita jamin gagal. Pada papan dengan konektor berat dan mikrochip dengan pitch halus, pendekatan seragam memastikan separuh papan memiliki pasta berlebihan sementara separuh lainnya kekurangan. Kami tidak memodifikasi data cetakan Anda agar menjadi sulit; kami melakukannya karena fisika memerlukannya.

Solder Adalah Masalah Volume

Lupakan “coverage.” Kita perlu berpikir dalam mil kubik.

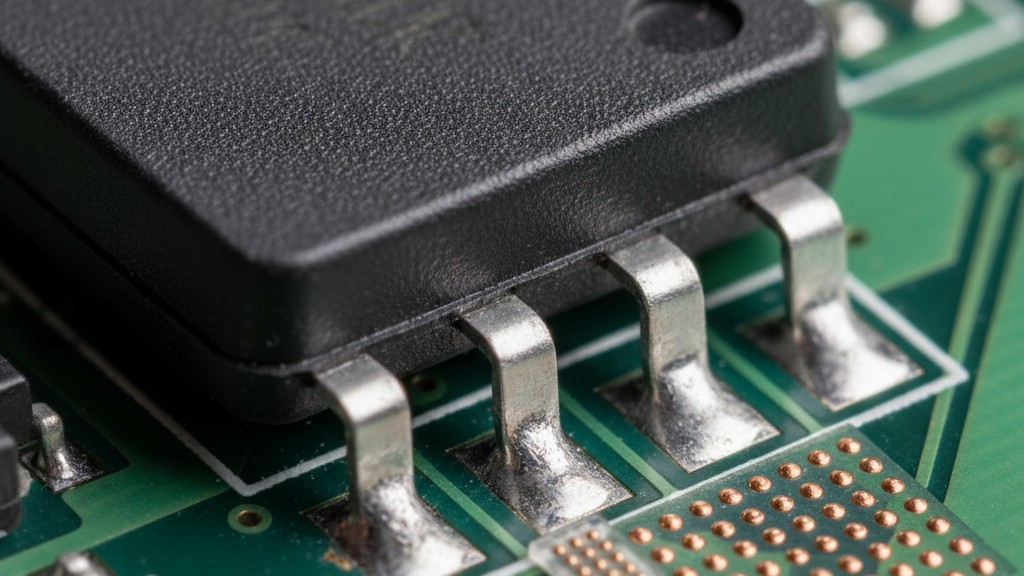

Integritas mekanik sebuah sambungan—terutama untuk komponen daya dan konektor—bergantung sepenuhnya pada volume fillet logam yang dihasilkan. Dudukan permukaan standar mungkin terlihat baik dengan deposit pasta setebal 5mil, tetapi header reflow lubang tembus atau konektor USB-C adalah makhluk yang berbeda.

Perancang sering panik ketika sebuah konektor terlepas saat pengujian prototipe, menganggap bagian itu sendiri cacat atau rumahnya terlalu lemah. Pada kenyataannya, masalahnya hampir selalu ketebalan cetakan. Konektor USB-C memiliki kaki struktural yang perlu dipasang dalam kedalaman tabung PCB. Jika kita menggunakan foil standar 4mil atau 5mil (umum untuk sebagian besar papan sinyal), kita hanya mengirim sebagian kecil dari solder yang dibutuhkan untuk mengisi tabung itu. Pasta dicetak di permukaan, meleleh, dan hilang ke dalam lubang, meninggalkan meniskus yang lemah dan kekurangan yang pecah saat pertama kali disisipkan.

Untuk memperbaikinya, kita harus menghitung volume total lubang dikurangi pin, menambahkan buffer 10% untuk pembakaran flux, dan melakukan rekayasa balik aperture cetakan untuk memberi pastanya tepat sebanyak itu. Seringkali, dudukan di papan tidak cukup besar untuk menahan pasta basah sebanyak itu. Ini memaksa kita melakukan overprint—secara sengaja mencetak pasta pada topeng solder agar menarik kembali ke dudukan selama reflow.

Lantai Rasio Area

Sementara bagian besar kekurangan, bagian kecil memiliki masalah sebaliknya: mereka menolak melepaskan. Di sinilah aturan “Area Ratio” menjadi batas keras dari keberhasilan produksi.

Percetakan stensil adalah perjuangan antara dua kekuatan: tegangan permukaan dari pasta yang menempel pada pad PCB, dan gesekan dari pasta yang menempel pada dinding bagian dalam aperture stensil. Agar pasta dapat dilepaskan dengan sukses, area pad harus jauh lebih besar daripada area dinding aperture.

Standar industri (IPC-7525) menetapkan zona bahaya dengan rasio 0,66. Jika rasio turun di bawah ini (misalnya, untuk BGA pitch 0,4mm atau kapasitor 01005), pasta menyumbat di dalam stensil daripada menempel pada papan. Anda akan mendapatkan satu cetak yang baik, mungkin dua, lalu aperture tersumbat. Mesin inspeksi optik otomatis (AOI) akan langsung menandai “solder tidak cukup”.

Kita bisa mencoba mengakali ini sedikit dengan pelapis nano yang membuat baja menjadi hidrofobik, secara efektif melumasi dinding aperture, tapi itu hanyalah perbaikan sementara. Pelapis tersebut aus setelah 10.000 siklus atau pembersihan under-wipe yang agresif. Satu-satunya solusi rekayasa permanen adalah mengubah geometri: kita bisa membuat aperture lebih besar (berisiko jembatan) atau membuat foil stensil lebih tipis untuk mengurangi luas permukaan dinding.

Konflik Bagian Besar / Bagian Kecil

Sekarang kita menghadapi konflik utama dalam perakitan elektronik modern: masalah “Part Besar / Part Kecil”. Anda mungkin memiliki regulator tegangan D2PAK berat yang membutuhkan banyak solder untuk dissipasi panas yang berada tepat di samping paket tingkat wafer dengan pitch 0,35mm yang membutuhkan olesan pasta mikroskopis untuk menghindari korsleting.

Jika kita menggunakan foil stensil “standar” 5mil—pilihan default untuk permintaan kutipan 90% yang kita lihat—kita akan merusak salah satu komponen ini. Foil 5mil menyediakan volume yang cukup untuk D2PAK, tetapi terlalu tebal untuk chip wafer kecil; Rasio Aspek akan salah, dan pasta tidak akan melepaskan. Jika kita beralih ke foil 3mil untuk mengakomodasi chip kecil, D2PAK akan kekurangan, menyebabkan void dan kegagalan termal.

Perancang sering bertanya, “Mengapa tidak cukup mengurangi ukuran aperture untuk bagian kecil?” Kita bisa, tetapi ingat Rasio Area: mengurangi area aperture sambil menjaga ketebalan foil hanya akan membuat rasio menjadi lebih buruk. Anda tidak dapat menyelesaikan masalah sumbu Z dengan penyesuaian sumbu X-Y.

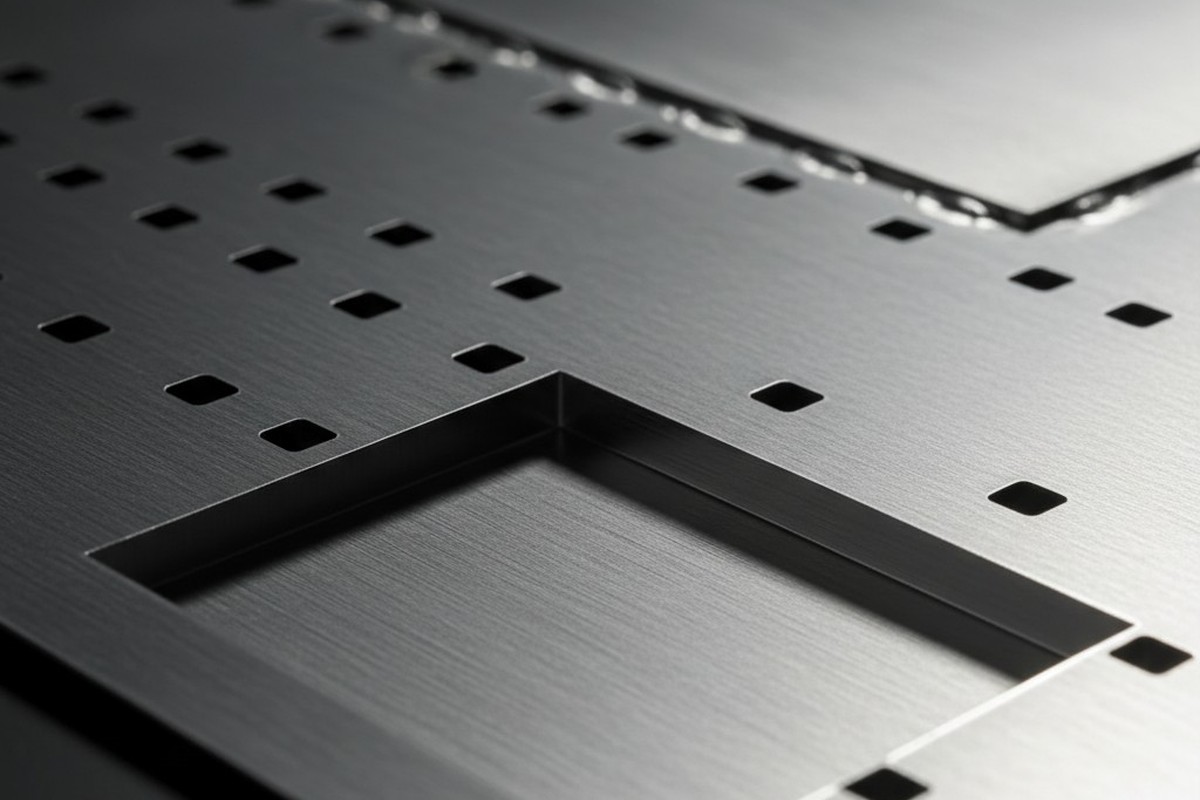

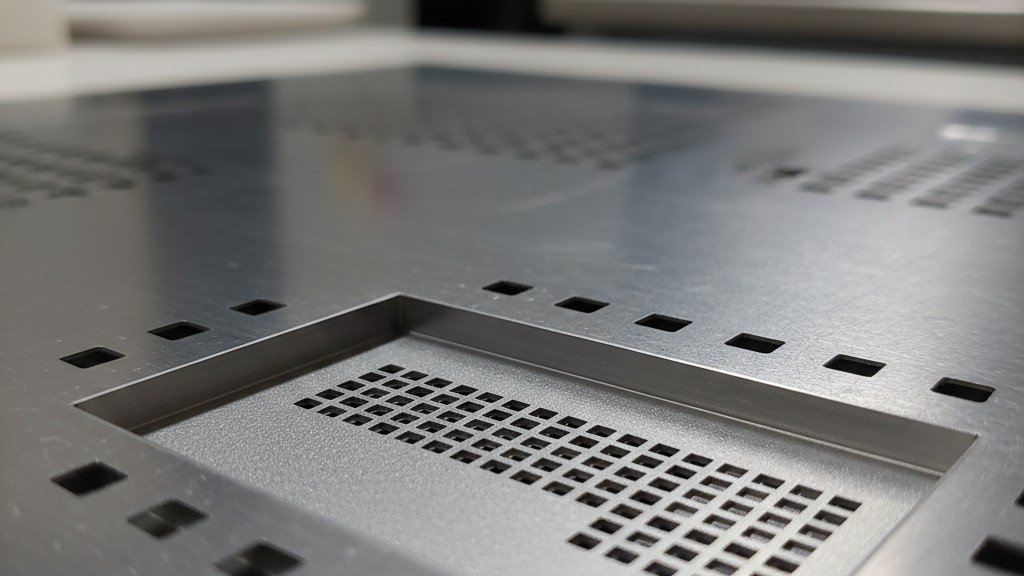

Topografi Teknik: Cetakan Langkah

Kita harus memperlakukan stensil lebih seperti peta topografi daripada lembar datar.

Kita menggunakan Step Stencils untuk menciptakan zona ketebalan terlokalisasi. Untuk D2PAK atau konektor USB tersebut, kita mungkin “meningkatkan” stensil, menyambungkan lembaran baja yang lebih tebal (misalnya, 6mil atau 8mil) ke area tertentu itu. Untuk BGA pitch kecil, kita mengukir kantung “turun langkah”, mengurangi ketebalan menjadi 3,5mil atau 3mil hanya untuk footprint komponen tersebut.

Ini bukan sihir; membutuhkan tata letak yang cermat. Bilah squeegee fleksibel, tetapi tidak cairan. Ia membutuhkan ruang transisi—biasanya 50 hingga 100 mil—untuk naik atau turun langkah tanpa melewatkan atau menyedot pasta dari lubang. Kita harus memetakan zona larangan ini dengan hati-hati, memastikan tidak ada komponen kritis yang duduk di lereng langkah. Jika dilakukan dengan benar, ini memungkinkan kita mencetak volume besar pasta untuk bagian daya dan deposit halus berdefinisi tinggi untuk mikro-komponen dalam satu kali proses. Ini mengubah papan yang “tidak dapat dibangun” menjadi yang berjalan dengan hasil 99%.

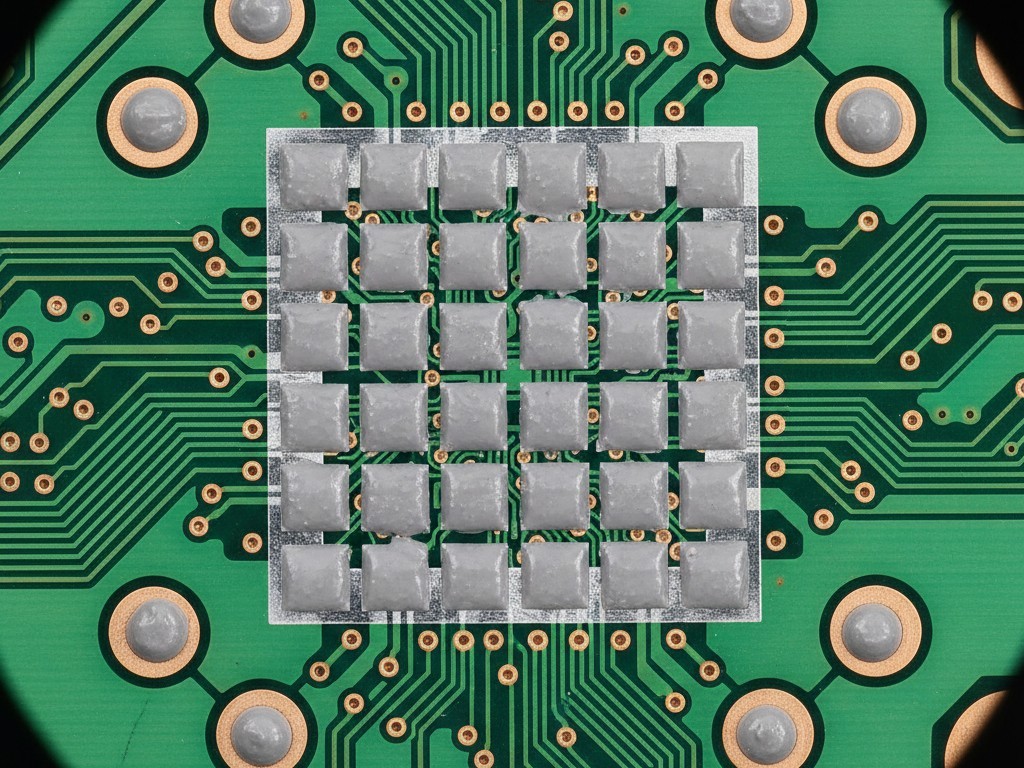

Kaca Jendela dan Outgassing

Modifikasi geometri tidak terbatas pada ketebalan. Kita juga harus melawan perilaku flux itu sendiri.

Di bawah pad termal besar, seperti pada QFN atau FET daya, perancang biasanya menggambar blok pasta maskara padat yang cocok dengan pad tembaga. Jika kita mencetak itu, kita menangkap kolam besar volatil (kendaraan flux) di bawah chip selama reflow. Saat flux mendidih, gas tidak punya tempat untuk keluar, menciptakan void besar—gelembung udara di dalam sambungan solder yang menghambat transfer panas.

Untuk mencegah ini, kita mengabaikan blok padat dalam Gerber dan menerapkan pengurangan “jendela kaca”. Kita membagi aperture persegi besar menjadi grid persegi kecil, dipisahkan oleh saluran baja 10-15 mil. Saluran ini bertindak sebagai jalan raya bagi flux yang menguap untuk keluar. Ini mungkin terdengar kontradiktif bagi insinyur tenaga yang menginginkan transfer termal maksimal, tetapi mencetak kurang tempel (sering coverage 60-70% alih-alih 100%) sebenarnya menghasilkan lebih kontak metal ke logam karena menghilangkan kekosongan.

Ekonomi Modifikasi

Sering ada penolakan terhadap biaya. Sebuah stensil potong laser standar mungkin menghabiskan biaya $150 sampai $200. Sebuah stensil langkah multi-level dengan pelapis nano mungkin mencapai $350 sampai $450. Tim pengadaan melihat item biaya itu dan bertanya apakah kita bisa hanya "membuatnya bekerja" dengan opsi standar.

Bandingkan itu dengan biaya alternatifnya.

Mengulang pekerjaan pada BGA 0,4mm yang terjepit tidak hanya sulit; sering kali mustahil tanpa merusak papan atau komponen tetangga. Mengganti konektor yang patah pada sebuah unit jadi biaya lima puluh kali lipat harga bagian mentahnya. Biaya NRE (Non-Recurring Engineering) dari sebuah stensil yang tepat adalah biaya sekali pakai. Biaya mengikis solder dari seribu papan karena kita mencoba melawan fisika adalah biaya berulang, menyakitkan, dan sepenuhnya dapat dicegah. Kita memodifikasi data karena biaya menjadi benar di percobaan pertama selalu lebih rendah daripada memperbaikinya kemudian.