Tekanan untuk menangkap kesalahan manufaktur sebelum papan dikirimkan adalah tidak dapat dinegosiasikan. Satu cacat yang lolos di sistem kritis bisa jauh lebih mahal daripada pengujian yang akan menangkapnya. Kenyataan ini mendorong banyak tim rekayasa menuju pengujian sirkuit (ICT) sebagai default, sebuah metode yang lama dianggap standar emas untuk cakupan. ICT penuh menawarkan akses komprehensif ke hampir setiap node di papan, menjanjikan tingkat deteksi kesalahan yang mendekati maksimum teoretis. Untuk produksi volume tinggi, investasi ini masuk akal; biaya tetap dari rekayasa fixture dan peralatan pengujian diamortisasi di ribuan unit, mengurangi beban per-unit menjadi tingkat yang dapat diabaikan.

Namun ekonomi berbalik saat volume produksi menurun. Untuk produksi di bawah beberapa ratus unit, kekuatan ICT justru menjadi kelemahan. Fixture khusus yang diperlukan untuk setiap desain papan membawa biaya rekayasa tetap yang curam dan tidak dapat diskalakan. Waktu tunggu memanjang saat fixture dirancang, dibuat, dan diperbaiki. Iterasi desain, yang umum dalam pengenalan produk baru, sepenuhnya membatalkan fixture, memaksa siklus dimulai ulang. Di PCBA Bester, kami telah menyaksikan perhitungan ini terjadi di ratusan proyek. Untuk run di bawah 200 hingga 300 unit, ICT penuh jarang membayar dirinya sendiri.

Alternatifnya bukanlah meninggalkan pengujian ketat, tetapi menggantikan model bergantung fixture dengan strategi yang lebih ramping dan cepat yang dibangun dengan boundary scan, pengujian tanpa vektor, dan pengujian fungsi fokus. Kombinasi ini memberikan cakupan kesalahan yang sepadan, menghilangkan hambatan fixture, dan menyediakan loop debug yang lebih cepat saat ditemukan kesalahan. Pergeseran ini bukanlah ideologi; ini adalah tanggapan praktis terhadap gesekan matematis dan mekanis yang diberlakukan ICT pada produksi volume rendah dan gesit.

Asumsi ICT dan Di Mana Itu Tidak Berfungsi

Pengujian sirkuit menjadi standar industri di era desain volume tinggi dan stabil. Modelnya sederhana: berinvestasi besar di awal dalam fixture pengujian khusus dan penguji canggih, lalu memanfaatkan investasi tersebut di antara puluhan ribu unit identik. Dengan waktu pengujian per unit yang diukur dalam detik, biaya marginal per papan secara efektif nol setelah biaya tetap diserap. Untuk produsen elektronik konsumen yang menjalankan 50.000 unit SKU yang sama, perhitungan ini tidak terbantahkan.

Model produksi itu sudah pecah. Pembuatan elektronik modern semakin melayani pasar dengan campuran tinggi dan volume rendah. Siklus hidup produk lebih singkat, iterasi desain lebih sering, dan kustomisasi adalah keunggulan kompetitif. Sebuah perusahaan mungkin memproduksi 150 unit satu varian, melakukan iterasi desain, lalu memproduksi 200 unit berikutnya. Asumsi bahwa satu fixture akan menguji ribuan papan identik tidak lagi berlaku. Biaya tetap yang tidak signifikan dalam volume tinggi menjadi memberatkan saat dibagi di antara beberapa ratus unit.

Model ini rusak ketika total biaya infrastruktur ICT melebihi biaya yang disesuaikan risiko dari strategi alternatif. Ambang batas ini bukan sembarangan. Ini merupakan fungsi dari biaya fixture, waktu rekayasa, waktu tunggu produksi, dan cakupan yang dapat dicapai melalui metode tanpa fixture. Untuk sebagian besar desain papan, ambang batas ini berada antara 200 dan 300 unit.

perangkap Biaya Tetap dari Pengujian Sirkuit

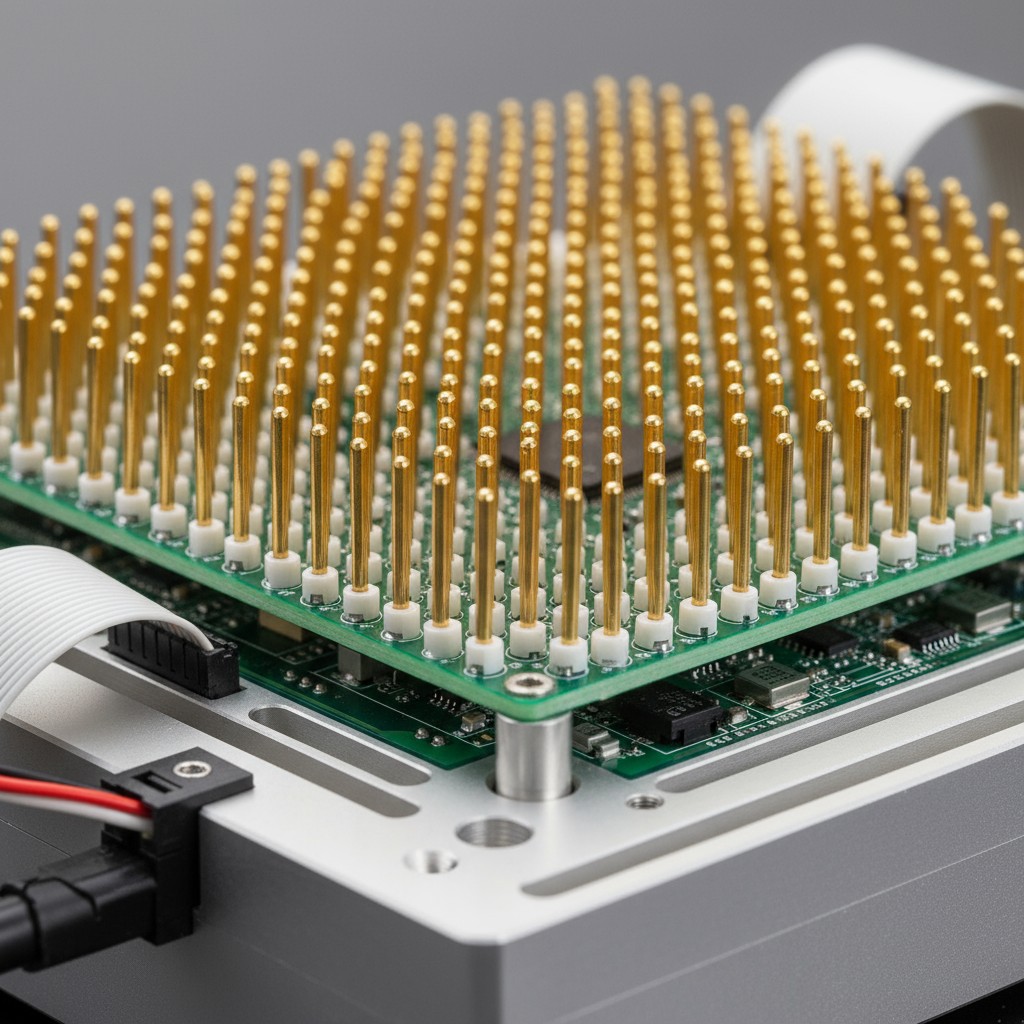

Meskipun fixture adalah biaya yang paling terlihat dari ICT, beban ekonomi sebenarnya jauh lebih luas. Fixture ICT kustom bukanlah pembelian off-the-shelf; itu adalah artefak yang direkayasa, dibangun khusus untuk tata letak papan tertentu. Proses desain memerlukan penerjemahan netlist papan dan penempatan komponen ke dalam struktur mekanik yang dipasang dengan probe pengujian bertekanan pegas, masing-masing diselaraskan ke titik pengujian tertentu dengan presisi sub-milimeter. Fixture harus memperhitungkan toleransi komponen, deformasi papan, dan keausan probe. Kemudian harus divalidasi dan diperbaiki—sebuah proses yang sering mengungkapkan masalah yang tidak terduga dengan akses probe atau integritas sinyal.

Biaya dan Waktu Tunggu Rekayasa Fixture

Biaya rekayasa untuk fixture yang agak kompleks biasanya berkisar antara $8.000 dan $15.000. Papan berdensitas tinggi dengan komponen pitch halus atau akses titik uji terbatas dapat menaikkan angka tersebut hingga $25.000 atau lebih. Ini murni biaya antarmuka mekanik dan listrik khusus yang diperlukan untuk menghubungkan papan ke peralatan ICT, terpisah dari biaya kapital dari penguji itu sendiri.

Waktu tunggu sama pentingnya. Setelah desain papan diselesaikan, desain dan pembuatan fixture biasanya memakan waktu dua hingga empat minggu, hingga enam minggu untuk desain yang kompleks. Selama periode ini, produksi terhenti. Papan mungkin dirakit, tetapi mereka tidak dapat diuji. Mereka tinggal di inventaris, menunggu. Jika desain berubah selama jendela ini—yang umum dalam pengenalan produk baru—fixture harus direvisi atau dibuang. Waktunya kembali reset.

Matematika Break-even untuk Produksi Volume Rendah

Perangkap ekonomi menjadi jelas ketika biaya fixture dibagi dengan jumlah unit. Fixture seharga $12.000 untuk produksi 100 unit menambah beban $120 pada setiap papan. Untuk papan dengan tagihan bahan sebesar $500, itu adalah overhead pengujian sebesar 24 persen. Bahkan jika proses ICT cepat, efisiensi ekonomi buruk. Fixture yang sama, jika diambil amortisasinya untuk 500 unit, menurunkan biaya per unit menjadi $24, overhead lima persen yang jauh lebih dapat diterima. Perbedaannya murni fungsi volume.

Titik impas adalah ketika total biaya ICT—termasuk rekayasa, pengaturan, dan biaya peluang dari waktu tunggu—sama dengan biaya alternatif tanpa fixture. Untuk strategi yang menggabungkan boundary scan, pengujian tanpa vektor, dan pengujian fungsional secara lean, biaya infrastruktur jauh lebih rendah. Boundary scan tidak memerlukan fixture, dan pengujian tanpa vektor menggunakan sensor yang dapat digunakan ulang yang bekerja tanpa kontak mekanis. Fixture pengujian fungsional apa pun biasanya minimal dan umum, bukan artefak spesifik papan yang memerlukan minggu-minggu rekayasa.

Pada volume produksi di bawah 200 unit, ekonomi ICT runtuh. Di bawah 300 unit, kasusnya marginal, tergantung pada kompleksitas papan. Hanya di atas 300 unit untuk desain yang stabil dan tidak iteratif ICT mulai kembali membuat ekonomi menjadi jelas.

Apa Itu Boundary Scan dan Pengujian Tanpa Vektor Sebenernya

Alternatif dari pengujian berbasis fixture bukanlah kompromi dalam ketelitian tetapi pergeseran ke metode yang memanfaatkan infrastruktur desain yang ada dan pengukuran non-kontak. Alat-alat ini dikembangkan untuk mengatasi tren yang sama yang merusak ICT: peningkatan kepadatan papan dan menyusutnya akses ke titik pengujian fisik.

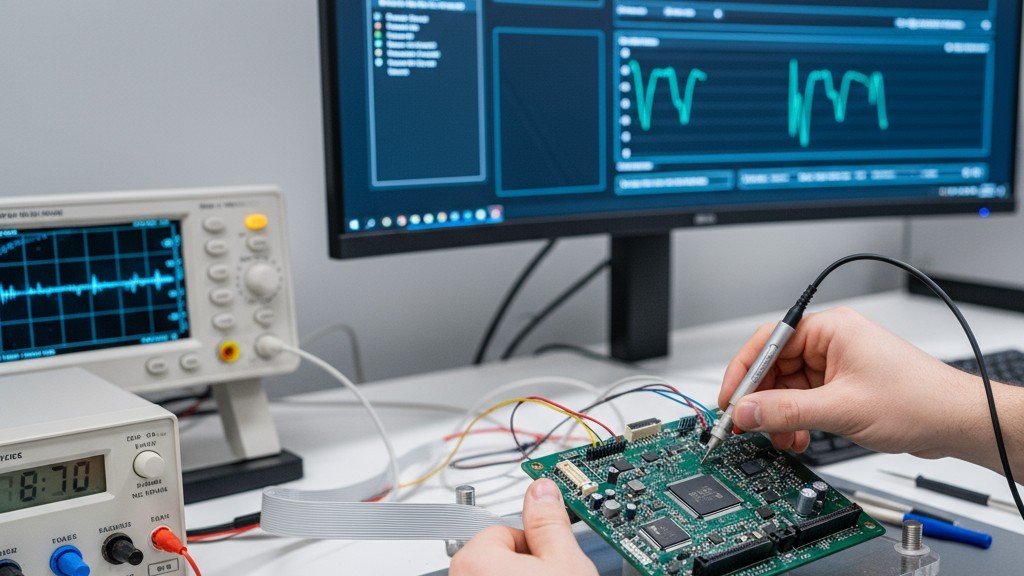

Boundary scan, yang diformalisasi dalam standar IEEE 1149.1 (yang umum dikenal sebagai JTAG), menyisipkan logika pengujian langsung ke dalam sirkuit terpadu papan. Chip yang kompatibel menyertakan rantai sel pada tiap pin input dan output. Selama pengujian, antarmuka empat kawat sederhana memindahkan pola ke dalam sel-sel ini, mengendalikan kondisi logika di jalur papan. Kondisi yang dihasilkan kemudian diambil dan dipindahkan keluar untuk analisis, memungkinkan penguji mengendalikan dan mengamati sinyal di tingkat pin tanpa kontak fisik. Metode non-invasif ini sangat efektif dalam mendeteksi hubung singkat, hubungan terbuka, dan kesalahan stuck-at antara perangkat yang kompatibel.

Pengujian tanpa vektor melengkapi ini dengan menggunakan pengukuran kapasitor dan induktif untuk mendeteksi kesalahan di seluruh papan. Array sensor yang diposisikan dekat papan mengukur tanda elektromagnetik dari komponen dan jalur yang terpasang. Hubungan singkat menciptakan kopling kapasitor yang terukur; hubungan terbuka menunjukkan perubahan impedansi karakteristik. Metode ini cepat, tanpa kontak, dan dapat menyimpulkan keberadaan komponen, polaritas, dan perkiraan nilai, membuatnya efektif dalam menangkap cacat manufaktur besar seperti komponen hilang, dioda terbalik, atau jalur yang terhubung.

Perbandingan Cakupan: Angka di Balik Trade-Off

Keberatan utama terhadap meninggalkan ICT adalah cakupan. Sementara ICT, secara prinsip, dapat mengakses setiap node pada papan dengan cukup titik uji, klaim bahwa alternatif lebih buruk tidak lengkap. Pertanyaan yang sebenarnya adalah apakah mereka mencapai cakupan yang cukup untuk menangkap kesalahan yang sebenarnya terjadi, dan jika pengujian fungsional yang terfokus dapat menutup celah yang tersisa.

Apa yang Dicakup oleh Boundary Scan

Cakupan pemindaian boundary bergantung pada berapa banyak komponen di papan yang sesuai dengan standar JTAG. Untuk papan yang didominasi oleh logika digital—mikroprosesor, FPGA, memori—cakupannya cukup luas. Rantai scan dapat menguji interkoneksi antara perangkat ini dengan tingkat deteksi kesalahan yang melebihi 95 persen untuk hubungan pendek, hubungan terbuka, dan Fault Stuck-At. Papan di mana 80 persen komponen sesuai akan mencapai cakupan bersih sekitar 70 hingga 85 persen. Bagian analog, komponen diskret, dan bagian warisan tidak terlihat oleh metode ini. Namun, untuk desain yang banyak menggunakan digital, scan boundary saja memberikan cakupan yang sebanding dengan ICT untuk lapisan interkoneksi, di mana sebagian besar kesalahan perakitan terjadi.

Apa yang Ditambahkan oleh Pengujian Tanpa Vektor

Pengujian tanpa vektor mengisi kekosongan yang ditinggalkan oleh pemindaian batas, terutama untuk komponen pasif dan cacat rakitan besar. Pengukuran kapasitor dapat mendeteksi resistor yang hilang, nilai kapasitor yang salah, dan dioda yang dibalik. Meskipun kurang tepat daripada pengukuran langsung ICT, ini adalah layar yang efektif untuk kesalahan paling umum: komponen yang salah, komponen hilang, atau ketidaksesuaian yang parah. Ini menambahkan 10 hingga 20 persen lagi ke total cakupan kesalahan, memberikan lapisan verifikasi non-kontak untuk bagian yang tidak dapat dilihat oleh pemindaian batas.

Kesenjangan yang Tersisa dan Bagaimana Pengujian Fungsional Lean Menutupnya

Gabungan boundary scan dan pengujian tanpa vektor masih menyisakan celah dalam validasi fungsional dan kinerja analog. Sebuah komponen bisa hadir dan terhubung dengan benar tetapi tetap gagal beroperasi sesuai spesifikasi. Sebuah catu daya mungkin memberikan tegangan tetapi dengan riak yang berlebihan. Di sinilah peran pengujian rangkaian fungsional lean (FCT). Tidak seperti pengaturan ICT lengkap, FCT lean memvalidasi bahwa papan menjalankan fungsi yang dimaksudkan di bawah kondisi yang realistis. Ia mengalirkan daya, merangsang input, dan mengukur output. Untuk pengendali motor, mungkin memverifikasi生成 PWM; untuk papan komunikasi, memeriksa transmisi data bebas kesalahan. Pengujian fungsional melengkapi pengujian struktural, mendeteksi kesalahan yang tidak bisa dilihat metode lain.

Kombinasi dari ketiga metode ini biasanya mencapai cakupan kesalahan sebesar 85 hingga 95 persen. Ini bukan 100 persen, tetapi ICT juga tidak dalam praktiknya. Karena keterbatasan titik uji dan keausan probe, cakupan ICT dunia nyata seringkali kurang dari maksimum teoritisnya. Perbedaannya jauh lebih kecil daripada penalti dalam biaya dan waktu tunggu.

Keunggulan Loop Debug

Cakupan pengujian hanyalah setengah dari nilai; sisanya adalah kecepatan dan ketepatan isolasi kesalahan. Pengujian yang mendeteksi kesalahan tetapi memberikan diagnostik yang samar meningkatkan waktu dan biaya yang diperlukan untuk menemukan akar penyebab.

Sementara ICT hebat dalam mendeteksi kesalahan, diagnosa-nya bisa sangat samar. Penguji mungkin melaporkan bahwa node 47 singkat ke ground, tetapi tidak menjelaskan mengapa atau di mana. Teknisi harus menelusuri skema, menemukan net, dan secara visual memeriksa area tersebut—sebuah proses yang bisa memakan waktu berjam-jam pada papan berlapis banyak yang padat.

Diagnostik pemindaian batas berbeda secara fundamental. Karena rangkaian scan tertanam dalam komponen, pengujian mengisolasi kerusakan ke pin dan perangkat tertentu. Hubungan singkat antara dua jaringan diidentifikasi oleh pin perangkat yang terlibat secara tepat, mempersempit pencarian ke beberapa milimeter persegi. Pembukaan terdeteksi antara pasangan driver dan receiver tertentu. Output diagnostik bukan kode kesalahan. Ini adalah peta. Presisi ini berarti kerusakan yang membutuhkan waktu satu jam untuk debug dengan data ICT sering dapat diselesaikan dalam 10 hingga 20 menit dengan pemindaian batas. Untuk satu jalur 100 unit dengan tingkat cacat tipikal, waktu debug kumulatif yang disimpan dapat melebihi 10 jam.

Waktu Tunggu dan Fleksibilitas: Nilai Tersembunyi

Argumen ekonomi terhadap ICT untuk volume rendah cukup meyakinkan, tetapi penalti waktu tunggu sama pentingnya. Proses rekayasa fixture selama dua hingga empat minggu memberlakukan penundaan wajib antara pembekuan desain dan kesiapan pengujian. Untuk pengenalan produk baru, di mana waktu ke pasar sangat penting, penundaan ini sering kali tidak dapat diterima.

Pemindaian batas dan pengujian tanpa vektor menghilangkan penantian ini. Pengaturan pengujian dapat dikonfigurasi dalam jam atau hari, bukan minggu, memungkinkan papan beralih dari perakitan ke pengujian ke pengiriman dalam aliran terus menerus. Fleksibilitas ini penting ketika desain mengalami iterasi. Jalur prototipe awal mungkin mengungkapkan masalah yang memerlukan perubahan tata letak papan. Dengan ICT, setiap revisi memerlukan fixture baru atau yang telah diperbaiki, menimbulkan biaya dan waktu tunggu yang sama sekali baru. Pola pengujian pemindaian batas, yang dihasilkan dari netlist, diperbarui secara otomatis dengan desain. Ini menciptakan strategi pengujian yang mendukung pengembangan iteratif daripada menghukumnya.

Kapan Masih Harus Memilih TIK

Namun, kasus terhadap ICT volume rendah tidak mutlak. Desain dan konteks produksi tertentu masih membenarkan investasi tersebut.

Papan dengan bagian analog tinggi kepadatan atau RF adalah kandidat buruk untuk strategi tanpa fixture murni. Komponen analog tidak memiliki logika pemindaian batas, dan karakteristik kinerja kritis seperti gain atau noise fase tidak dapat diverifikasi secara struktural. Jika sirkuit analog atau RF mewakili lebih dari 40 persen dari fungsi papan, kasus untuk ICT menjadi sangat kuat.

Industri yang didorong oleh kepatuhan seperti medis, dirgantara, dan otomotif sering beroperasi di bawah regulasi yang mengharuskan cakupan pengujian atau metode tertentu. Jika standar pengatur mengharuskan pengujian sirkuit dalam atau akses node setara, strategi alternatif mungkin tidak cukup. Di sini, biaya ICT adalah biaya yang tidak bisa dinegosiasikan untuk masuk pasar.

Akhirnya, jalur yang jelas dan komitmen menuju produksi volume tinggi mengubah perhitungannya. Jika sebuah jalur awal 150 unit diharapkan akan meningkat menjadi 1.000 unit dalam enam bulan, biaya fixture dialokasikan ke seluruh volume yang diperkirakan. Ini membutuhkan kepercayaan tinggi pada perkiraan dan desain yang stabil, tetapi dapat membuat investasi awal menjadi berharga.

Membangun Strategi Pengujian Alternatif

Mengganti ICT bukan sekadar pertukaran sederhana; ini adalah rekonstruksi arsitektur pengujian menjadi strategi berlapis, di mana setiap lapisan menangkap kesalahan yang mungkin terlewatkan oleh lapisan lain.

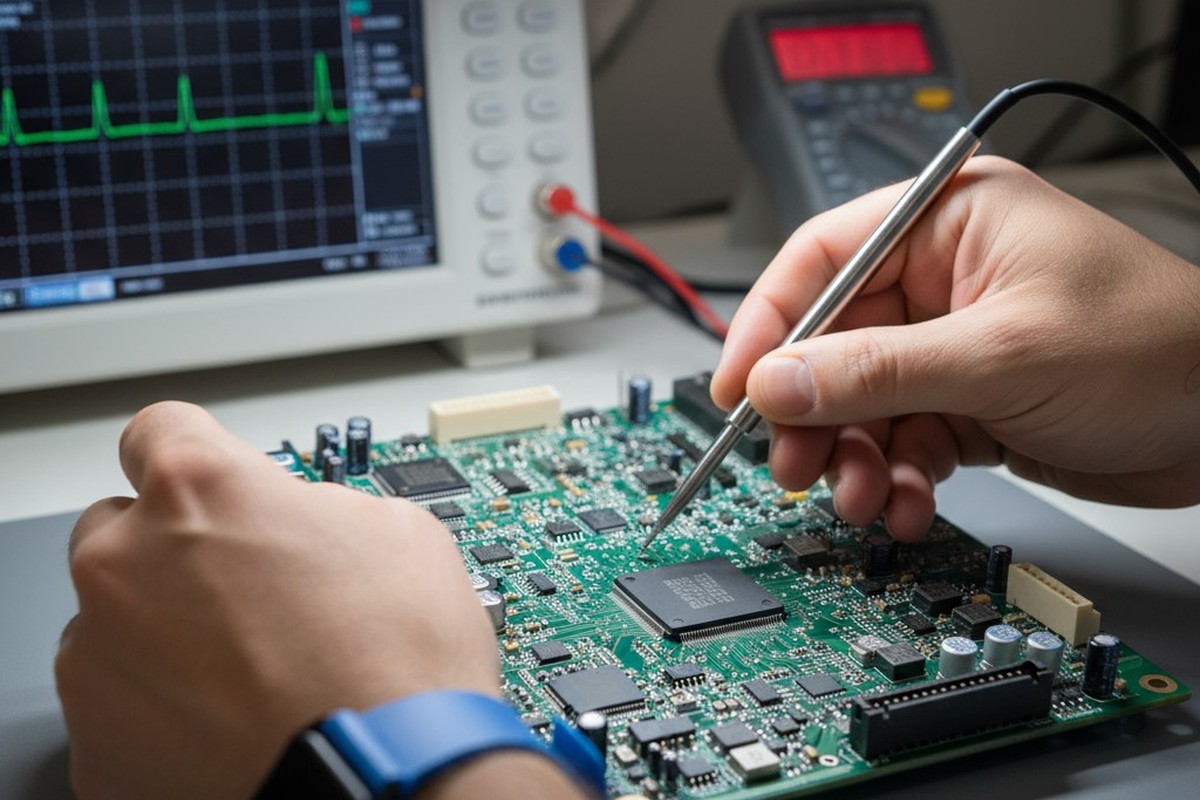

Proses harus berurutan. Lapisan pertama adalah pemindaian batas, yang berjalan cepat pada semua perangkat yang mematuhi untuk menangkap kesalahan interkoneksi pada bagian digital papan. Papan yang gagal diberi tanda untuk diperbaiki segera, mencegah kegagalan katastrofik saat daya dinyalakan nanti. Lapisan kedua adalah pengujian tanpa vektor, yang berjalan di seluruh papan untuk mendeteksi komponen pasif yang hilang atau salah, shorts besar, dan kesalahan polaritas. Ini mencakup komponen dan jaringan yang tidak terlihat oleh rangkaian scan.

Lapisan ketiga dan terakhir adalah pengujian fungsi yang terfokus. Setelah kesalahan struktural disaring sebelumnya, papan diberdayakan untuk memvalidasi fungsi kritisnya di bawah kondisi operasi yang realistis. Ruang lingkup disesuaikan dengan tujuan papan—memverifikasi akurasi ADC pada papan akuisisi data atau pengaturan beban pada catu daya. Urutan ini memastikan bahwa kesalahan yang merusak dapat diketahui sejak dini dan secara tidak merusak, meminimalkan waktu debug pada kegagalan fungsi yang lebih kompleks.

Untuk papan dengan kompleksitas hibrida—misalnya inti digital padat yang dikelilingi oleh pengkondisian sinyal analog—strategi hibrida mungkin paling baik. Fixture ICT parsial dapat dirancang untuk menyelidiki hanya bagian analog yang penting, meninggalkan bagian digital untuk pemindaian batas. Ekonomi fixture parsial lebih menguntungkan, mengurangi biaya dan waktu tunggu sambil tetap memberikan cakupan yang diperlukan untuk seluruh desain.