Sebuah papan bisa terlihat bersih. Bisa melewati angka ionik massal yang disorot dengan warna hijau di sertifikat. Dan tetap bisa bocor di lapangan.

Ini bukan sikap sinis. Ini geometri, kelembapan, dan waktu yang mengejar pengukuran yang salah tempat.

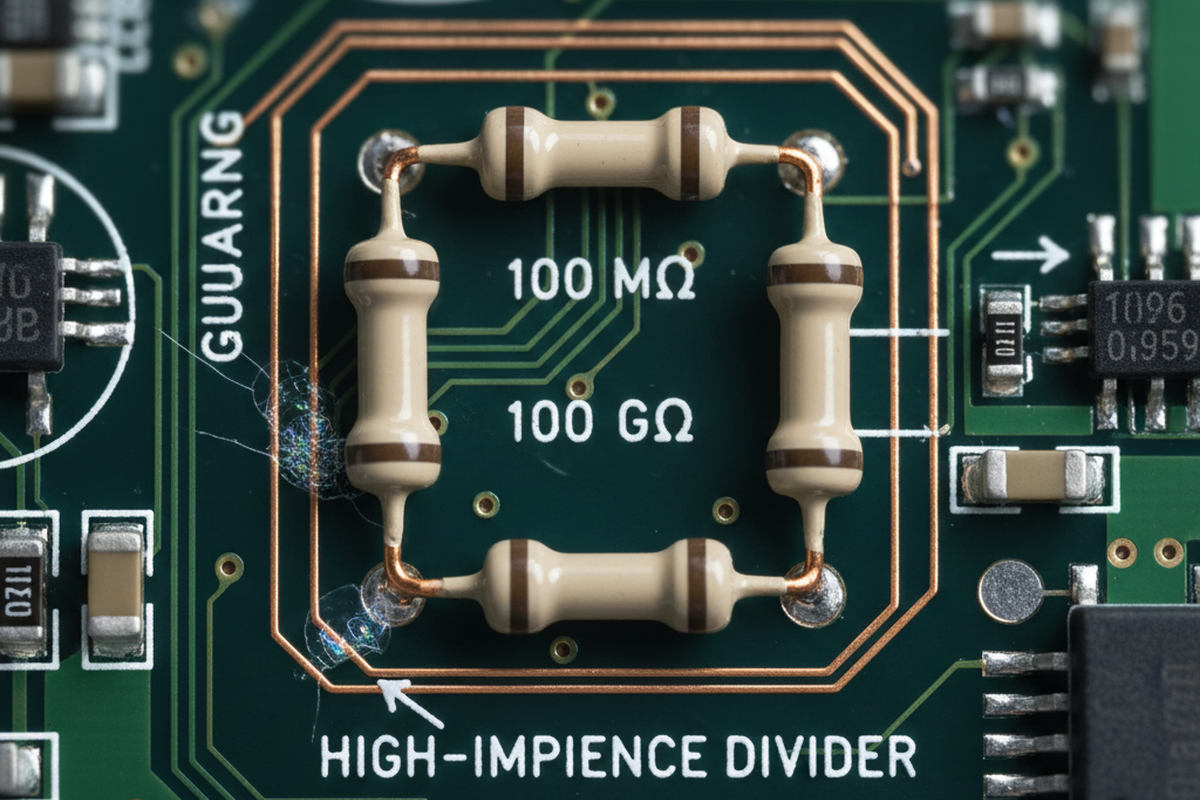

Pertimbangkan pola yang familiar dalam sensing industri: sebuah platform dengan pembagi impedansi tinggi (100 MΩ hingga 1 GΩ) berperilaku sempurna di meja uji dan melewati pemeriksaan masuk, namun mulai menunjukkan drift offset setelah penempatan di pantai. Argumen di ruangan selalu sama: pembuat kontrak memiliki laporan ROSE; memenuhi batas; seharusnya baik-baik saja. Sementara itu, satu-satunya pengaturan yang mengungkapkan drift adalah paparan kelembapan bias—pikirkan 85%RH dengan bias diterapkan di seluruh jaringan sensitif—di mana kegagalan muncul perlahan, seperti pengatur waktu.

Ketika Anda membagi kegagalan ke wilayah tertentu (biasanya daerah LGA/QFN dengan jarak rendah dekat cincin penjaga), cerita 'bersih massal' runtuh. Ekstraksi lokal di sekitar hotspot mengungkapkan kontaminasi yang tidak pernah tertangkap oleh angka papan lengkap. Tindakan koreksi yang benar-benar menggerakkan jarum bukanlah heroik. Mereka adalah disiplin biasa: tren resistivitas bilas, aturan pemuatan yang mencegah bayangan, dan disiplin flux rework yang ditegakkan oleh revisi instruksi kerja yang terkait dengan ECO.

Di sini, jalan pintas mulai bertambah: “Bisakah kita hanya melapisi konformal?” “Bisakah kita hanya meminta sertifikat yang lebih bersih?” “Bisakah kita hanya meningkatkan jarak?” Pertanyaan-pertanyaan ini menenangkan karena terdengar seperti penutupan. Mereka tidak.

Sertifikat kebersihan adalah data input. Itu bukan bukti bahwa permukaan impedansi tinggi atau tegangan tinggi akan tetap isolasi di seluruh kelembapan, bias, dan penuaan.

Bukti nyata terlihat berbeda: validasi yang terkait mekanisme yang cocok dengan mode kegagalan, plus kontrol proses yang membuat hasil pembersihan dapat direproduksi—termasuk bagian dari manufaktur yang semua orang harap tidak dihitung, seperti rework dan touch-up solder selektif.

Apa arti “Bersih” Ketika Nanoamps Penting

Untuk rakitan impedansi tinggi dan HV, “bersih cukup” tidak bisa hanya berarti “kami mengekstraksi ion dari area besar dan jumlahnya di bawah batas.” Tujuannya lebih sempit dan lebih menuntut: mencegah drift kebocoran dan degradasi isolasi di seluruh musim, profil penyimpanan, dan waktu di bawah bias. Ini adalah tujuan keandalan listrik, berbeda dari standar kosmetik. Film residu tipis dan berpatch yang tidak akan pernah memicu alarm saat inspeksi visual dapat menjadi aktif secara listrik dalam kelembapan. Setelah bias diterapkan, itu berhenti menjadi kontaminan pasif dan menjadi bagian dari jalur konduksi.

Secara mekanis, bahan-bahannya sederhana: residu ionik, kelembapan, bias, waktu, dan geometri yang memungkinkan sebuah film menjembatani apa yang diasumsikan oleh diagram jarak sebagai udara. Bagian yang sulit adalah bahwa geometri yang Anda pedulikan sering tersembunyi. Zona di bawah komponen—QFN, LGA, BGA, pin dengan pitch rapat, dan tepi perekat atau staking—adalah tempat residu terperangkap dan di mana jangkauan pencucian paling buruk. Ini juga tempat tepat di mana tim tidak dapat melakukan inspeksi dengan baik, dan tepat di mana pengujian ekstraksi massal mengabaikan masalah. Jika seseorang bertanya, “Bagaimana Anda membersihkan di bawah QFN/LGA?” mereka bukan bertanya pertanyaan pemula. Mereka sedang menyelidiki inti dari apakah cerita pembersihan itu nyata atau hanya sandiwara.

Secara praktis, validasi harus dilokalisasi di sekitar node sensitif. Cincin penjaga di sekitar input elektrometer, jaringan pembagi nilai tinggi, atau wilayah creepage HV bukanlah “hanya area lain dari papan.” Itu adalah hotspot dengan fisika kegagalan yang berbeda. Jalur kebocoran sering mengikuti fitur biasa: tepi masker solder, lingkungan via-in-pad, atau perimeter paket dengan jarak rendah di mana residu flux terperangkap dan diaktifkan oleh kelembapan. Inilah sebabnya mengapa “hanya meningkatkan jarak” jarang menyelesaikan keandalan HV pada rakitan yang masih memiliki residu: film permukaan tidak menghormati jarak nominal yang digambar di CAD.

Shiny bukanlah sebuah pengukuran.

Kebenaran yang tidak nyaman adalah bahwa banyak program memvalidasi pembersihan seolah-olah kontaminasi bersifat seragam dan terlihat. Kegagalan impedansi tinggi dan HV biasanya tidak demikian.

Jejak Mekanisme: Residue → Kelembapan → Bias → Kebocoran (dan Cara Membuktikannya)

Rencana validasi dimulai dengan menyatakan mekanisme kegagalan dalam satu kalimat. Untuk topik ini, biasanya konduksi permukaan dan drift (kadang-kadang berkembang menuju migrasi elektrokimia), bukan kerusakan langsung. Kemudian rencana mencantumkan kondisi yang diperlukan: residu ionik di suatu tempat di permukaan atau terperangkap di bawah paket, kelembapan cukup tinggi untuk menciptakan lapisan konduktif, medan listrik yang diterapkan di seluruh wilayah (bias), dan cukup waktu agar kebocoran stabil dalam perilaku “normal baru”. Komponen waktu ini adalah apa yang sering diremehkan tim; pengujian laboratorium singkat, sementara paparan lapangan berlangsung lama.

Setelah rantai sebab-akibat itu dinamai, rencana memetakan di mana setiap bahan tersembunyi di rakitan. Di bawah LGA/QFN dengan jarak rendah dekat pembagi 100 MΩ adalah perangkap klasik: wilayah ini secara elektrik sensitif, secara fisik sulit dibersihkan, dan mudah terkontaminasi selama pengerjaan ulang. Ketika sebuah program melihat pengelompokan drift setelah penempatan pantai atau penyimpanan gudang musim panas, itu jarang berarti papan menjadi “lebih kotor” secara dramatis. Itu berarti lingkungan akhirnya menyediakan kelembapan yang dibutuhkan untuk menyelesaikan rangkaian melintasi film residu yang sudah ada, dan bias membuat jalur kebocoran menjadi konsisten.

Perendaman kelembapan bias bukanlah pengujian mewah dalam konteks ini; ini adalah cara untuk mereproduksi bahan-bahan nyata dari kegagalan lapangan. Dan memiliki standar pemalsuan: jika kelembapan bias pada tingkat stres yang relevan tidak mengubah resistansi isolasi dari waktu ke waktu di wilayah hotspot, hipotesis residu kehilangan kekuatan.

Ini juga tempat di mana kebingungan “ROSE pass = aman?” harus ditangani. Pengujian ionik massal bisa menjadi layar yang berguna, tetapi mereka tidak menjamin bahwa satu sentimeter persegi di bawah paket jarak rendah dekat cincin penjaga bersih. Mereka juga jarang meniru kondisi operasi—kimia ekstraksi, pengambilan sampel lokasi, dan sensitivitas terhadap residu lokal sangat penting. Sebuah laporan bisa “benar” dan tetap tidak relevan terhadap mekanisme kegagalan. Pertanyaan validasi bukanlah “Apakah ini memenuhi angka?” Melainkan “Apakah rakitan ini mempertahankan perilaku isolasi di bawah kelembapan dan bias selama konstanta waktu yang akan dilihat produk?”

Tidak ada ambang “residu yang dapat diterima” universal yang dapat diakui secara jujur untuk semua desain impedansi tinggi/HV. Tingkat yang dapat diterima bergantung pada skala impedansi (nanoampere bukan mikroampere), gradien tegangan, geometri, dan lingkungan. Cara mengelola ketidakpastian itu adalah korelasi, bukan kepercayaan. Pilih strategi papan atau kupu-kupu yang mewakili, terapkan profil kelembapan bias yang membatasi kondisi lapangan yang masuk akal (85°C/85%RH adalah pembatas umum, tetapi bukan satu-satunya), dan korelasikan indikator kontaminasi lokal (ekstraksi lokal di sekitar hotspot, pengujian gaya SIR/ECM, resistansi isolasi vs. waktu) terhadap kinerja listrik yang Anda pedulikan.

Garis utama sederhana: jika kegagalan melibatkan kelembapan + bias + waktu, maka validasi harus melibatkan kelembapan + bias + waktu, di tempat yang tepat.

Paket Validasi Minimum Viable (Apa yang Dibuktikan, Apa yang Tidak)

Paket validasi minimum yang layak bukanlah versi yang dilemahkan dari program yang sempurna. Ini adalah kompromi yang disengaja: cukup untuk menyingkirkan loop kepercayaan palsu yang paling umum tanpa mengubah proyek menjadi usaha ilmiah yang terbuka. Ini berhenti memperlakukan sertifikat sebagai garis finis. Daripada menambah pengujian demi pengujian, paket ini mewakili seperangkat kontrol dan bukti terkecil yang secara bermakna mengurangi kemungkinan drift/kembalinya kebocoran.

Setidaknya, program membutuhkan dua kategori: (1) bukti penyaringan/proses bahwa pembersihan terkendali dan dapat diulang, dan (2) setidaknya satu pengujian listrik yang terkait mekanisme yang fokus pada hotspot.

Di sisi proses, program harus menuntut artefak yang dapat diaudit dari jalur pembersihan dan CM, bukan pernyataan pemasaran. Program yang konsisten stabil memiliki ciri khas tertentu: resep pencucian yang terdokumentasi, catatan pemeliharaan yang mencakup inspeksi/pembersihan nosel pada pencuci inline berair dengan batang semprot, dan metode pemuatan yang menghindari bayangan (aturan jarak keranjang yang benar-benar diikuti, bukan hanya ditempelkan ke pintu).

Kualitas bilas layak mendapatkan perhatian yang tidak proporsional karena mudah diabaikan dan mengubah hasil. Logging resistivitas bilas DI yang tren dari waktu ke waktu lebih informatif daripada berdebat tentang kimia yang “lebih kuat” sementara kualitas air bilas mengambang. Di sinilah kecocokan bahan—rumah konektor, label, silikon/underfill, gasket—berada. Penggantian kimia yang membuat plastik keruh atau mengembang gasket hanya dapat “menyelesaikan” kontaminasi dan menciptakan masalah keandalan yang berbeda. Pemeriksaan kupu-kupu dasar dan tinjauan lembar data/SDS adalah wajib saat substitusi dilakukan.

Di sisi mekanisme, pilih satu pengujian yang menyerupai bahan kegagalan dan satu pengukuran yang menargetkan hotspot. Itu bisa berupa perendaman kelembapan bias dengan bias yang terdefinisi di seluruh wilayah sensitif (jarak HV atau area pembagi nilai tinggi) yang dikombinasikan dengan tren resistansi isolasi vs. waktu, atau pengujian SIR/ECM yang berorientasi pada proses dan bahan yang digunakan. Pasangkan dengan ekstraksi lokal di sekitar wilayah risiko tinggi (lingkungan cincin penjaga, di bawah paket jarak rendah) daripada rata-rata seluruh papan. Tujuannya adalah membuat program sensitif terhadap cara kegagalan ini sebenarnya terjadi: lokal, diaktifkan oleh kelembapan, distabilkan oleh bias, dan terungkap seiring waktu.

Pengadaan dan troubleshooting awal sering memulai dengan pertanyaan yang salah: “Pembersih mana yang harus kita beli?” Jika hasil pembersihan berubah saat papan disusun ulang dalam keranjang atau saat nosel semprot dibersihkan dari sumbatan, tim tidak memiliki masalah kimia. Mereka memiliki masalah kemampuan proses. Pemilihan kimia penting—terutama dengan jenis fluks dan batasan bahan—tetapi ini adalah tombol terakhir yang diputar setelah mekanik, pemuatan, kualitas bilas, dan pemantauan terlihat dan dikendalikan.

Dan tidak: lapisan konformal bukanlah rencana pembersihan. Lapisan dapat mengurangi risiko, atau dapat menyegel residu ke dalam rakitan dan mengubahnya menjadi sumber drift jangka panjang. Jika lapisan digunakan, itu membutuhkan kontrol prosesnya sendiri (strategi masking, pengukuran ketebalan yang dicatat per lot, verifikasi curing, dan rencana pengerjaan ulang) dan tetap tidak dapat diperlakukan sebagai izin untuk melewati validasi kebersihan hotspot.

Rework dan Solder Selektif: Titik Buta Validasi

Jika rencana validasi mengabaikan rework, itu memvalidasi proses manufaktur fiktif.

Build pilot dapat melewati ICT dan terlihat stabil, lalu mengembangkan kegagalan impedansi tinggi yang intermiten setelah sehari di ruang uap dengan bias diterapkan. Post-mortem sering mengungkapkan sesuatu yang menyakitkan biasa: dua teknisi melakukan “touch-up” yang sama menggunakan flux dan kebiasaan pembersihan yang berbeda. Salah satu menggunakan pena flux dan kapas kapas dengan IPA; yang lain menggunakan flux berbeda dan bahan lap yang mengelupas serat. Instruksi kerja yang mengatakan “bersihkan sesuai kebutuhan” hanyalah sebuah keinginan. Ketika kegagalan dikaitkan kembali ke catatan MRB atau NCR dan kemudian ke meja rework, pola tersebut berhenti terlihat acak. Itu mulai terlihat seperti proses manufaktur kedua yang tidak terkendali.

Inilah mengapa rework dan solder selektif harus termasuk dalam ruang lingkup validasi. Kontrolnya eksplisit: daftar flux terkunci (nomor bagian dilacak di gudang alat), pelarut dan bahan lap yang didefinisikan (bukan “resep rakyat” tergantung orangnya), aturan routing yang jelas untuk kapan papan harus kembali melalui pencucian setelah touch-up, dan kriteria verifikasi yang sesuai dengan mekanisme kegagalan (bukan hanya “terlihat bersih”). Jika sebuah program harus melalui ECO dan perbaikan layanan lapangan, validasi harus mencakup setidaknya satu siklus rework dalam matriks pengujian untuk wilayah hotspot, karena di situlah residu disuntikkan secara terlambat dan diam-diam.

Ada juga ketidakpastian halus tetapi penting untuk dikelola di sini: “no-clean” pada label flux bukan jaminan fisika, dan formulasi bervariasi. Perlakukan jenis flux sebagai variabel terkendali. Ketika berubah, lakukan validasi ulang perilaku hotspot di bawah kelembapan dan bias. Jika tidak, program berakhir “divalidasi” untuk flux yang bukan yang digunakan selama touch-up yang berantakan dan mendesak waktu.

Volume rework bisa kecil dan tetap mendominasi risiko karena node yang sensitif terlokalisasi. Risikonya sebanding dengan apakah kejadian rework menyentuh sentimeter persegi yang salah, bukan berapa banyak papan yang di-rework secara total.

Red‑Teaming artefak kenyamanan (ROSE, CoC, Visual, Hipot)

Mindset arus utama sederhana: capai KPI kebersihan, lulus hipot, kirim. Artefak kenyamanan ditumpuk seperti perisai: laporan ROSE, CoC pemasok, inspeksi visual, mungkin pewarna pelacak UV, dan lulus hipot di akhir. Setiap artefak mengukur sesuatu yang nyata, tetapi tidak satu pun dari mereka, sendiri, mengukur “perakitan ini tidak akan mengembangkan konduksi permukaan dan drift di kelembapan di bawah bias seiring waktu.”

ROSE adalah layar bulk kasar; itu tidak dirancang untuk memetakan residu lokal di bawah perimeter QFN atau di tepi cincin penjaga. CoC pemasok menggambarkan bahan masuk, bukan keadaan papan yang dirakit setelah reflow, solder selektif, penanganan, dan rework. Inspeksi visual (bahkan dengan bantuan UV) membantu menangkap residu kasar dan masalah pengerjaan, tetapi film tipis yang aktif secara listrik bisa hampir tidak terlihat. Hipot membuktikan ketahanan saat tertentu di bawah pengaturan tertentu; itu tidak secara otomatis memprediksi drift konduksi permukaan di 85%RH dengan bias yang diterapkan selama berjam-jam atau berhari-hari. Ini bukan kritik terhadap pengujian. Mereka adalah pengingat batasannya.

Jika produk peduli terhadap nanoamp, harus divalidasi dengan nanoamp—atau dengan pengujian yang secara andal memprediksi mereka.

Rebuild pragmatis mempertahankan artefak kenyamanan sebagai layar, tetapi berhenti menggunakannya sebagai penutup. Tambahkan satu pengujian bukti yang terkait mekanisme di hotspot di bawah kelembapan dan bias selama waktu yang relevan, dan padukan dengan pengukuran kontaminasi lokal atau bukti gaya SIR/ECM. Penambahan tunggal ini seringkali lebih banyak membantu mencegah pengembalian lapangan yang dipicu drift daripada memperluas daftar sertifikat.

Cara Menentukan Ruang Lingkup Tanpa Memulai Proyek Ilmiah

Sebuah program yang kredibel tidak mencoba memvalidasi “kebersihan” di mana-mana, selamanya. Ia berfokus pada konsekuensi dan kemungkinan.

Mulailah dari node sensitif dan sekitarnya: pembagi nilai tinggi (100 MΩ ke atas), input elektrometer dengan cincin penjaga, dan jarak HV di mana film permukaan dapat menjembatani creepage. Kemudian tentukan seperti apa dunia produk dalam rentang: dalam ruangan yang aman, paparan kelembapan pantai, atau penyimpanan gudang panas diikuti oleh kelembapan selama pengiriman dan penempatan. Keputusan skoping ini mempengaruhi pemilihan stres pengujian. Itu juga mempengaruhi pengambilan sampel: ekstraksi lokal di sekitar hotspot lebih informatif daripada rata-rata seluruh papan saat entrapment komponen bawah menjadi faktor kegagalan. Jika CM dapat menunjukkan tren resistivitas bilas, log pemeliharaan cuci, dan diagram pemuatan yang mencegah bayangan semprotan, itu mengurangi kebutuhan pengujian eksploratori berulang. Jika tidak, program harus mengasumsikan variabilitas sampai terbukti sebaliknya.

Panduan ini secara sengaja menghindari peringkat merek pembersih, memberikan langkah pembersihan hobi, atau menelusuri sejarah klausul standar demi standar. Materi tersebut tidak membantu tim profesional memutuskan apakah rakitan impedansi tinggi/HV akan tetap stabil di bawah kelembapan dan bias. Itu cenderung mengalihkan perhatian dari tuas yang benar-benar penting: geometri, kemampuan proses, dan validasi yang terkait mekanisme.

Bintang utara praktisnya sederhana: berhenti bertanya apakah papan “bersih” secara abstrak. Tanyakan apakah hotspot tetap isolasi di seluruh kelembapan, bias, waktu, dan kenyataan rework—dan minta pengukuran yang dapat menjawab pertanyaan itu.