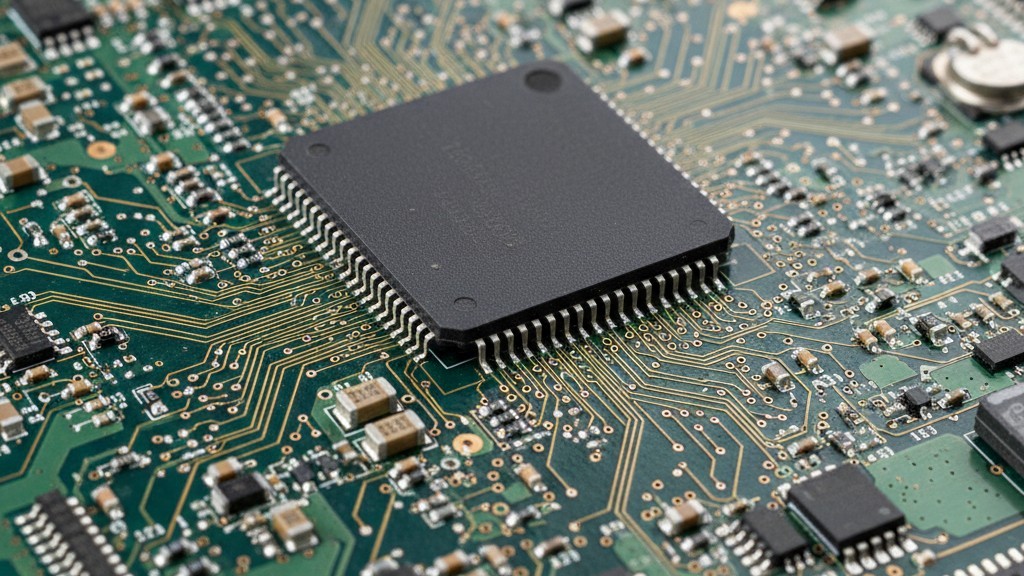

Il silenzio di un prototipo morto è pesante. Non si tratta solo della mancanza di rumore di ventole o dei LED oscuri sull'interfaccia di debug. È il calcolo immediato e opprimente dei costi. Quando una scheda prototipo non si avvia—forse un BGA non si è assestato correttamente durante l'assemblaggio, o un difetto di progettazione richiede una sostituzione—l'attenzione si restringe immediatamente al grande quadrato nero al centro della PCB.

In settori ad alta affidabilità, quel quadrato è spesso un FPGA di fascia alta, come un Xilinx Kintex UltraScale o un Intel Stratix 10. Questi non sono componenti di consumo; sono asset. In tempi di restringimento della catena di fornitura, sostituire quel singolo chip potrebbe richiedere un tempo di consegna di 52 settimane o un markup sul mercato dei broker che supera il budget del progetto. La scheda stessa, un impilaggio di 12 strati con vias cieche e sommerse, potrebbe rappresentare $5.000 in costi di fabbricazione e assemblaggio. La riparazione non è una riparazione standard. È un'operazione di salvataggio in cui l'intera tempistica di sviluppo è in gioco.

Fisica non negozia

Persistente è un'errata idea che rimuovere un Ball Grid Array (BGA) sia semplicemente una questione di applicare calore fino a far fondere la lega saldante. Questo atteggiamento distrugge i prototipi. Pistole termiche portatili, sebbene utili per restringere tubi, sono strumenti di distruzione per le interconnessioni ad alta densità.

La fisica si riduce alla massa termica e al coefficiente di espansione termica (CTE). Un FPGA moderno si trova su una scheda riempita di piani di terra in rame concepiti specificamente per dissipare il calore. Se si colpisce la cima del chip con aria calda senza riscaldare adeguatamente la parte inferiore della scheda, si crea un gradiente termico verticale. La parte superiore si espande mentre quella inferiore rimane fredda e rigida. Il risultato è una deformazione. Mentre la scheda si deforma, tira contro le giunzioni di saldatura. Se la fonte di calore è incontrollata, si rischia di creare

Ecco perché gli ingegneri devono adottare una mentalità di “produzione localizzata”. L'obiettivo è replicare il profilo di riflusso originale — la curva specifica della temperatura nel tempo — che la scheda ha visto nel forno di produzione. L'intera assemblaggio deve essere portata a una temperatura di pre-riscaldamento (di solito intorno ai 150°C o 170°C) per attivare il flusso e equalizzare la temperatura su tutta la PCB. Solo allora dovresti applicare energia localizzata sul componente stesso per spingerlo oltre il punto di liquidus di 217°C. La fisica ignora le scadenze; se la rampata termica è troppo ripida, l'umidità intrappolata all'interno del pacchetto del chip si espande in vapore, causando la delaminazione del pacchetto o il “popcorn”. Un chip esploso è un chip morto.

Il processo: intervento controllato

Ridurlo di un componente $2.000 richiede rigore. Il processo inizia giorni prima dell'intervento vero e proprio con la gestione dell'umidità. A meno che la scheda non sia stata conservata in una scatola asciutta con indicatori di umidità che segnano livelli sicuri, deve essere preriscaldata. I protocolli standard IPC-1601 prescrivono di rimuovere l'umidità dalla PCB e dal componente per prevenire la delaminazione da pressione di vapore. Saltare questo passaggio è la causa più comune di fallimenti invisibili che si manifestano settimane dopo.

Una volta che la scheda è asciutta, passa a un sistema di rework dedicato—tipicamente una macchina con ottiche split-vision, preriscaldatori a infrarossi sul lato inferiore e un ugello di convezione superiore controllato da computer. L'automazione guida questo processo, non il senso manuale. Un termocoppia è spesso attaccato a una scheda sacrificial per mappare precisamente il profilo termico. È necessario sapere che quando la macchina segnala 230°C, le sfere di saldatura sotto il centro di quella griglia di 35x35mm raggiungono effettivamente il reflow, non restano fredde a causa di un dissipatore di calore vicino.

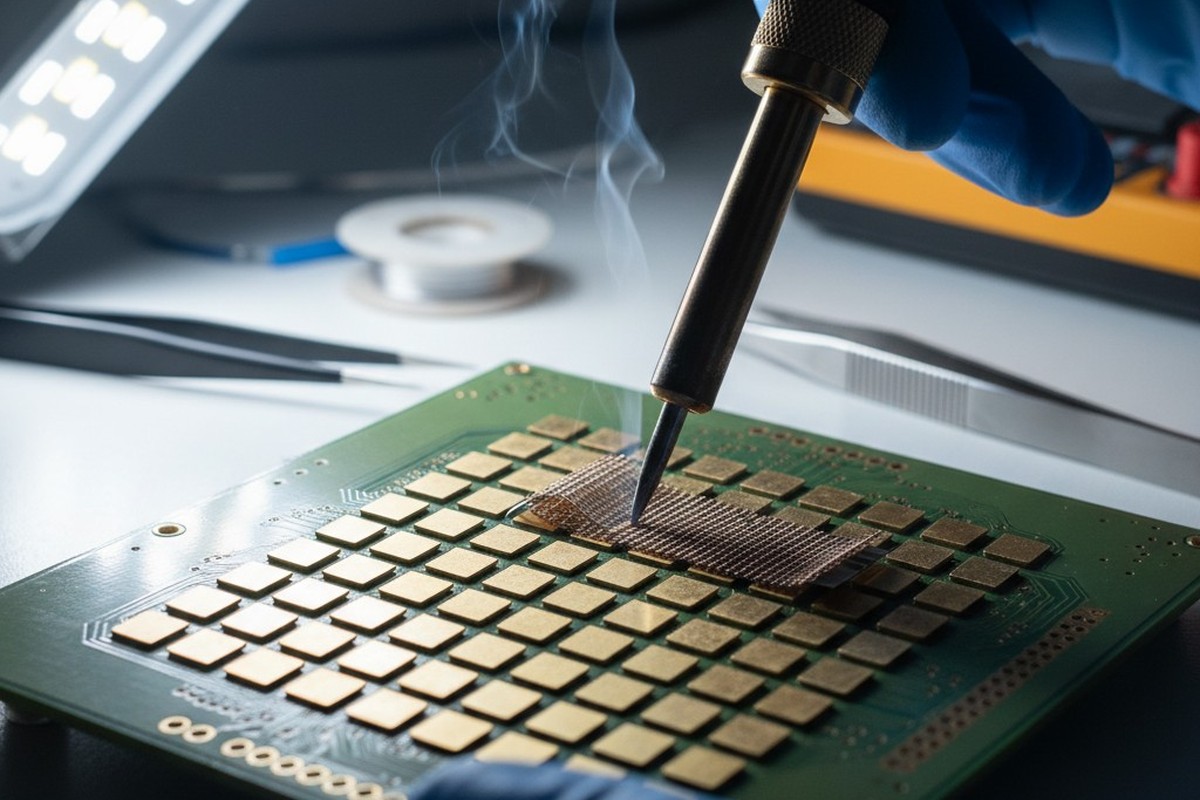

La rimozione stessa è poco spettacolare se il profilo è corretto. Il ugello vuoto scende, la lega si liquefa e il componente si solleva verticalmente senza forza. L'ansia aumenta immediatamente dopo: la preparazione del sito. Ciò comporta la rimozione manuale della vecchia saldatura dai pad PCB usando un ferro da stiro e una trama di bermuda. È qui che le mani dell'operatore sono più importanti. Il ferro deve

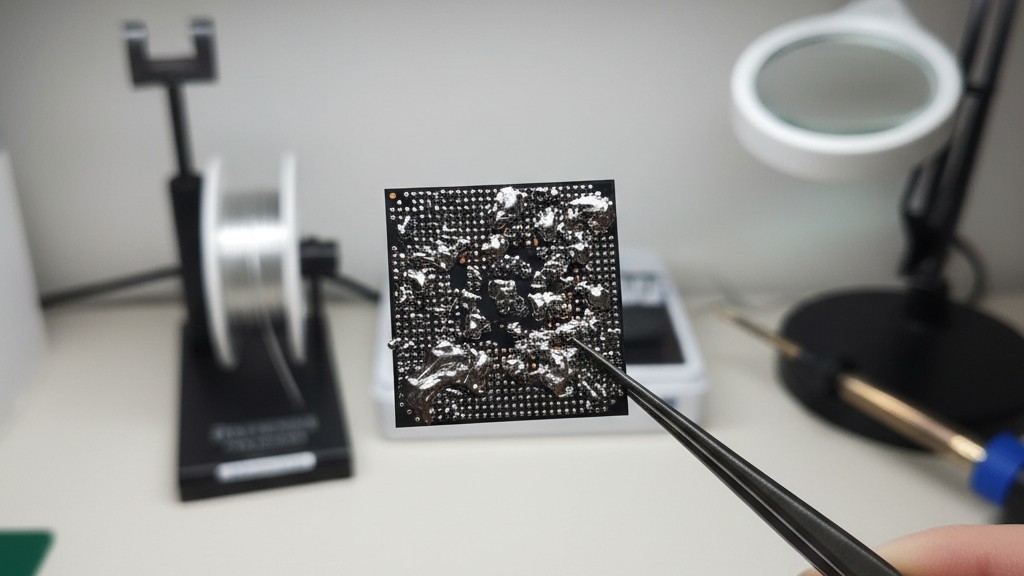

L'equazione del reballing

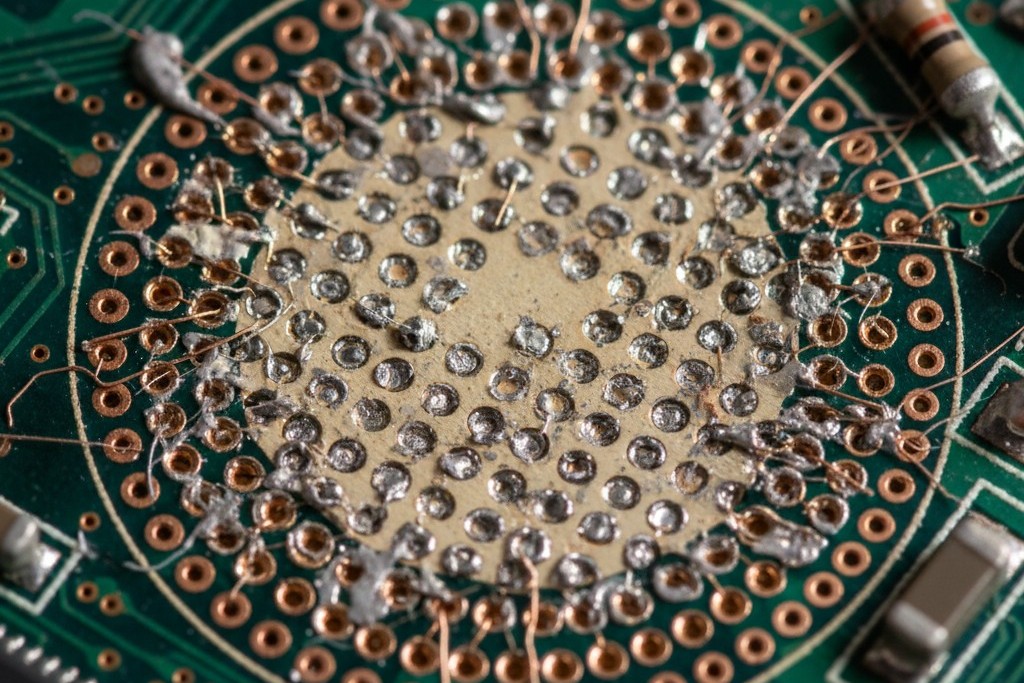

A volte l'obiettivo non è un nuovo chip, ma recuperare quello vecchio da una scheda morta da riutilizzare altrove, o reinstallare un chip che ha avuto un guasto di connessione. Questo introduce la sotto-disciplina del reballing. Un BGA rimosso ha dei pezzi di stagno disordinati e irregolari lasciati sulla sua parte inferiore. Questi devono essere rimossi e nuove sfere di stagno devono essere attaccate.

È un calcolo di ROI puro. Il reballing di un microcontrollore da $5 di merce è una follia finanziaria; le ore di lavoro superano il costo del componente. Ma per un Virtex UltraScale+ del valore di $15.000, il reballing è obbligatorio. Il processo coinvolge un apposito stencil che corrisponde alla impronta del chip, una presenza appiccicosa di flussante e migliaia di sfere di stagno preformate (spesso da 0,4mm o 0,5mm di diametro) versate e allineate manualmente.

L'incertezza è inevitabile, però. Ogni volta che un die di silicio subisce un ciclo di reflow—riscaldamento a 240°C e raffreddamento—si accumula stress termico. La differenza di espansione termica tra il die di silicio, il substrato del package e il PCB esercita una forza sui collegamenti interni. Sebbene un chip possa generalmente sopportare due o tre cicli di reflow (assemblaggio iniziale, rimozione, reballing, posizionamento), il rendimento non è mai garantito. Podemos mitigare il rischio con una profilatura perfetta, ma non possiamo cambiare il limite di fatica dei materiali.

La decisione di rifare di solito dipende dal rapporto 'sostituisci vs. recupera'. Se il silicio è irreplaceabile a causa di carenze, o se la scheda rappresenta settimane di tempo di fabbricazione unico, l'investimento in un profilo termico adeguato e nel tempo di un operatore qualificato è trascurabile rispetto al costo di ricominciare da capo. Le attrezzature—i pre-riscaldatori, i sistemi di visione, le teste di reflow inerti con azoto—esistono per trasformare una catastrofe in un normale ritardo ingegneristico.