縮短產品開發時間的壓力無情,但延遲的後果從未如此嚴重。資金里程碑拖延、市場窗口關閉、競爭對手率先出貨。對硬體團隊而言,從有效原型到試產的過程——一個依賴、批准及製造現實的迷宮——通常需要六十到九十天。速度一直很重要,但對複雜的印刷電路板組裝(PCBA)來說,三十天是一個現實目標,還是設定團隊失敗的理想幻想?

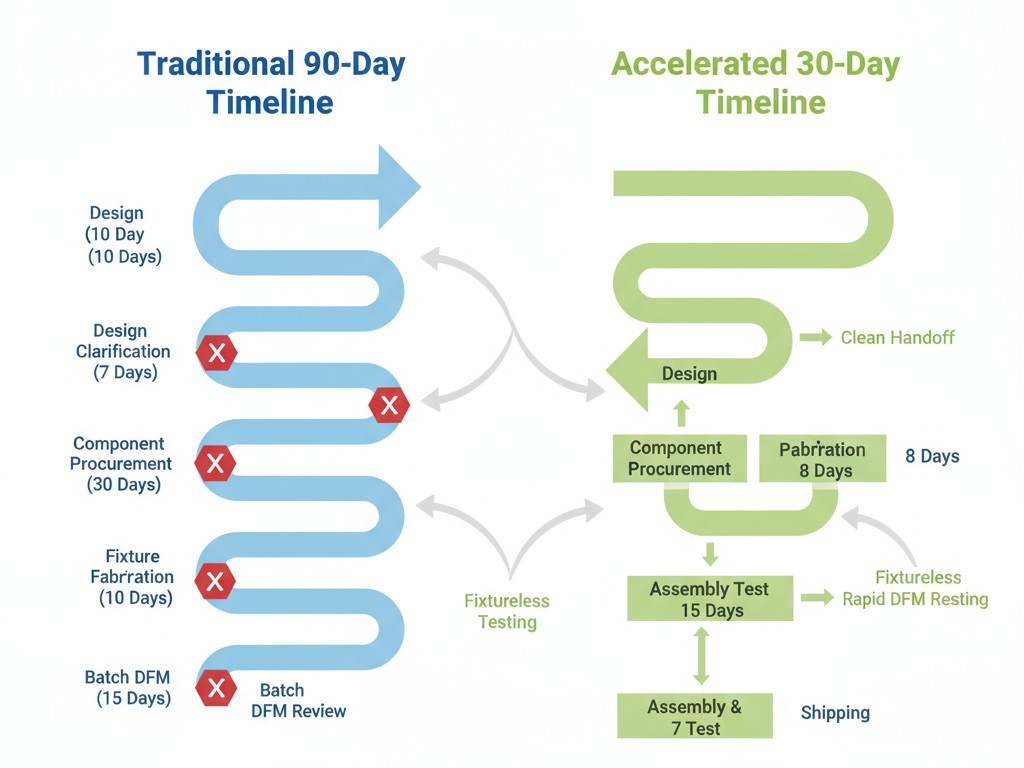

在Bester PCBA,我們知道三十天的上升階段是可行的,但只有在三個特定系統同步優化並精準執行時才行。這不是關於更快的工作或抄近道,而是拆除傳統工作流程中的結構性延遲。三十天循環與九十天循環之間的差別不在於努力,而在於流程的設計。當首次交付的設計清晰、無夾具測試消除了定制工具的瓶頸,以及為製造可行性(DFM)提供的反饋在幾小時內完成而非幾天,整個關鍵路徑就被壓縮。一旦其中任何一項失誤,時間線就會像多米諾般倒塌成行業標準的艱難進行。

這是那個三十天執行操作藍圖的運作框架,它是建立在機械現實之上,而非行銷承諾上。我們將檢視預防模糊的設計交接,消除多周延遲的無夾具測試策略,以及把工程反饋控制在幾小時內的DFM協議。對於構建複雜多層板的團隊來說,這是降低風險、同時保持試驗品等級品質的操作手冊。

為何《三十天》是例外,而非規則

電子製造業從原型批准到試點準備完成PCBA的平均時間在六十到九十天之間。這並不是因為製造商反應遲緩;而是因為流程被設計為一系列連續的門檻,每個都帶來延遲。設計資料不完整會引發澄清循環,甚至在製造開始前就多出五天。用於傳統驗證的定制測試夾具,交付時間為兩至三週。將DFM反饋作為批量處理而非持續對話,可能會浪費一週或更長時間。

這些延遲會累積。一個DFM反饋的兩天延遲會推遲製造開始,進而延遲電路板的交付,造成組裝延遲,進而影響測試。等到試產完成時,三十天的目標已伸長到七十天。問題不在於單一供應商或流程步驟,而在於每個階段依賴上一個階段的小效率累積。在關鍵路徑上,沒有所謂的小延遲。

相較之下,三十天循環是為零餘地而設計的。它要求每一次交接都必須乾淨利落,每個流程都須平行進行,每個決策都須事先預解。這也是為什麼它仍是例外。大多數組織缺乏在第一次就提供完整設計資料的紀律。大多數製造商缺乏在同一天內獲得DFM反饋的工程能力。大多數測試流程仍以需數週交期的夾具為核心。三十天的上升階段不是不可能的,而是標準效率不足的時候,長時間流程所能容忍的

關鍵路徑:定義你的時間線的三個門檻

任何製造過程都受其關鍵路徑的支配——即決定最短完工時間的相依任務序列。此路徑上任何任務的延遲都會使整個專案延長相同的時間。

對於PCBA試點升級,關鍵路徑由三個門控控制: 設計交付精度, 無夾具測試架構,和 DFM 反饋速度. 這些不是獨立變數,而是相互連結的系統。優化這三者,使壓縮的時間表成為可能。準確的交接決定了何時可以開始生產。無夾具測試能確定在不等待工具的情況下驗證電路板的時機。快速的DFM反饋確保在設計風險導致返工或延遲之前解決它們。它們共同構成快速流程的骨幹。

1. 設計交接的精確度

第一關是設計包的完整性。不完整的資料是最大的一個可避免延誤來源。當Gerber檔案缺少層數、物料清單(BOM)缺少製造商料號,或組裝圖紙模糊不清時,流程就會停滯。工程團隊被迫陷入 emailed 問答與澄清通話的循環,每個週期至少耗時一天。在六十天的時間線中,這是個麻煩;在三十天的時間線中,則是致命的。

2. 無夾具測試架構

第二關是驗證組裝完成的電路板的方法。傳統的通路測試夾具是定製的機械組件,能將彈簧探針對準測試點,它們精確,但製作耗時較長,設計、製造與除錯可能長達三週。這是直接在關鍵路徑上的三週串行流程。像飛行探針或邊界掃描的無夾具方法,完全消除了這種依賴,使用可程式化的探針或嵌入的測試邏輯。雖然吞吐量可能較低,但對於十到一百單位的試點規模,所節省的日曆周數幾乎可以忽略不計。

3. DFM 反饋速度

第三關是製造性設計分析的速度。一個徹底的 DFM 檢查能發現風險——如清晰度不足、焊膏碎屑、熱設計不佳——可能會嚴重影響產率或可靠性。當 DFM 反饋在設計交接後數小時內抵達時,可以在生產前做出修正;若需五天,整個時間表便會相應延遲。若反饋需要設計更改,延遲甚至會更長。

雖然元件的交貨時間和電路板的複雜度亦很重要,但這三個閘門是流程設計能最直接控制的因素。Bester PCBA 已專門優化它們,以支持三十天的快速衝刺。

設計交接清單:定義“完整”

“完整的設計包”是一個常用術語,但鮮少精確定義到可以預防歧義的程度。完整包不僅是一套檔案;它是保證製造團隊可以立即進行DFM和生產規劃的保證,無需問一句話。資料不完整總是以可預測的方式顯現:缺少鑽孔檔案、過時的BOM、不匹配的圖紙。每一個問題都會引發查詢,而每個查詢都會帶來延遲。

我們對完整性的定義是零歧義狀態,通過嚴格遵循一個圍繞製造資料、BOM完整性和組裝文件的清單來實現。

Gerber檔案與製造資料

Gerber套件必須包括所有層:銅、阻焊、絲印和膏膠面罩,每個都要正確命名。鑽孔檔必須指定所有孔尺寸和鍍層要求。製造圖紙必須鎖定板的尺寸、層堆疊、材料類型(例如FR-4或高頻層壓板)、銅重量和表面處理。對於具有控制阻抗的板子,堆疊必須定義介電質厚度、目標阻抗值,以及需要控制的特定走線。模糊的製造資料是延遲的最常見原因。當製造商必須猜測時,時間已經在倒數。

物料清單完整性

BOM是所有零件的權威性列表,包括採購和組裝。完整的BOM必須包括參考設計符號、數量、製造商名稱,以及——最重要的——每一行的完整製造商零件號。一個列出“10k電阻 0402”的BOM沒有可行性。而列出“Yageo RC0402FR-0710KL”的BOM,因為它指定了確切、可購買的零件。

不完整的BOM會造成兩種失敗模式:採購延遲和組裝錯誤。通用零件號碼會迫使澄清或冒險替代。BOM與Gerber之間設計符號不匹配,會導致零件位置錯亂和返工。此外,完整性還涉及供貨情況。如果一半零件的交貨期為十二週,BOM就不完整。驗證零件可用性 之前 交接是非 negotiating 的。

三十天的BOM清單包括:

- 所有零件的製造商零件號;不要用通用型。

- 參考設計符號須與Gerber和組裝文件完全一致。

- 所有零件的交貨期驗證。

- 任何獨家供應或高風險零件的替代零件號碼。

- 任何客戶提供零件的清楚標記。

組裝文件和零件放置檔案

組裝文件包括組裝圖、零件放置(或質心)檔案,以及任何特殊指示。組裝圖須為每個元件的定位、方向和極性提供直觀參考,且皆由最終PCB設計產生。放置檔提供自動化用的XY座標。

特殊指示涵蓋非標準工藝:必須在覆膜後組裝的接插件、需要較低回流曲線的耐熱元件,或因濕氣敏感而需要烘烤的IC。這些細節對設計團隊來說似乎理所當然,但對組裝技術人員來說卻是看不見的。完整的文件能消除解讀困難,並保持生產線順暢。

無夾具測試策略:消除瓶頸

測試驗證已組裝的PCBA在進入下一階段前能正常運作。傳統的製造流程依賴自訂測試夾具來提供測試點的物理接入。對於大量生產,投入定制測試夾具的前期成本是合理的,因為它速度快且重複性高;而對於低量試產,測試夾具則成為瓶頸。

為何傳統固定器會打破三十天模型

自訂測試夾具是一種機械組裝,必須先設計、製造並驗證,才能開始測試。這個為期數週的過程涉及分析佈局、創建夾具設計、機加工硬體以及除錯最終組裝。對於複雜的電路板,這個過程很容易需要三週時間。

這是一個序列化的依賴關係。在測試夾具準備好之前,組裝無法進行測試。在六十天的時間表中,三週的夾具交貨時間是可以管理的。在三十天的時間表中,則占用了整個日曆的一半,沒有容錯空間。解決方案是無夾具的測試策略,這允許在板子剛下線的那一刻開始測試。

Flying Probe 和 Boundary Scan 作为替代方案

Flying probe 測試系統使用兩個或更多獨立控制的探針,移動到特定測試點以執行電氣測量。測試序列直接從 CAD 數據編程,因此無需建立物理夾具。設置時間以小時計,而不是以週計。取捨在於吞吐量;測試是順序性的,因此每塊板所需時間更長。對於十到五十個單元的試產,非常有利。一次五分鐘的測試,消除了三週的等待時間,這是個輕鬆的決定。

Boundary scan 另一種無夾具的方法是利用支持 IEEE 1149.1 (JTAG) 標準的集成電路內嵌測試邏輯。它允許測試設備控制和觀察 IC 引腳的狀態,無需物理接觸,這在高密度 BGA 板子上尤其寶貴,因為測試點往往無法接觸。它的限制是僅適用於內建支持的元件。對於具有混合元件類型的板子,邊界掃描經常與 Flying Probe 結合,以實現全面覆蓋。

試點批量的測試覆蓋範圍取捨

無夾具測試並非沒有取捨。與全鋼針測試相比,測試覆蓋率可能較低。對於高產量生產,單一疏漏缺陷造成的成本乘以數千,最大化覆蓋率至關重要。對於試點批量,主要目標是驗證設計功能並捕捉主要組裝缺陷,無夾具方法的覆蓋通常已經足夠。關鍵是要選擇一個在覆蓋率、時間線和成本之間取得平衡的測試策略,而不是出於習慣而採用傳統方法。

DFM回應時間:關鍵的反饋循環

DFM 分析是製造工程師找出可能影響良率、可靠性或成本的問題的方法。每塊板都會進行審查。唯一的問題是它是事先有條理的反饋循環(在製造前)還是反應性的(在生產線上發現問題,導致延誤和報廢)。這個差異通常決定了時間表是三十天還是六十天。

DFM 在製造前抓到什麼

DFM 審查會標記在技術規格範圍內但對工藝變異沒有余地的設計規範,例如與製造商絕對最小值相匹配的走線寬度。該審查會建議一個更安全的尺寸,這不會增加成本,但能顯著提高良率。它會驗證層堆疊是否符合阻抗要求,並檢查可能影響工具或導致回流缺陷(如 tombstoning)的元件擺放。

DFM 的價值不僅在於識別問題;還在於在它們便宜且快速修復時就發現問題。在 DFM 中捕捉到的走線間距違規只需一小時的布局修改。而在製造後發現相同違規則意味著報廢板子並重新開始,延遲兩週。這也是為什麼 DFM 響應時間在關鍵路徑上的原因。

工程能力變數

DFM 響應時間不僅取決於設計的複雜性,還取決於工程能力的可用性。經驗豐富的工程師可以幾小時內審查一塊簡單的板子,但如果工程師積壓,就仍需數天。

在 Bester PCBA,我們安排工程能力,以便為快速通道項目提供當日或次日的 DFM 反饋。這是一個有意的運營策略,需有更大的工程團隊和嚴格的優先排序。這是對速度的投資,也是緊湊時間表的關鍵推動力。

如何迅速根據DFM反饋採取行動

設計團隊對 DFM 反饋的反應速度決定了電路板何時進入生產階段。最有效的方法是將 DFM 視為一個同步的過程。當設計交接時,團隊應準備好進行快速迭代。對於關鍵電路板,我們建議進行一次現場審查會議,製造和設計工程師可以即時解決問題。

迭代是三十天時間表的敵人。每一次循環都會增加天數。最有效的方法是從一開始就提供一個乾淨、可製造的設計,這就回到了交接清單。乾淨的設計能導致最低限度的DFM反饋,循環也能快速閉合。

電路板複雜度與可行性界限

三十天的時間表對於多種電路板都是可行的,但並非所有都如此。複雜度是決定可行性的主要變數。一個簡單的雙層電路板可以在幾天內完成。一個具有盲孔和埋孔、阻抗控制對、0.4mm pitch BGA的十二層堅硬柔性電路板則需要更長的製造週期和更密集的裝配,從而拉長了時間。

- 層數 是最直觀的驅動因素。四層板的製造大約需要三到五天;帶有盲孔的十二層板可能需要十到十二天。對於超過八層的電路板,三十天的時間窗口會大幅收緊。

- 元件密度 以及封裝類型也會影響可行性。一個使用01005被動元件和0.4mm pitch BGA的電路板在回流焊時需要更嚴格的工藝控制,並增加缺陷風險,這些缺陷可能需要返工。

- 阻抗控制 增加了製造複雜性和DFM風險。它需要精確的材料厚度和驗證,如果阻抗不符合規範,必須報廢並重新製造電路板。

目標不是為了阻礙複雜設計,而是設定現實的預期。一個具有標準元件的六層電路板,三十天的預估是保守的;而一個具有密集BGA和嚴格阻抗公差的十層電路板,則是可以實現的,但需要完美執行,且零誤差空間。

執行三十天上升階段:一個一體化框架

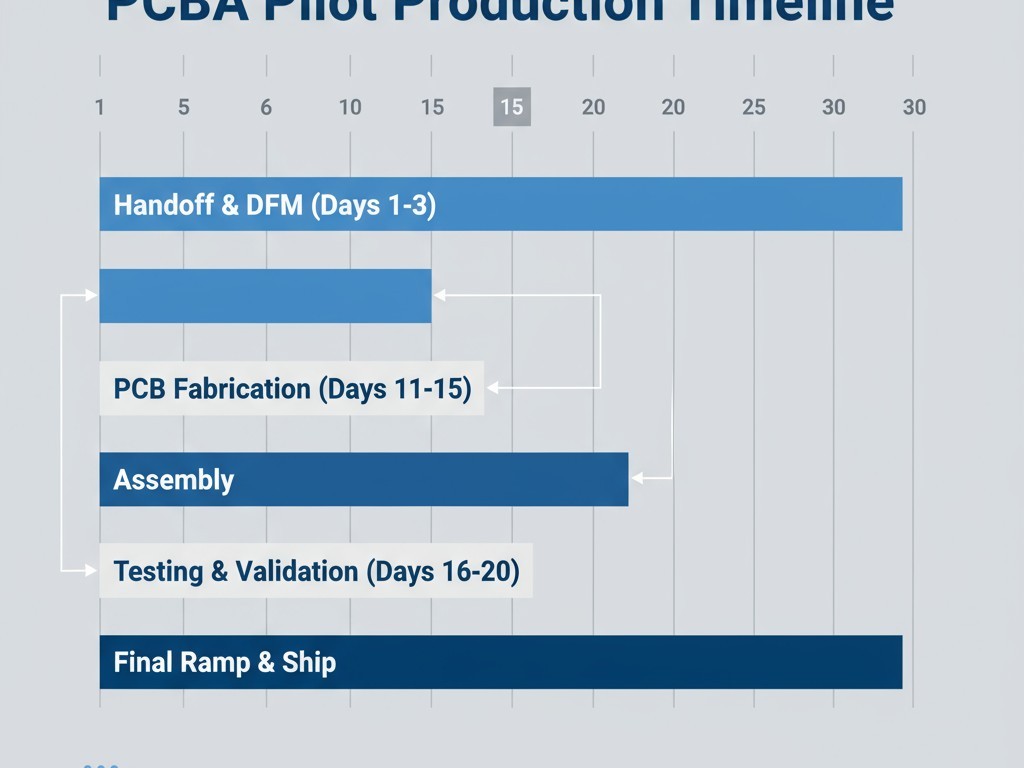

三十天的時間表是密切協調的流程。這個框架概述了一個現實的逐日進展,適用於具有二十到五十台單位的六到八層複雜電路板。

第1–3天:交接與DFM 第一天,完整的設計資料包到達。立即開始DFM審查。到第二天結束時,提供反饋。在第三天,設計團隊提交更正檔案,電路板獲准進行製造。這一階段是交接清單發揮作用的地方;如果資料包不完整,這一階段可能延長到一週,嚴重破壞時間表。

第4–10天:PCB製造 第四天開始製造。對於六層板,包括成像、層壓、鑽孔、電鍍和後處理。這一段時間是最難壓縮的,因為受到物理流程的限制。空白電路板在第十天運送到組裝廠。

第11–15天:組裝 元件配套和模板製作在第十一天進行。在接下來的兩天內完成焊膏印刷、貼片和回流,之後進行任何手動組裝。檢查在第十五天完成。這裡最大的風險是元件的可用性,這也是為什麼交接時的提前期驗證是不可談判的。

第16到20天:測試與驗證 無治具測試在第十六天開始,一旦電路板可用。接下來的幾天內會識別並返工組裝缺陷。由於不需要定制治具,這一階段在組裝完成後立即開始。採用傳統治具的情況下,測試要等到第二十五天或更晚。

第21到30天:試點提升與最終驗證 到第21天,已測試出初始電路板,並完善了組裝流程。剩餘的試點單元建造、測試和驗證。最終檢查、包裝及出貨在第30天完成。產品團隊現擁有具功能的試點單元,較傳統流程節省了三週時間。

關鍵依賴已經清楚。DFM必須在第3天完成。製造需在第10天前結束。無治具測試必須在第16天開始。每個門都促進下一步。當這三個系統皆優化完成,30天的時間表不再是一個目標,而是經過精心設計流程的自然結果。