Ciśnienie, aby wykryć usterki produkcyjne zanim płytki trafią do klienta, jest nie do negocjacji. Pojedyncza niezaobserwowana wada w krytycznym systemie może kosztować znacznie więcej niż testy, które by ją wykryły. Ta rzeczywistość kieruje wiele zespołów inżynieryjnych ku testom w obwodzie (ICT) jako domyślnemu rozwiązaniu, długo uważanemu za złoty standard pokrycia. Pełne ICT zapewnia kompleksowy dostęp do niemal każdego węzła na płycie, obiecując wskaźniki wykrywania usterek zbliżone do teoretycznego maximum. Dla produkcji na dużą skalę, inwestycja ma sens; stałe koszty inżynierii jigsów i sprzętu testowego rozkładają się na tysiące jednostek, obniżając koszt jednostkowy do znikomego poziomu.

Ale ekonomiczne uwarunkowania odwracają się, gdy volume produkcji spada. Przy partiiach poniżej kilkuset sztuk, właśnie mocne strony ICT stają się wadami. Niestandardowy jig wymagany dla każdego projektu płyty generuje wysokie, stałe koszty inżynieryjne, które nie skalują się. Czas realizacji wydłuża się, gdy jigs są projektowane, budowane i debugowane. Iteracje projektu, powszechne we wprowadzaniu nowych produktów, całkowicie unieważniają jig, wymuszając rozpoczęcie procesu od nowa. W firmie PCBA oglądaliśmy, jak te kalkulacje sprawdzają się na setkach projektów. Przy partiiach poniżej 200-300 sztuk, pełne ICT rzadko kiedy się opłaca.

Alternatywą nie jest porzucenie rygorystycznych testów, lecz zastąpienie modelu opartego na jigach bardziej lean, szybszą strategią opartą na boundary scan, testowaniu bez wektorów i skoncentrowanych testach funkcjonalnych. Ta kombinacja zapewnia porównywalny zakres wykrywania usterek, eliminuje wąskie gardło związane z jigami oraz zapewnia szybszą pętlę debugowania, gdy wykryte zostaną usterki. Ta zmiana nie jest ideologiczna; jest praktyczną reakcją na matematyczne i mechaniczne tarcia, które ICT narzuca na produkcję niskonakładową i zwinność.

Przyjęcie ICT i miejsce, w którym się łamie

Testy w obwodzie stały się standardem branżowym w erze produkcji na dużą skalę i stabilnych projektów. Model był prosty: inwestuj dużo z góry w niestandardowy jig i zaawansowany tester, a następnie korzystaj z tej inwestycji na dziesiątki tysięcy identycznych jednostek. Przy czasie testu jednostkowym wyrażonym w sekundach, koszt marginalny na płytę był praktycznie zerowy po pokryciu kosztów stałych. Dla producenta elektroniki konsumenckiej produkującego 50 000 sztuk tego samego modelu, matematyka była niepodważalna.

Ten model produkcji się rozbił. Nowoczesne wytwarzanie elektroniki coraz częściej obsługuje rynki o wysokim miksie i niskim volume. Cykle życia produktów są krótsze, iteracje projektowe częstsze, a personalizacja stanowi przewagę konkurencyjną. Firma może wyprodukować 150 sztuk jednej wersji, zmodyfikować projekt, potem wyprodukować 200 sztuk kolejnej. Założenie, że pojedynczy jig wytestuje tysiące identycznych płytek, nie jest już aktualne. Stałe koszty, które w wysokich ilościach były pomijalne, stają się uciążliwe, gdy rozkładają się na kilka setek sztuk.

Model łamie się tam, gdzie całkowity koszt infrastruktury ICT przewyższa koszt strat związanych z alternatywnymi strategiami, odpowiednio wyważonymi do ryzyka. Próg ten nie jest arbitralny. Jest funkcją kosztu jigów, czasu inżynieryjnego, czasu realizacji produkcji i pokrycia dostępnego przez metody bez jiga. Dla większości projektów płytek, ten próg mieści się pomiędzy 200 a 300 jednostek.

Pułapka stałych kosztów testowania w obwodzie

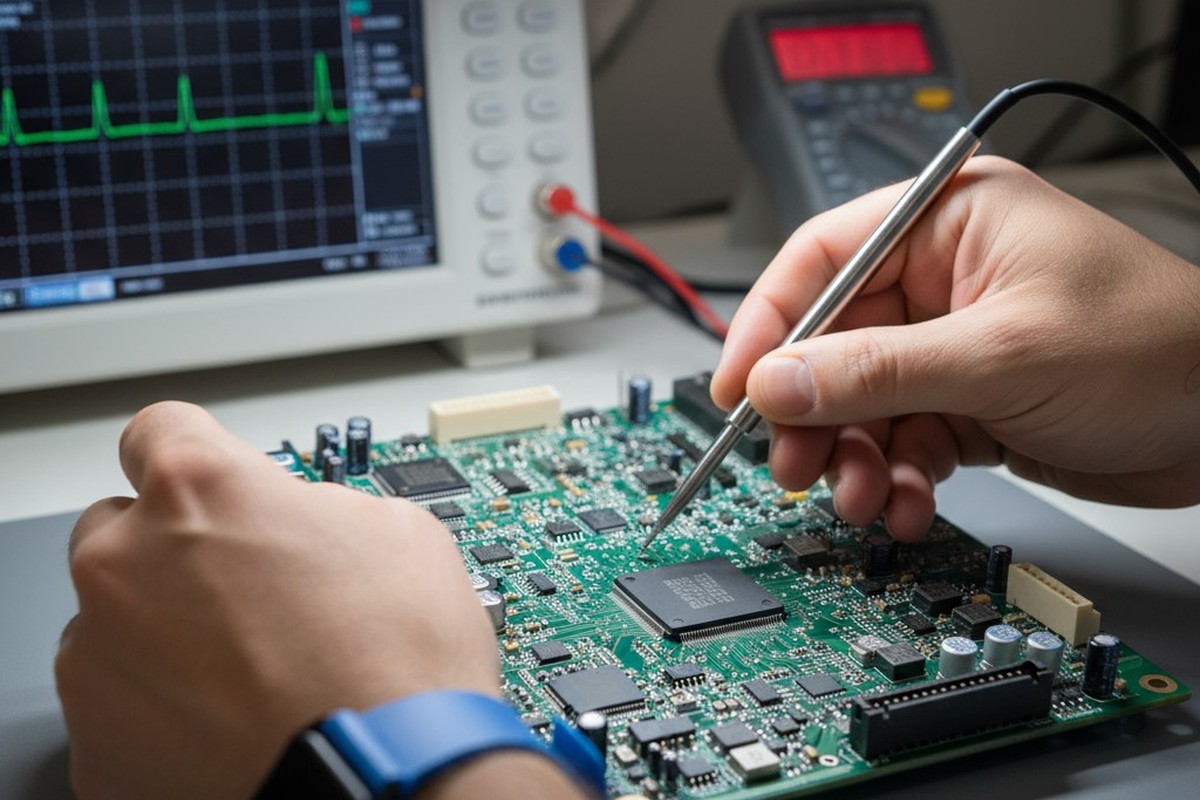

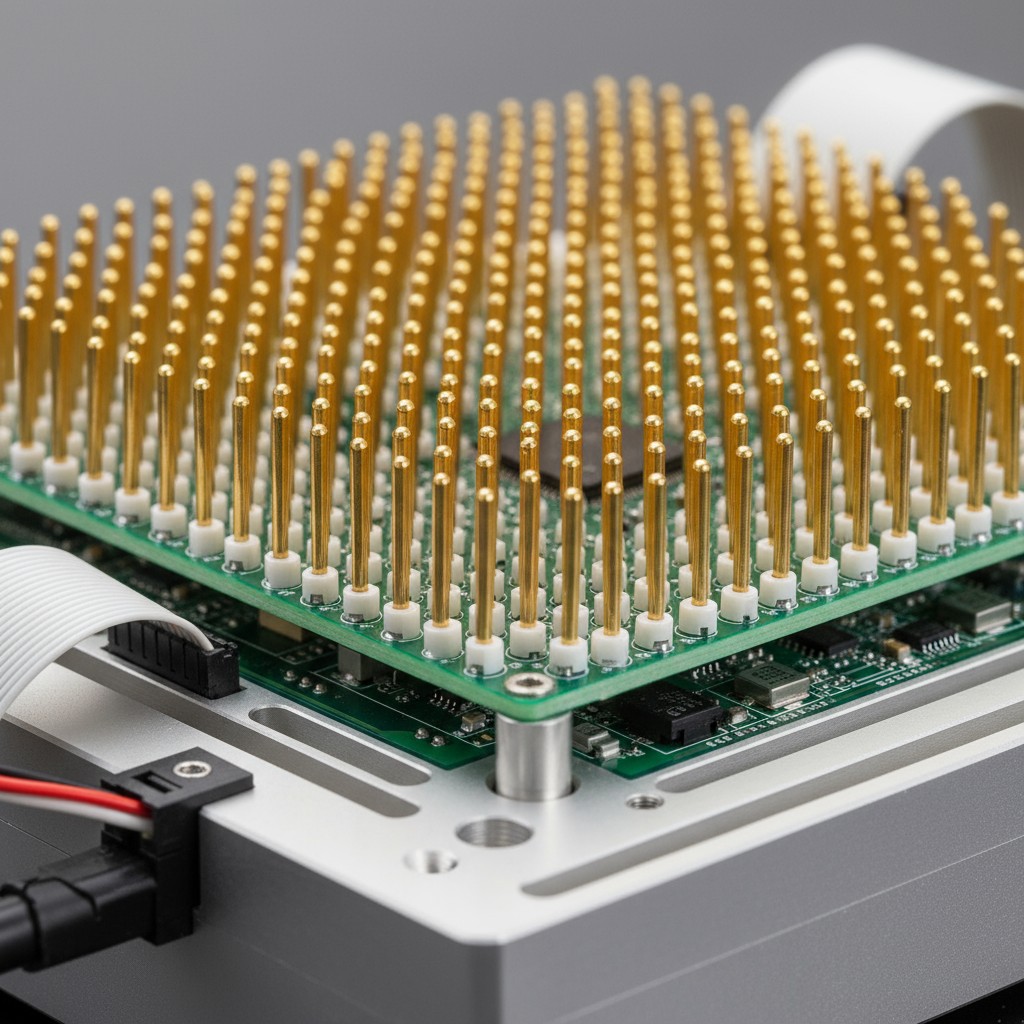

Podczas gdy jig jest najbardziej widocznym kosztem ICT, prawdziwy ciężar ekonomiczny jest znacznie szerszy. Niestandardowy jig ICT nie jest zakupem gotowym od razu; jest to wyprodukowany na zamówienie, specjalistyczny artefakt, stworzony pod konkretne rozmieszczenie płytek. Proces projektowania wymaga przekształcenia listy połączeń płytek i rozmieszczenia komponentów w strukturę mechaniczną z sprężynującymi sondami testowymi, każdą wyrównaną do konkretnego punktu testowego z precyzją poniżej milimetra. Jig musi uwzględniać tolerancje komponentów, odkształcenia płytki i zużycie sond. Następnie musi zostać zwalidowany i zdebugowany — proces ten często ujawnia nieprzewidziane problemy z dostępem sond lub integralnością sygnału.

Koszty inżynieryjne i czas realizacji jigsów

Koszt inżynieryjny dla przeciętnie skomplikowanego uchwytu zazwyczaj wynosi od $8 000 do $15 000. Wysoko-gęste płyty z elementami o drobnej rozstawie lub ograniczonym dostępie do punktów testowych mogą podnieść tę kwotę do $25 000 lub więcej. Jest to czysto koszt niestandardowego interfejsu mechanicznego i elektrycznego potrzebnego do podłączenia płyty do sprzętu ICT, oddzielnie od kosztów kapitałowych samego testera.

Czas realizacji jest równie istotny. Od momentu zatwierdzenia projektu płytki, projekt i wykonanie uchwytu zwykle zajmują od dwóch do czterech tygodni, a w przypadku skomplikowanych projektów nawet do sześciu. W tym okresie produkcja jest wstrzymywana. Płyty mogą być zmontowane, ale nie mogą być testowane. Leżakują w magazynie, czekając. Jeśli projekt ulegnie zmianie w tym okresie—co jest powszechne przy wprowadzaniu nowego produktu—uchwyt musi zostać zmodyfikowany lub wyrzucony. Czas się resetuje.

Matematyka opłacalności dla niskonakładowych serii

Pułapka ekonomiczna staje się jasna, gdy koszty uchwytu są dzielone przez liczbę jednostek. Uchwyt za $12 000 na serię 100 sztuk dodaje obciążenie $120 do każdej płyty. Dla płyty z kosztem materiałów wynoszącym $500, oznacza to 24 procent nadwyżki testowania. Nawet jeśli proces ICT jest szybki, wydajność ekonomiczna jest niska. Ten sam uchwyt amortyzowany na 500 jednostek obniża koszt jednostkowy do $24, co jest znacznie bardziej akceptowalnym pięcioprocentowym kosztem nadwyżki. Różnica wynika wyłącznie z wielkości produkcji.

Punkt rentowności to miejsce, w którym łączny koszt ICT—w tym inżynierii, ustawień i kosztu alternatywnego czasu realizacji—jest równy kosztowi alternatywy bez uchwytu. Dla strategii łączącej boundary scan, testowanie bez wektorów oraz lean funkcjonalny test, koszty infrastruktury są znacznie niższe. Boundary scan nie wymaga uchwytu, a testowanie bez wektorów korzysta z wielokrotnego użytku sensorów, które działają bez kontaktu mechanicznego. Każdy uchwyt funkcjonalny jest zwykle minimalny i uniwersalny, nie jest specyficznym artefaktem dla płytki, wymagającym tygodni inżynierii.

Przy wolumenach produkcyjnych poniżej 200 sztuk ekonomia ICT upada. Poniżej 300 sztuk, sytuacja jest marginalna, zależna od skomplikowania płytki. Dopiero powyżej 300 sztuk dla stabilnych, nieskończonych projektów ICT zaczyna znów mieć wyraźny sens ekonomiczny.

Czym naprawdę są Boundary Scan i testowanie bez wektorów

Alternatywą dla testowania opartego na fixture jest niekompromisowa rigor, lecz przejście na metody wykorzystujące istniejącą infrastrukturę projektową oraz pomiary bezkontaktowe. Narzędzia te zostały opracowane, aby sprostać temu samemu trendowi, który podważa ICT: rosnącej gęstości układów i zmniejszającemu się dostępowi do fizycznych punktów testowych.

Boundary scan, sformalizowany w standardzie IEEE 1149.1 (znanym jako JTAG), wprowadza logikę testową bezpośrednio do układów scalonych na płytce. Kompatybilne układy zawierają łańcuch komórek przy każdym wejściu i wyjściu. Podczas testu, prosty interfejs czteroprzewodowy przesuwa wzorce do tych komórek, kontrolując stany logiczne na sieciach płytki. Wynikowe stany są przechwytywane i przesuwane na zewnątrz do analizy, pozwalając testerowi na kontrolowanie i obserwowanie sygnałów na poziomie pinów bez kontaktu fizycznego. Ta nieinwazyjna metoda jest wyjątkowo skuteczna w wykrywaniu zwarć, otwarć i usterek typu stuck-at pomiędzy zgodnymi urządzeniami.

Testowanie bez wektorów uzupełnia to, korzystając z pomiarów pojemnościowych i indukcyjnych do wykrywania usterek na całej płytce. Sonda umieszczona w pobliżu płytki mierzy jej sygnał elektromagnetyczny zmontowanych elementów i ścieżek. Zwarcia generują wyczuwalne sprzężenia pojemnościowe; otwarcia wykazują charakterystyczne zmiany impedancji. Metoda jest szybka, bezkontaktowa i może wnioskować o obecności komponentów, polaryzacji i przybliżonej wartości, co czyni ją skuteczną w wykrywaniu poważnych defektów produkcyjnych, takich jak brakujące elementy, odwrócone diody czy mostki na ścieżkach.

Porównanie pokrycia: liczby stojące za kompromisem

Podstawową sprzeciw wobec porzucenia ICT jest zakres pokrycia. Chociaż ICT z założenia może uzyskać dostęp do każdego węzła na płytce z wystarczającą ilością punktów testowych, twierdzenie, że alternatywy są gorsze, jest niepełne. Prawdziwe pytanie brzmi, czy osiągają wystarczający zakres, by wykryć rzeczywiste usterki, które się pojawiają, oraz czy skoncentrowany test funkcjonalny może zamknąć pozostałą lukę.

Co obejmuje Boundary Scan

Pokrycie skanowania granicznego zależy od tego, ile elementów na płytce jest zgodnych ze standardem JTAG. Dla płyt zdominowanych przez logikę cyfrową — mikroprocesory, FPGA, pamięć — pokrycie jest szerokie. Łańcuch skanowania może testować połączenia między tymi urządzeniami z wskaźnikami wykrywania błędów przekraczającymi 95 procent dla zwarć, otwarć i błędów typu

Co dodaje testowanie bezwektorowe

Testowanie bezwektorowe wypełnia luki pozostawione przez skanowanie graniczne, zwłaszcza dla komponentów pasywnych i poważnych defektów montażu. Pomiary pojemnościowe mogą wykryć brakujące rezystory, nieprawidłowe wartości kondensatorów i odwrócone diody. Chociaż jest mniej precyzyjne niż bezpośrednie pomiary ICT, jest skuteczną metodą wykrywania najczęstszych błędów: niewłaściwego elementu, brakującego elementu lub poważnego nieprawidłowego ułożenia. Dodaje to kolejne 10 do 20 procent do całkowitego zakresu wykrywania usterek, zapewniając warstwę weryfikacji bezkontaktowej dla części, których skanowanie graniczne nie jest w stanie zobaczyć.

Pozostała luka i jak Lean Functional Test ją zamyka

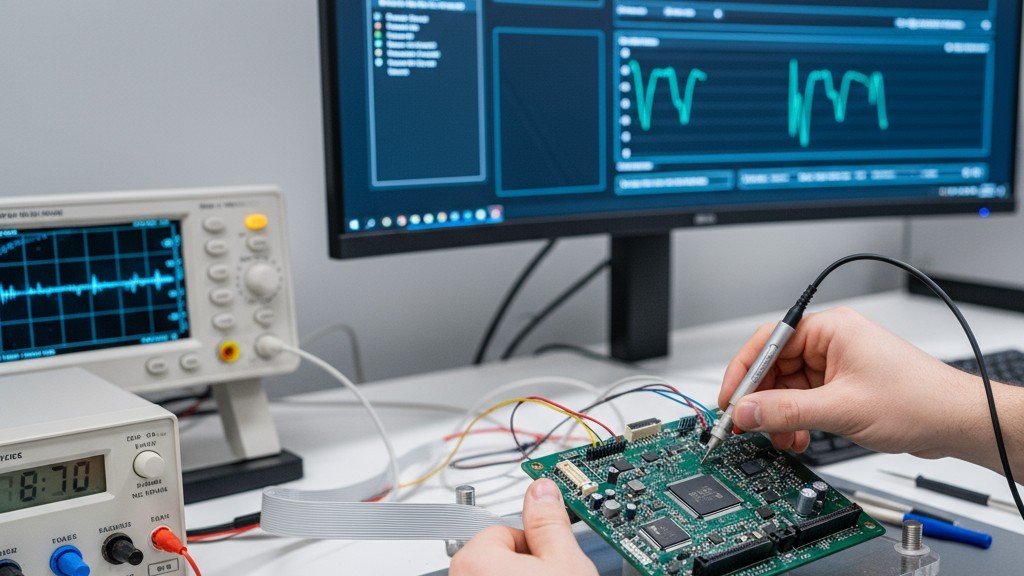

Połączenie boundary scan i testowania bez wektorów wciąż pozostawia lukę w walidacji funkcjonalnej i wydajności analogowej. Element może być obecny i podłączony poprawnie, ale wciąż może nie działać zgodnie z specyfikacją. Zasilacz może dostarczać napięcie, ale z nadmiernym ripples. Tak działa lean funkcjonalny test obwodu (FCT). W odróżnieniu od pełnego zestawu ICT, lean FCT weryfikuje, czy płytka wykonuje zamierzoną funkcję w realistycznych warunkach. Zastosowuje zasilanie, pobudza wejścia i mierzy wyjścia. Dla sterownika silnika może to oznaczać weryfikację generacji sygnału PWM; dla płytki komunikacyjnej – sprawdzenie bezbłędnej transmisji danych. Test funkcjonalny uzupełnia testy strukturalne, wykrywając usterki, których inne metody nie widzą.

Połączenie tych trzech metod zwykle osiąga od 85 do 95 procent pokrycia usterek. To nie jest 100 procent, ale również ICT w praktyce nie jest. Ze względu na ograniczenia punktów testowych i zużycie sond, rzeczywiste pokrycie ICT często nie osiąga swojego teoretycznego maksimum. Różnica w pokryciu jest znacznie mniejsza od kary w kosztach i czasie realizacji.

Zaleta pętli debugowania

Pokrycie testów to tylko połowa wartości; druga to szybkość i precyzja izolacji usterki. Test, który wykryje usterkę, ale dostarcza mglistych diagnoz, wydłuża czas i zwiększa koszty poszukiwania przyczyny źródłowej.

Podczas gdy ICT świetnie sygnalizuje usterki, jego diagnostyka może być irytująco niejasna. Tester może zgłosić, że węzeł 47 jest zwarcie do masy, ale nie wyjaśnia dlaczego lub gdzie. Technik musi prześledzić schemat, zlokalizować sieć i wizualnie sprawdzić obszar—proces, który może zająć godziny na gęstej, wielowarstwowej płytce.

Diagnostyka skanowania granicznego jest zasadniczo inna. Ponieważ łańcuch skanu jest osadzony w komponentach, test izoluje usterki do konkretnych pinów i urządzeń. Zwarcie między dwoma sieciami jest identyfikowane na podstawie dokładnych pinów urządzenia, zawężając zakres poszukiwań do kilku milimetrów kwadratowych. Otwarcia są wykrywane między określonymi parami sterowników i odbiorników. Wynik diagnostyczny to nie kod błędu. To mapowanie. Ta precyzja oznacza, że usterka, którą można naprawić w ciągu godziny za pomocą danych ICT, często może zostać rozwiązana w 10 do 20 minut dzięki skanowaniu granicznemu. Dla produkcji 100 jednostek z typowym wskaźnikiem defektów, łączny czas oszczędności na debugowaniu może przekroczyć 10 godzin.

Czas realizacji i elastyczność: ukryta wartość

Ekonomiczny argument przeciwko ICT przy niskich nakładach jest przekonujący, ale kara za czas realizacji jest równie znacząca. Proces inżynieryjny przy użyciu urządzenia od dwóch do czterech tygodni narzuca obowiązkowe opóźnienie między zamrożeniem projektu a gotowością do testowania. Dla wprowadzenia nowego produktu, gdzie czas wprowadzenia na rynek jest krytyczny, to opóźnienie często jest nie do przyjęcia.

Skanowanie graniczne i testowanie bez wektorów eliminują to oczekiwanie. Konfiguracja testu może być ustawiona w godzinach lub dniach, a nie tygodniach, umożliwiając przejście płytek od montażu do testu do wysyłki w ciągłym przepływie. Ta elastyczność jest kluczowa przy iteracyjnym procesie projektowania. Wczesne uruchomienie prototypu może ujawnić problemy wymagające zmian w układzie płytki. Przy ICT każda rewizja wymaga nowego lub przerobionego urządzenia, co wiąże się z kosztami i czasem realizacji od nowa. Wzorce testowe skanowania granicznego generowane z netlisty aktualizują się automatycznie wraz z projektem. Tworzy to strategię testową wspierającą iteracyjny rozwój, a nie karzącą za niego.

Kiedy nadal wybierać ICT

Ale argument przeciwko niskonakładowym ICT nie jest absolutny. Niektóre projekty i konteksty produkcyjne nadal uzasadniają inwestycję.

Płyty z wysokiej gęstości analogowymi lub RF sekcjami są złymi kandydatami do strategii opartej wyłącznie na urządzeniu. Komponenty analogowe nie mają logiki skanowania granicznego, a kluczowe parametry wydajności, takie jak wzmocnienie czy szum fazowy, nie mogą być weryfikowane strukturalnie. Jeśli obwody analogowe lub RF stanowią ponad 40 procent funkcjonalności płyty, argument za ICT znacznie się wzmacnia.

Przemysły podlegające przepisom, takie jak medyczny, kosmiczny i motoryzacyjny, często funkcjonują w ramach regulacji nakładających określoną ochronę testową lub metody. Jeśli obowiązujący standard wymaga testowania w układzie lub równoważnego dostępu na poziomie węzłów, alternatywne strategie mogą nie wystarczyć. W tym przypadku koszt ICT jest nieodłącznym kosztem wejścia na rynek.

Ostatecznie, jasna i zaangażowana droga do produkcji wysokiego wolumenu zmienia rachubę. Jeśli początkowa seria 150 jednostek ma się rozwinąć do 1000 jednostek w ciągu sześciu miesięcy, koszt urządzenia rozkłada się na całkowity przewidywany wolumen. To wymaga dużej pewności co do prognozy i stabilnego projektu, ale może sprawić, że początkowa inwestycja będzie opłacalna.

Budowa alternatywnej strategii testowania

Zastąpienie ICT nie jest prostą zamianą; to rekonfiguracja architektury testu w warstwową strategię, w której każda warstwa wychwytuje usterki, które mogłyby przegapić inne.

Proces powinien być sekwencyjny. Pierwsza warstwa to skanowanie graniczne, które szybko działa na wszystkich zgodnych urządzeniach, aby wychwycić usterki połączeń na cyfrowych częściach płyty. Płyty, które zawiodą, są oznaczane do natychmiastowego przerobienia, co zapobiega katastrofalnym awariom podczas późniejszego zasilania. Druga warstwa to testowanie bez wektorów, które działa na całej płycie, aby wykryć brakujące lub nieprawidłowe elementy pasywne, zwarcia grube i błędy polaryzacji. Pokrywa komponenty i sieci niewidoczne dla łańcucha skanowania.

Trzecia i ostatnia warstwa to skoncentrowany test funkcjonalny. Po odfiltrowaniu usterek strukturalnych płyta jest zasilana, aby zweryfikować krytyczne funkcje w realistycznych warunkach operacyjnych. Zakres jest dostosowany do celu płyty — weryfikacji dokładności ADC na płycie do akwizycji danych lub regulacji obciążenia na zasilaczu. Ta sekwencja zapewnia, że katastrofalne usterki są wykrywane wcześnie i bez uszkodzeń, minimalizując czas debugowania trudnych awarii funkcjonalnych.

Dla płyt z hybrydową złożonością — na przykład gęstym rdzeniem cyfrowym otoczonym analogowym uszeregowaniem sygnałów — może być najbardziej odpowiednia strategia hybrydowa. Częściowy układ ICT można zaprojektować do sondowania tylko krytycznego odcinka analogowego, pozostawiając cyfrową część do skanowania granicznego. Ekonomia częściowego urządzenia jest bardziej korzystna, obniżając koszty i czas realizacji, jednocześnie zapewniając konieczne pokrycie całego projektu.