Die Kosten einer Leiterplatten-Neuproduktion gehen weit über verschrottete Platinen und verzögerte Zeitpläne hinaus. Für Produkte, die Quad Flat No-Lead (QFN)- und Micro-Ball-Grid-Array (BGA)-Pakete mischen, ist der Cliff der Ersteinsatz-Ertragsschwelle steiler, als die meisten Designteams vermuten. Diese beiden Paketfamilien stellen widersprüchliche Anforderungen an nahezu jeden Aspekt der Herstellung, vom Paste-Druck und Bauteilplatzierung bis hin zur Nach-Reflow-Inspektion. Eine Schablonenöffnung, optimiert für das große thermische Pad eines QFN, wird die feinen Kugeln eines Micro-BGA in Lötzinn ertränken. Ein Board-Rail, der für die Standardmontage ausreichend ist, fehlt möglicherweise die Steifigkeit, wenn ein schweres Schablonenmuster beide Pakete abdeckt.

Dieser Konflikt ist in den Paketen selbst verwurzelt. QFNs erfordern hohe Pastemengen für ein einzelnes großes thermisches Pad—oft 5 mm oder mehr pro Seite—und gleichzeitig präzise Absetzungen auf Perimeter-Pads mit Teilungsmaßen von 0,4 mm. Micro-BGAs verteilen dagegen Hunderte von Löt-Kugeln auf eine kleine Fläche mit Pitches von 0,5 mm oder feiner, bei denen selbst kleine Registrierungsfehler Öffnungen oder Brücken verursachen. Wenn beide auf einer gemeinsamen Schablone und einem Platzierungslauf verwendet werden, muss das Layout diese Bedürfnisse durch bewusste, manchmal kontraintuitive, DFM-Maßnahmen ausgleichen. Die meisten vermeidbaren Fehler bei der ersten Produktion lassen sich auf fünf spezifische Entscheidungspunkte zurückführen: Paste-Ø-Anpassung, Via-in-Pad-Ausführung, Unterfüll-Restriktionsplanung, Board-Rail-Dimensionierung und Fiducial-Verortung.

Warum gemischte Layouts den ersten Produktions-Yield-Absturz verursachen

Der offenliegende thermische Kontaktpad des QFN ist eine berüchtigte Montageherausforderung. Dieser Pad kann 40 bis 60 Prozent der Gehäuse footprint ausmachen und erfordert eine robuste Lötverbindung für thermische und elektrische Leistung. Das bedeutet, dass eine ausreichende Lötmenge entscheidend ist, doch die Paste muss ohne Einschluss von Lufteinschlüssen oder das Aufschwimmen des Gehäuses wieder fließen. Um diesen Pad herum fordern fein-pitch Perimeterkontakte präzise Pastenablagerungen mit minimalem Risiko des Durchhängens oder Überbrückens. Das Gehäuse ist im Wesentlichen zwei unterschiedliche Montageprobleme in einer footprint.

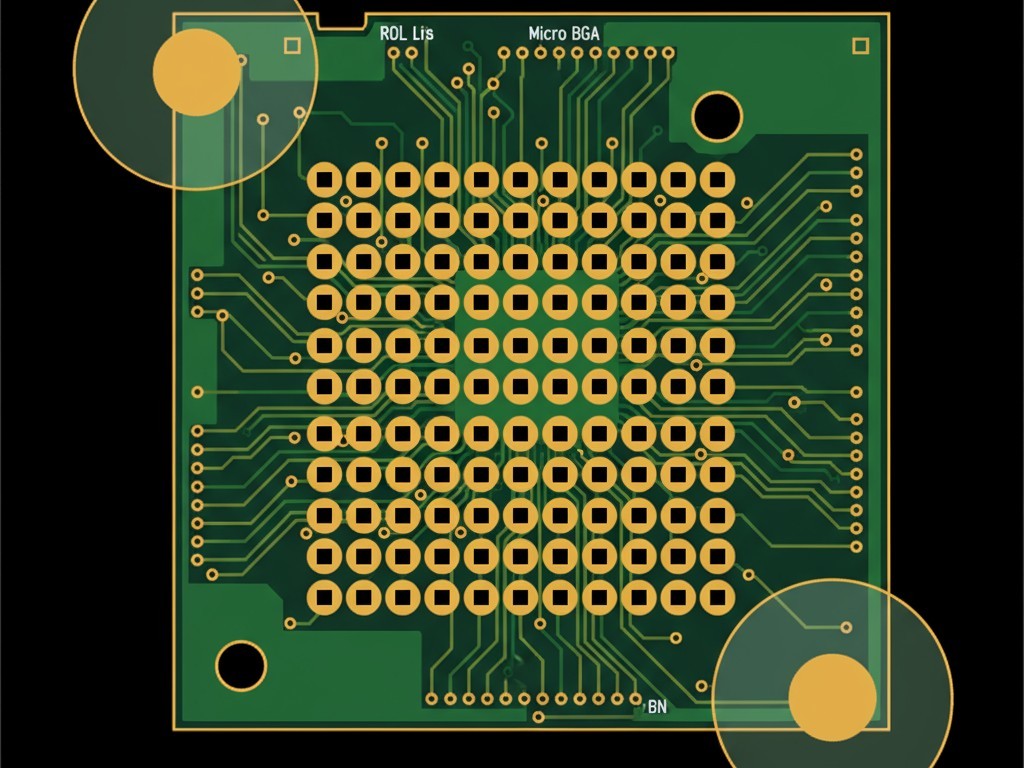

Micro-BGAs setzen eine andere Reihe von Beschränkungen durch. Mit vorinstallierten Lötbällen verschieben sich die Variablen von Paste-Druck zu Platzierungsgenauigkeit. Ein 0,5 mm Pitch BGA erlaubt nur 0,1 mm Fehler, bevor die Bälle ihr Ziel verfehlen. Die kleinen Pads, oft nur 0,25 bis 0,3 mm im Durchmesser, erfordern ebenso kleine und präzise Pastenablagerungen. Zu viel Paste verursacht Brücken; zu wenig führt zu schwachen Verbindungen oder Öffnungen. Die Fehlertoleranz ist eng bei ±10 Prozent des Zielvolumens.

Wenn diese Pakete koexistieren, wird eine dicke Schablone, die das thermische Pad eines QFN erfüllt, zu viel Paste auf die Micro-BGA-Pads abgeben. Eine dünne, für den BGA optimierte Schablone wird das QFN unterversorgen. Der Ertragsschwellenwert erscheint, wenn diese Konflikte ignoriert werden. Lötstellen auf dem thermischen Pad des QFN zeigen Lunker über 25 Prozent, was die Kriterien der IPC-A-610 Klasse 3 verletzt. Micro-BGA-Arrays weisen Brücken auf inneren Reihen oder Öffnungen bei den Ecken auf. Dies sind keine zufälligen Defekte, sondern deterministische Fehler, die in vorhersehbaren DFM-Fehlern verwurzelt sind.

Paste Aperture Tuning: Balance zwischen zwei Welten

Das Volumen des Lötpastenmaterials, gesteuert durch das Design der Schablonenöffnung, bestimmt die Qualität der Lötstelle. Das Volumen muss ausreichen, um eine zuverlässige Verbindung zu bilden, und muss sich sauber von der Schablone lösen. Für Platinen mit gemischten Paketen erfordert das Treffen beider Ziele eine sorgfältige Abstimmung der Öffnungsdimensionen und der Schablonendicke.

Das Flächenverhältnis bestimmt die Paste-Freisetzung. Das Verhältnis der Öffnungsfläche zur Wandfläche muss 0,66 übersteigen, um eine zuverlässige Paste-Freisetzung zu gewährleisten. Darunter haftet die Paste an den Wänden der Schablone statt, sich sauber zu verteilen. Eine 0,125 mm dicke Schablone, die auf eine 0,25 mm große Micro-BGA-Pad druckt, ergibt ein Flächenverhältnis von etwa 0,5—deutlich unter dem Schwellenwert. Das erzwingt eine Entscheidung: die Schablonendicke zur Verbesserung des Verhältnisses bei kleinen Pads zu verringern oder größere Öffnungen zu akzeptieren und das Risiko einer Überfüllung einzugehen.

Schablonendicke ist ein notwendiger Kompromiss. QFN-Thermalpads profitieren von dickeren Schablonen (0,150 mm oder mehr), während Micro-BGAs mit dünneren Schablonen (0,100 bis 0,125 mm) besser funktionieren. Wenn beide eine Schablone teilen, muss das Design auf das constrainingste Bauteil ausgelegt sein. Das bedeutet meist die Wahl einer 0,125 mm dicken Schablone und eine Kompensation für das QFN-Thermalpad durch Verringerung seiner Öffnungsfläche. Das bedeutet zwar eine kleinere Paste-Bettung auf dem Thermalpad, aber gewährleistet eine akzeptable BGA-Leistung. Designs, bei denen die thermische Leistung des QFN absolut entscheidend ist, erfordern möglicherweise einen kostspieligen Doppel-Print-Prozess mit zwei Schablonen.

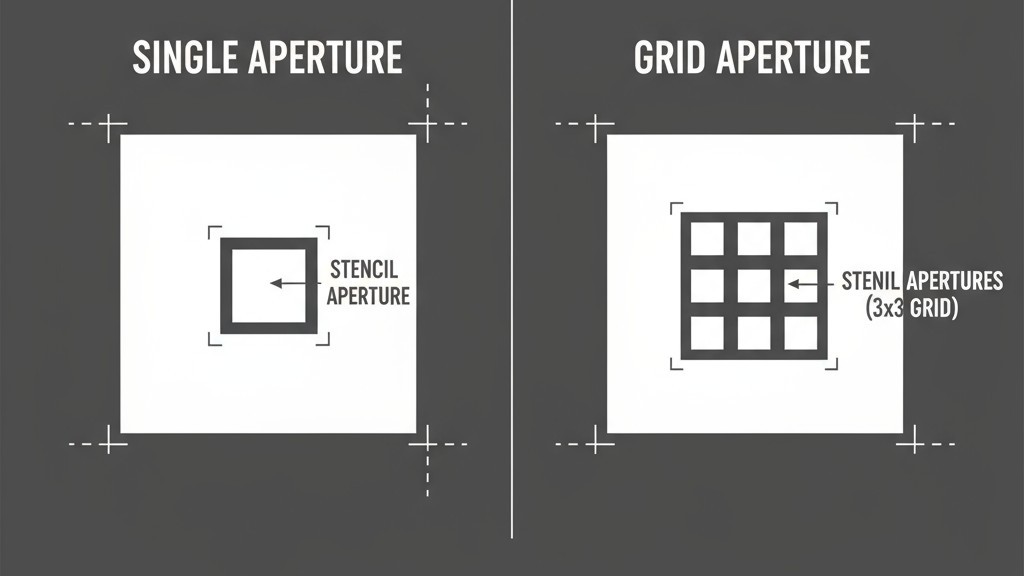

Thermoplattenöffnungen müssen absichtlich reduziert werden. Eine gängige Richtlinie ist, die Öffnungsfläche der thermischen Pad im QFN auf 50-80 Prozent der tatsächlichen Padfläche zu reduzieren. Dies verhindert, dass das Gehäuse während des Reflows auf überschüssigem Lötzinn schwimmt, und ermöglicht ein segmentiertes Aperturmuster. Ein Gitter aus kleineren Öffnungen, anstelle eines großen Fensters, verbessert die Paste-Entladung und verringert die Hohlräume, indem es dem eingeschlossenen Flussmittel einen Fluchtweg bietet. Ein typisches 5mm thermisches Pad könnte ein 3×3-Gitter aus 1,0mm quadratischen Öffnungen verwenden, das ein ausreichendes Lötvolumen bietet und gleichzeitig die Prozesskontrolle aufrechterhält.

Unsere Empfehlung ist, das Micro-BGA zu priorisieren. Wählen Sie eine dünnere Schablone für die Druckauflösung, und verbessern Sie die thermische Leistung des QFN durch Via-in-Pad-Design und sorgfältiges Aperturensplit. Dieser Ansatz minimiert BGA-Überbrückungen – die schwierigste Reparaturfehler – während eine handhabbare Reduktion des Lötvolumens des thermischen Pads beim QFN akzeptiert wird.

Via-in-Pad: Unnachgiebige Regeln und praktische Grenzen

Vias in Komponentenpads, üblich bei der thermischen Verwaltung von QFN und bei der Fluchtleitung für Micro-BGA, stellen ein erhebliches Zuverlässigkeitsrisiko dar, wenn sie nicht korrekt behandelt werden. Während des Reflow kann die Barrel des Via Lötzinn vom Joint wegziehen. Gleichzeitig können eingeschlossenen Luft und Flussmittel ausgasen, was zu Hohlräumen führt. Beide Mechanismen verschlechtern die Verbindung.

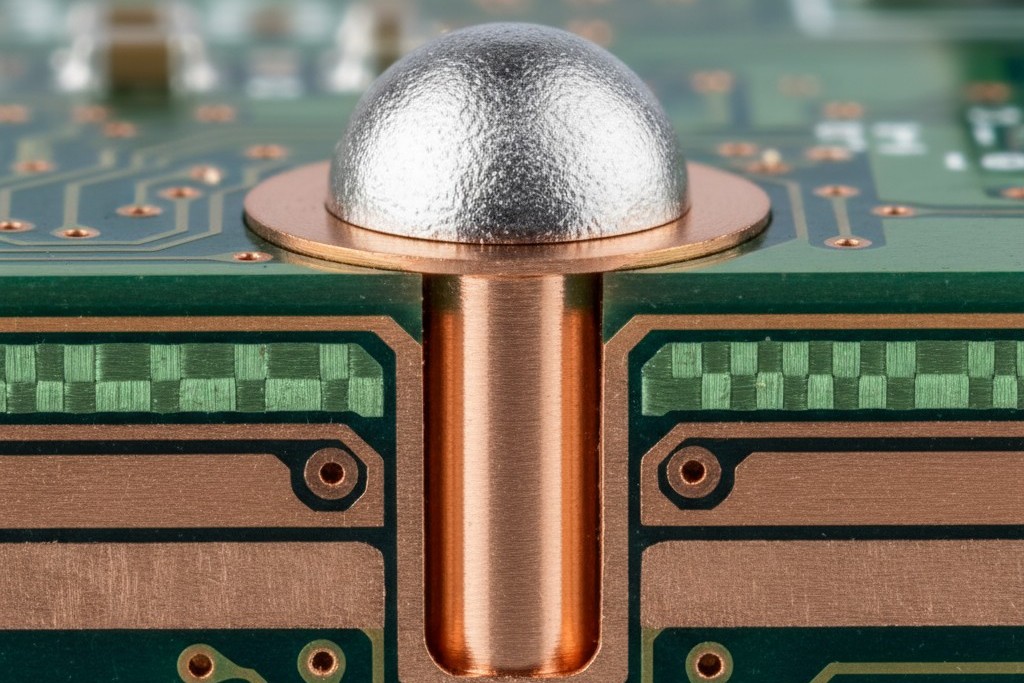

Kupfervollgefüllte und planparallele Via-Processing sind die zuverlässigsten Lösungen. Hier wird die Barrel des Vias mit Kupfer beschichtet, bis sie vollständig gefüllt ist, und die Oberfläche wird plan geschliffen. Dies eliminiert den Ausgasweg und verhindert das Wicking von Lötzinn. Die Spezifikation muss deutlich an den PCB-Fertiger kommuniziert werden, inklusive einer Füllquote von 95 Prozent oder mehr und der erforderlichen Oberflächenbeschaffenheit. Seriöse Fertiger zertifizieren diesen Prozess nach IPC-4761 oder IPC-6012 Klasse 3 Standards.

Nicht-leitfähige Füllung ist eine kostengünstigere Alternative. Ein Epoxidstopfen versiegelt das Via, blockiert das Ausgasen, verhindert jedoch nicht so effektiv das Wicking von Lötzinn wie eine vollständige Kupferfüllung. Dieser Ansatz kann für QFN-thermische Pads in weniger anspruchsvollen Klasse-2-Assemblies akzeptabel sein, ist jedoch eine schwächere Lösung für Micro-BGAs, bei denen das Paste-Volumen viel enger bemessen ist.

Wenn Ihr Fertiger keine vollständige Via-Füllung garantieren kann

Wenn eine vollständige Via-Füllung nicht möglich oder praktikabel ist, muss das Design angepasst werden.

- Via-Tenting: Das Aufbringen von Lötstopplack über die Via-Öffnung bietet einen teilweisen Schutz. Das Tenting der Oberseite der Leiterplatte direkt unter dem Pad ist am effektivsten, erfordert jedoch eine hohe Präzision bei der Lötstoppmasken-Registrierung.

- Plugging: Die Verwendung von nicht leitfähischer Paste, um das Via zu verschließen, ist besser als Tenting, reicht aber nicht für eine vollständige Füllung. Der Plug ist möglicherweise nicht planparallel, was eine Oberflächenvertiefung hinterlässt, die die Paste-Druckkonsistenz beeinträchtigt – ein erhebliches Risiko für Micro-BGAs.

- Offene Vias akzeptieren: Dies ist ein letzter Ausweg, nur für Prototypen oder Low-Power-QFNs geeignet, bei denen eine Vertiefung von bis zu 50 Prozent tolerierbar ist. Offene Vias in Micro-BGA-Pads sind aufgrund des hohen Risikos des Lötverlustes nahezu nie akzeptabel.

Füllungen, eine flüssige Epoxidharz, die um ein BGA herum aufgetragen wird, verbessern die mechanische Zuverlässigkeit, indem sie die Spannung auf die Lötstellen verteilen. Obwohl sie nicht immer erforderlich ist, ist sie bei Anwendungen mit thermischem Zyklus oder Stoßeinwirkung üblich. Wenn sie vorgeschrieben ist, muss das Leiterplattenlayout den Auftragssprozess berücksichtigen.

Unterfüll-Restriktionszonen: Planung für die Prozessrealität

Unterfüllung, ein flüssiges Epoxidharz, das um ein BGA herum aufgetragen wird, verbessert die mechanische Zuverlässigkeit, indem sie die Spannung auf die Lötstellen verteilt. Obwohl sie nicht immer erforderlich ist, ist sie bei Anwendungen mit thermischem Zyklus oder Stoßeinwirkung üblich. Wenn sie vorgeschrieben ist, muss das Leiterplattenlayout den Auftragssprozess berücksichtigen.

Die Dosiernadel benötigt einen Abstand von 1 bis 2 mm vom Paketrand für einen gleichmäßigen Fluss. Zu dicht platzierte Komponenten können die Nadel blockieren oder Barrieren bilden, was zu Lufteinschlüssen und unvollständiger Abdeckung führt. Diese Ausschlusszone muss früh im Layout festgelegt werden, da das Verschieben von Komponenten später oft eine Neuanfertigung erzwingt.

Die Höhe der Komponenten innerhalb dieser Zone ist genauso kritisch wie die seitliche Freiraumgestaltung. Hohe Komponenten wirken wie Dämme, die den Unterfüllfluss blockieren. Das Layout sollte eine klare, ebene Fläche innerhalb des Ausschlussbereichs bewahren, ohne dass Komponenten die Abstandshöhe des BGA übersteigen (typischerweise 0,3 bis 0,5 mm). Für Designs, bei denen Nacharbeiten erwartet werden, sollte dieser Ausschlussbereich auf 3 mm oder mehr erweitert werden, um Zugang für Entfernen-Werkzeuge zu ermöglichen.

Board Rails und Panel-Design für die Montage

Leiterplattenbahnen, der nicht-funktionale Rand eines PCB-Panels, sind die mechanische Schnittstelle für alle Montagesysteme. Zu kleine oder schlecht gestaltete Bahnen verursachen, dass sich das Panel während des Drucks verzieht oder bei der Platzierung verschiebt, was die Ausbeute beeinträchtigt.

Die minimale Bahnweite für gemischte QFN- und Micro-BGA-Baugruppen sollte 7 bis 10 mm pro Seite betragen. Dies bietet ausreichend Greiffläche für Förderbänder und Spannvorrichtungen. Schmalere Bahnen, die verwendet werden, um die Anzahl der Boards pro Panel zu maximieren, verursachen während des Maskendrucks eine Biegung des Panels, was ungleichmäßige Pastenablagerungen zur Folge haben kann. Die Einsparungen durch schmalere Bahnen werden fast immer durch geringere Ausbeute zunichte gemacht. Für Boards, die dünner als 1,6 mm sind, kann eine temporäre Verstärkungsstange, die während des Drucks an die Bahn geklemmt wird, diese Biegung verhindern.

Werkzeuglöcher und Fiduzer an den Bahnen dienen als Referenzpunkte für die Automatisierung. V-Scoring oder Tab-Routing für die Trennung beeinflusst ebenfalls das Bahnendesign. Bei gemischten QFN- und Micro-BGA-Designs ist Tab-Routing oft vorteilhaft, da es erlaubt, feinabgestimmte Komponenten näher am Rand der Leiterplatte zu platzieren, um eine bessere Signallenkung zu gewährleisten.

Fiducial-Strategie: Genauigkeit durch Disziplin

Fiduzien, die optischen Referenzmarken für Pick-and-Place-Maschinen, bestimmen direkt die Platzierungsgenauigkeit. Für diese Platinen, bei denen Toleranzen im Zehntel-Mikrometer-Bereich gemessen werden, ist die Fiduzienstrategie eine primäre Anforderung im Design und kein nachträglicher Gedanke.

Globale Fiduzien bieten panelüberschreitende Registrierung. Drei nicht-kollineare Markierungen müssen auf den Leiterplattenbahnen platziert werden, so weit wie möglich voneinander entfernt, um dem Bildverarbeitungssystem die Berechnung von Position, Drehung und Skalierungsfehlern zu ermöglichen. Jede globale Fiduzie benötigt eine klare Ausschlusszone, typischerweise mit einem Radius von 3 bis 5 mm, frei von Features, die das Vision-System verwirren könnten.

Lokale Fiduzien sind für jedes Micro-BGA erforderlich und sehr empfohlen bei feinen Baugruppen wie QFNs. Sie bieten die Bauteilverzerrungs-Kalibrierung auf Komponentenebene, korrigieren lokale Verzerrungen der Leiterplatte. Für ein Micro-BGA sind zwei lokale Fiduzien, die diagonal über das Gehäuse platziert werden, innerhalb von 10 bis 15 mm von dessen Rand, optimal für Genauigkeit.

Ein typischer Fiduzial ist ein 1 mm großer Kupferring innerhalb einer 2 mm großen Lötmaskenöffnung. Dies sorgt für hohen Kontrast für die Bildverarbeitungskamera. In dichten Layouts, in denen der ideale Abstand nicht möglich ist, kann der Abstand auf mindestens 5 mm reduziert werden. Als letzte Möglichkeit kann eine große QFN-Ecken-Pad oder eine BGA-Ecken-Ball-Pad als Fiduzialziel festgelegt werden, aber dies ist eine risikoreiche Strategie.

Das letzte Tor: Vor-Tab-Kontrolle der DFM-Verifizierung

Eine systematische Überprüfung dieser fünf kritischen Bereiche vor dem Tape-out ist die letzte Chance, Fehler zu erkennen.

Die Verifikation sollte mit einer Peer-Review beginnen, die sich auf diese spezifischen risikoreichen Bereiche konzentriert. Automatisierte DFM-Software kann einige Probleme kennzeichnen, aber sie kann die nuancierten Abwägungen im Paste-Apertur-Design oder bei via-in-pad-Entscheidungen nicht bewerten. Menschliches Urteilsvermögen ist entscheidend. Führen Sie anschließend eine Beratung mit Ihrem geplanten Fertigungs- und Montagelabor durch. Das Teilen Ihrer Daten ermöglicht es ihnen, prozessspezifische Risiken zu erkennen, bevor das Design endgültig festgelegt wird.

Ihre Pre-Tape-out-Checkliste muss enthalten:

- Schablonen-Öffnungen: Exportierte und überprüfte Daten auf korrekte Flächenverhältnisse bei allen Mikro-BGA-Pads und die richtige Reduzierung bei QFN-Thermopads.

- Via-in-Pad: Spezifikationen klar dokumentiert in Fertigungsnotizen, inklusive Füllmethode und Akzeptanzkriterien.

- Underfill-Beschränkungen: Zonen geprüft für alle Mikro-BGAs, keine Komponenten, die den Abstand verletzen.

- Leiterplatten-Schienen: Breite bestätigt, um die Mindestmaße für die Paneelsteifigkeit zu erfüllen.

- Fiduzialen: Global und lokal Platzierung überprüft auf Größe, Abstand und Ausschlusszonen.

- Lackierung: Abstände auf Micro-BGA-Pads bestätigt, dass sie nicht durch Lack definiert sind (NSMD).

- Depaneling: Methode und Randabstände verifiziert, um eine Beschädigung der Komponenten zu verhindern.

Das Abschließen dieser Tors ist, was DFM von einem abstrakten Ziel in ein messbares Ergebnis verwandelt. Es ist der Unterschied zwischen einem reibungslosen ersten Bau und einem kostspieligen Neudruck.