Der Druck, die Zeitpläne für die Produktentwicklung zu verkürzen, ist unerbittlich, aber die Konsequenzen von Verzögerungen waren noch nie so hoch. Finanzierungsmeilensteine verschieben sich, Marktfenster schließen sich und Wettbewerber liefern zuerst. Für Hardware-Teams spannt das Zugunglück zwischen einem funktionierenden Prototyp und einer Pilotproduktion — ein Labyrinth aus Abhängigkeiten, Genehmigungen und Herstellungsrealitäten — typischerweise sechzig bis neunzig Tage. Schnelligkeit war schon immer wichtig, aber ist dreißig Tage ein realistisches Ziel für eine komplexe Leiterplattenmontage (PCBA), oder eine aspirative Fiktion, die Teams auf Misserfolg vorbereitet?

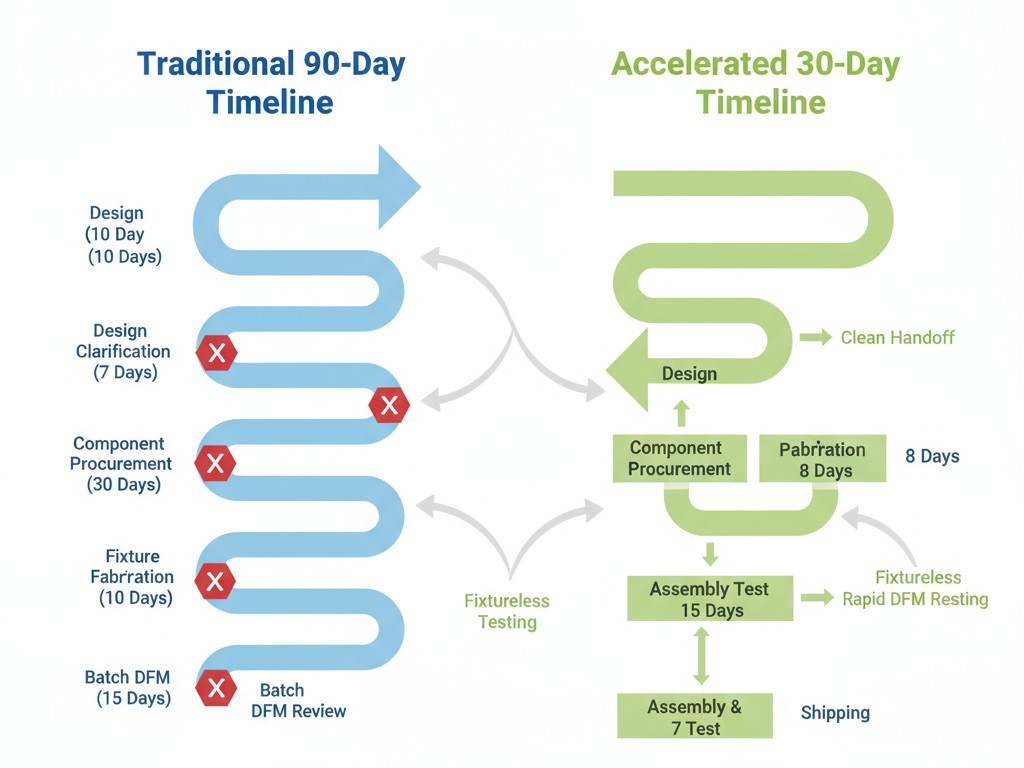

Bei Bester PCBA wissen wir, dass die dreißig Tage schnelle Hochlaufphase erreichbar sind, aber nur, wenn drei spezielle Systeme parallel optimiert und mit Präzision ausgeführt werden. Hier geht es nicht darum, schneller zu arbeiten oder Abkürzungen zu nehmen. Es geht darum, die strukturellen Verzögerungen zu beseitigen, die in traditionellen Arbeitsabläufen endemisch sind. Der Unterschied zwischen einem dreißig Tage Zyklus und einem neunzig Tage Zyklus liegt nicht im Aufwand; es ist die Gestaltung des Prozesses selbst. Wenn eine Designübergabe beim ersten Durchlauf sauber ist, wenn werkzeuglose Tests den Engpass bei kundenspezifischen Werkzeugen entfernen und wenn Feedback zur Design for Manufacturability (DFM) in Stunden statt in Tagen erfolgt, verkürzt sich der gesamte kritische Pfad. Bei Ausfall in einem dieser Bereiche verzögert sich der Zeitplan und wird zur branchenüblichen Schleife.

Dies ist der Betriebsplan für diese dreißig Tage Umsetzung, ein Rahmen, der auf mechanischen Realitäten und nicht auf Marketingversprechen basiert. Wir werden die Designübergabe untersuchen, die Mehrdeutigkeiten verhindert, die werkzeuglose Teststrategie, die eine mehrwöchige Verzögerung eliminiert, und das DFM-Protokoll, das das Engineering-Feedback daran hindert, einen Engpass zu werden. Für Teams, die komplexe, mehrlagige Platinen bauen, ist dies das Spielbuch zur Risikoreduzierung eines aggressiven Zeitplans bei gleichzeitiger Beibehaltung der Pilotqualität.

Warum dreißig Tage die Ausnahme und nicht die Regel sind

Der Median der Branche in der Elektronikfertigung von Prototypgenehmigung bis zu einer einsatzbereiten PCBA liegt zwischen sechzig und neunzig Tagen. Das liegt nicht daran, dass Hersteller langsam sind; sondern daran, dass der Prozess als Reihe sequenzieller Tore aufgebaut ist, die jeweils Latenzzeiten einführen. Unvollständige Design-Daten lösen Klarstellungsschleifen aus, die fünf Tage in Anspruch nehmen, bevor die Herstellung beginnen kann. Kundenindividuelle Testvorrichtungen, die für die traditionelle Validierung unerlässlich sind, benötigen Vorlaufzeiten von zwei bis drei Wochen. Feedback zur DFM, das als Stapelprozess und nicht als kontinuierlicher Dialog behandelt wird, kann eine Woche oder mehr in Anspruch nehmen.

Diese Verzögerungen summieren sich. Ein Verzögerung von zwei Tagen bei DFM-Feedback verschiebt den Starttermin der Fertigung, was die Platinenlieferung verzögert, was die Montage verzögert und was wiederum die Tests verzögert. Wenn der Pilotaufbau fertig ist, hat sich das Ziel von dreißig Tagen auf siebzig verlängert. Das Problem liegt nicht bei einem einzelnen Anbieter oder Prozessschritt. Es ist die Ansammlung kleiner Ineffizienzen in einem Workflow, bei dem jede Stufe von der vorherigen abhängt. Auf dem kritischen Pfad gibt es keine kleineren Verzögerungen.

Ein dreißig Tage Zyklus ist im Gegensatz dazu so konzipiert, dass er keine Puffer zulässt. Es erfordert, dass jede Übergabe sauber ist, jeder Prozess parallelisiert wird und jede Entscheidung vorab geklärt ist. Deshalb bleibt es die Ausnahme. Die meisten Organisationen fehlen die Disziplin, um beim ersten Durchlauf vollständige Design-Daten zu liefern. Die meisten Hersteller verfügen nicht über die Ingenieurkapazität für sofortiges DFM-Feedback. Die meisten Testabläufe basieren noch auf Vorrichtungen, die Wochen Vorlaufzeit benötigen. Der Hochlauf innerhalb von dreißig Tagen ist nicht unmöglich; er lässt nur die üblichen Ineffizienzen, die längere Zeitpläne aufnehmen sollen, ungenutzt.

Der kritische Pfad: Drei Tore, die Ihren Zeitplan bestimmen

Jeder Fertigungsprozess wird durch seinen kritischen Pfad gesteuert — die Abfolge abhängiger Aufgaben, die die minimale mögliche Fertigstellungszeit bestimmt. Eine Verzögerung bei einer beliebigen Aufgabe auf diesem Pfad verlängert das gesamte Projekt um denselben Zeitraum.

Für einen Pilotanstieg bei der PCBA-Steuerung wird der kritische Pfad durch drei Tore kontrolliert: Designübergabe Präzision, Architektur für werkzeugloses Testenund Geschwindigkeit des DFM-Feedbacks. Dies sind keine unabhängigen Variablen, sondern miteinander verbundene Systeme. Das Optimieren aller drei ist das, was einen komprimierten Zeitplan realisierbar macht. Ein präziser Übergabepunkt bestimmt, wann die Fertigung beginnen kann. Fixture-Tests ohne Vorrichtungen bestimmen, wann Boards validiert werden können, ohne auf Werkzeuge zu warten. Schnelles DFM-Feedback stellt sicher, dass Designrisiken vor Rework oder Verzögerungen behoben werden. Zusammen bilden sie das Rückgrat des Schnellversetzungsprozesses.

1. Präzision bei der Designübergabe

Die erste Hürde ist die Vollständigkeit des Designpakets. Unvollständige Daten sind die größte Quelle vermeidbarer Verzögerungen. Wenn Gerber-Dateien Ebenen fehlen, ein Stücklistenschema (BOM) keine Herstellernummern enthält oder Montagestellenbzeichnungen mehrdeutig sind, kommt der Prozess zum Stillstand. Engineering-Teams werden in eine Schleife aus E-Mails und Klärungsgesprächen gezwungen, wobei jeder Zyklus mindestens einen Tag dauert. In einem sechzig Tage langen Zeitplan ist das ärgerlich. In einem dreißig Tage langen Zeitplan ist es fatal.

2. Architektur für Tests ohne Vorrichtungen

Die zweite Hürde betrifft die Validierung der montierten Boards. Traditionelle In-Circuit-Testvorrichtungen sind kundenspezifische mechanische Baugruppen, die federbelastete Sonden auf Testpunkte ausrichten. Sie sind präzise, aber auch langsam in der Herstellung, benötigen bis zu drei Wochen für Design, Fertigung und Debugging. Dies ist ein dreith-week serialized Prozess, der direkt auf dem kritischen Weg liegt. Vorrichtungslose Methoden wie Flying Probe oder Boundary Scan eliminieren diese Abhängigkeit vollständig, indem sie programmierbare Sonden oder eingebettete Testlogik verwenden. Obwohl die Durchsatzrate niedriger sein kann, ist bei Pilotmengen von zehn bis hundert Einheiten die Strafe vernachlässigbar im Vergleich zu den Wochen, die durch eingesparte Kalenderzeit gewonnen werden.

3. Geschwindigkeit des DFM-Feedbacks

Die dritte Hürde ist die Geschwindigkeit der Design-for-Manufacturability (DFM)-Analyse. Eine gründliche DFM-Überprüfung erkennt Risiken—unzureichende Abstände, Lötstoppmasken-Risse, schlechte thermische Konstruktion—die die Ausbeute oder Zuverlässigkeit beeinträchtigen könnten. Wenn das DFM-Feedback innerhalb von Stunden nach der Designübergabe eintrifft, werden Korrekturen vorgenommen, bevor die Fertigung beginnt. Bei einer Dauer von fünf Tagen verschiebt sich der gesamte Zeitplan um diese Zeit. Wenn das Feedback Designänderungen erfordert, dehnt sich die Verzögerung noch weiter aus.

Während Komponentenlieferzeiten und Boardkompliziertheit ebenfalls eine Rolle spielen, sind diese drei Hürden die Faktoren, die am direktesten durch das Prozessdesign kontrolliert werden. Bester PCBA hat sie speziell optimiert, um den dreißig-tägigen Start zu ermöglichen.

Checkliste für die Designübergabe: “Vollständig” definieren

Der Begriff “vollständiges Designpaket” ist gebräuchlich, aber selten präzise genug definiert, um Mehrdeutigkeiten zu vermeiden. Ein vollständiges Paket ist nicht nur eine Sammlung von Dateien; es garantiert, dass das Fertigungsteam sofort mit DFM und Fertigungsplanung fortfahren kann, ohne eine einzige Frage zu stellen. Unvollständigkeit zeigt sich immer auf vorhersehbare Weise: fehlende Bohrdateien, veraltete Stücklisten oder uneindeutige Zeichnungen. Jeder Fall löst eine Anfrage aus, und jede Anfrage führt zu Verzögerungen.

Unsere Definition von Vollständigkeit ist ein Zustand nuller Mehrdeutigkeit, erreicht durch die Einhaltung einer strengen Checkliste, die um Fertigungsdaten, BOM-Integrität und Montage-Dokumentation organisiert ist.

Gerber-Dateien und Fertigungsdaten

Das Gerber-Set muss alle Ebenen enthalten: Kupfer, Lötstoppmaske, Siebdruck und Paste-Maske, jeweils korrekt benannt. Die Bohrdatei muss alle Lochgrößen und Plattierungsanforderungen angeben. Die Fertigungszeichnung muss die Board-Abmessungen, den Layer-Stack, den Materialtyp (z.B. FR-4 oder Hochfrequenzlaminat), Kupfergewichte und Oberflächenfinish festlegen. Für Boards mit kontrollierter Impedanz muss der Stack-up die Dielektrizitätsdicke, Ziel-Impulswerte und die spezifischen Traces, die kontrolliert werden müssen, definieren. Mehrdeutige Fertigungsdaten sind die häufigste Ursache für Verzögerungen. Wenn ein Hersteller raten muss, läuft die Uhr bereits.

Integrität der Stückliste

Die BOM ist die autoritative Liste aller Komponenten, die beschafft und montiert werden sollen. Eine vollständige BOM muss Referenzbezeichner, Menge, Herstellername und—am wichtigsten—die vollständige Herstellernummer für jeden Posten enthalten. Eine BOM, die “10k Widerstand 0402” auflistet, ist nicht umsetzbar. Eine, die “Yageo RC0402FR-0710KL” auflistet, ist es, weil sie ein genaues, kaufbares Bauteil spezifiziert.

Eine unvollständige BOM verursacht zwei Fehlermodi: Beschaffungsverzögerungen und Montagefehler. Allgemeine Teilenummern erzwingen Klarstellungen oder riskante Substitutionen. Nicht übereinstimmende Referenzbezeichner zwischen BOM und Gerbern führen zu falsch platzierten Komponenten und Nacharbeit. Außerdem gilt Integrität auch für die Verfügbarkeit. Eine BOM ist nicht vollständig, wenn die Hälfte der Teile eine Vorlaufzeit von zwölf Wochen hat. Validierung der Komponentenverfügbarkeit vor Das Übergabeverfahren ist unverhandelbar.

Eine 30-tägige BOM-Checkliste umfasst:

- Herstellernummern für alle Komponenten; keine Generika.

- Referenzbezeichner, die genau mit Gerber- und Montage-Dateien übereinstimmen.

- Vorlaufzeit-Validierung für alle Komponenten.

- Alternative Teilenummern für alle ausschließlich bezogenen oder hochriskanten Komponenten.

- Klar gekennzeichnete vom Kunden gelieferte Komponenten.

Montagedokumentation und Komponentenplatzierungsdateien

Montagedokumentation umfasst die Montagezeichnung, eine Komponentenplatzierungs- (oder Centroid-) Datei und etwaige spezielle Anweisungen. Die Montagezeichnung muss eine visuelle Referenz für die Lage, Ausrichtung und Polarität jeder Komponente sein, generiert aus dem endgültigen Leiterplattenlayout. Die Platzierungsdatei liefert die X-Y-Koordinaten, die die Pick-and-Place-Maschine für die Automatisierung verwendet.

Spezielle Anweisungen decken nicht standardisierte Prozesse ab: ein Stecker, der nach der Konformalbeschichtung montiert werden muss, eine hitzeempfindliche Komponente, die ein niedrigeres Reflow-Profil benötigt, oder ein IC, der aufgrund der Feuchtigkeitsempfindlichkeit ausgebacken werden muss. Diese Details scheinen dem Konstruktionsteam offensichtlich, sind für den Montagearbeiter jedoch unsichtbar. Vollständige Dokumentation beseitigt Interpretationsspielräume und hält die Linie in Bewegung.

Fixture-lose Teststrategie: Die Engpassbeseitigung

Tests bestätigen, dass eine montierte PCBA vor dem nächsten Schritt funktioniert. Traditionelle Fertigungsprozesse setzen auf speziell gefertigte Testfixturen, um physischen Zugriff auf Testpunkte auf der Platine zu ermöglichen. Für die Massenproduktion rechtfertigt die Anfangsinvestition in eine kundenspezifische Fixtur deren Schnelligkeit und Wiederholbarkeit. Für Kleinserien im Pilotbetrieb ist die Fixtur jedoch ein Engpass.

Warum traditionelle Fixuren das Dreißig-Tage-Modell durchbrechen

Eine kundenspezifische Testfixtur ist eine mechanische Baugruppe, die entworfen, gefertigt und validiert werden muss, bevor der Test beginnen kann. Dieser mehrwöchige Prozess beinhaltet die Analyse des Layouts, das Erstellen eines Fixtur-Designs, die Bearbeitung der Hardware und die Fehlersuche an der Endmontage. Für eine komplexe Platine kann dies leicht drei Wochen dauern.

Dies ist eine serialisierte Abhängigkeit. Die Montage kann erst in die Testphase übergehen, wenn die Vorrichtung fertig ist. Bei einem Zeitrahmen von sechzig Tagen ist eine Vorlaufzeit von drei Wochen für die Vorrichtung gut machbar. Bei einem Zeitrahmen von dreißig Tagen beansprucht sie die Hälfte des Kalenders, ohne Spielraum für Fehler. Die Lösung ist eine vorrichtungslose Teststrategie, die es ermöglicht, mit dem Testen zu beginnen, sobald die Platinen die Montagelinie verlassen.

Flying Probe und Boundary Scan als Alternativen

Flying Probe Testsysteme verwenden zwei oder mehr unabhängig kontrollierte Sonden, die zu bestimmten Testpunkten bewegen, um elektrische Messungen durchzuführen. Die Testsequenz wird direkt aus CAD-Daten programmiert, so dass keine physische Vorrichtung gebaut werden muss. Die Rüstzeit wird in Stunden und nicht in Wochen gemessen. Der Kompromiss liegt beim Durchsatz; das Testen ist sequenziell, was pro Platine länger dauert. Für Pilotserien von zehn bis fünfzig Einheiten ist dieser Kompromiss äußerst vorteilhaft. Ein fünfminütiger Test, der eine dreiwöchige Wartezeit eliminiert, ist eine einfache Entscheidung.

Boundary Scan ist eine weitere vorrichtungslose Methode, die eingebettete Testlogik innerhalb von ICs nutzt, die den IEEE 1149.1 (JTAG) Standard unterstützen. Sie ermöglicht es, Testgeräte die Zustände der IC-Pins zu kontrollieren und zu beobachten, ohne physischen Kontakt, was bei Boards mit hochdichten BGA-Bausteinen, bei denen Testpunkte unzugänglich sind, unschätzbar wertvoll ist. Ihre Einschränkung ist, dass sie nur bei Komponenten mit eingebauter Unterstützung funktioniert. Bei Boards mit gemischten Komponententypen wird Boundary Scan oft mit Flying Probe kombiniert, um eine vollständige Abdeckung zu erreichen.

Testabdeckungs-Kompromisse bei Pilotmengen

Vorrichtungslose Tests sind nicht ohne Kompromisse. Die Testabdeckung kann im Vergleich zu einer vollen Nadelbettvorrichtung geringer sein. Für die Massenproduktion, bei der die Kosten eines einzigen entkommenen Defekts mit Tausenden multipliziert werden, ist die maximale Abdeckung entscheidend. Bei Pilotmengen, bei denen das primäre Ziel die Validierung der Designfunktionalität und das Aufspüren großer Montagefehler ist, ist die Abdeckung durch vorrichtungslose Methoden in der Regel ausreichend. Der Schlüssel ist die Wahl einer Teststrategie, die Abdeckung, Zeitplan und Kosten auf die spezifischen Bedürfnisse des Projekts ausrichtet, anstatt aus Gewohnheit zum traditionellen Ansatz zurückzukehren.

DFM-Reaktionszeiten: Die Feedback-Schleife, die zählt

DFM-Analyse ist die Methode, mit der Fertigungsingenieure Probleme erkennen, die die Ausbeute, Zuverlässigkeit oder Kosten beeinträchtigen könnten. Jede Platine wird überprüft. Die einzige Frage ist, ob dies proaktiv, als strukturierte Feedback-Schleife vor der Fertigung, oder reaktiv, als Reihe von Problemen, die auf der Linie entdeckt werden und Verzögerungen sowie Ausschuss verursachen, geschieht. Der Unterschied entscheidet oft darüber, ob der Zeitplan dreißig oder sechzig Tage umfasst.

Was DFM vor der Fertigung erkennt

Eine DFM-Überprüfung kennzeichnet Designregeln, die technisch innerhalb der Spezifikation liegen, aber keinen Spielraum für Prozessvariationen lassen, wie zum Beispiel eine Leitungsbreite, die dem absoluten Minimum des Herstellers entspricht. Die Überprüfung empfiehlt eine sicherere Dimension, die nichts kostet, aber die Ausbeute erheblich verbessert. Sie validiert die Schichtaufbaustruktur gegen Impedanzanforderungen und überprüft Komponentenplatzierungen, die die Werkzeugführung behindern oder Reflow-Defekte wie Tombstoning verursachen könnten.

Der Wert von DFM liegt nicht nur darin, Probleme zu erkennen; es geht darum, sie zu einem Zeitpunkt zu erkennen, an dem sie billig und schnell zu beheben sind. Ein Verstoß gegen den Leitungsspalt, der in DFM entdeckt wird, bedeutet eine einstündige Layout-Änderung. Dieselbe Verletzung nach der Fertigung bedeutet, die Platinen zu entsorgen und von vorne zu beginnen – eine Verzögerung von zwei Wochen. Deshalb ist die Reaktionszeit bei DFM im kritischen Pfad.

Die variable Fertigungskapazität

DFM-Antwortzeit ist nicht nur eine Funktion der Konstruktionskomplexität; sie ist eine Funktion der verfügbaren Ingenieurskapazität. Eine einfache Platine kann von einem erfahrenen Ingenieur in Stunden überprüft werden, aber es wird trotzdem Tage dauern, wenn dieser Ingenieur eine hohe Arbeitsbelastung hat.

Bei Bester PCBA strukturieren wir unsere Ingenieurskapazität so, dass wir für Schnellverfahren Projekte am selben Tag oder am nächsten Tag DFM-Feedback liefern. Dies ist eine bewusste betriebliche Entscheidung, die ein größeres Engineering-Team und diszipliniertes Priorisieren erfordert. Es ist eine Investition in Geschwindigkeit und ein entscheidender Faktor für den verkürzten Zeitplan.

Wie man schnell auf DFM-Feedback reagiert

Die Geschwindigkeit, mit der ein Designteam auf DFM-Feedback reagiert, bestimmt, wann die Leiterplatte in die Fertigung geht. Der effektivste Ansatz ist, DFM als einen synchronen Prozess zu behandeln. Wenn das Design übergeben wird, sollte das Team bereit für schnelle Iterationen sein. Bei kritischen Platinen empfehlen wir eine Live-Reviewsitzung, in der Fertigungs- und Designingenieure Probleme in Echtzeit lösen.

Iteration ist der Feind des dreißig Tage langen Zeitplans. Jede Schleife fügt Tage hinzu. Der beste Weg, sie zu minimieren, ist, von Anfang an ein sauberes, fertigungstüchtiges Design zu liefern, was auf die Übergabeliste zurückzuführen ist. Ein sauberes Design führt zu minimalem DFM-Feedback, und die Schleife schließt sich schnell.

Leiterplattenkomplexität und die Machbarkeitsgrenze

Der dreißig Tage Zeitplan ist für eine Vielzahl von Platinen erreichbar, aber nicht für alle. Komplexität ist die primäre Variable, die die Machbarkeit bestimmt. Eine einfache Zweischicht-Platine kann in Tagen fertiggestellt werden. Eine Zwölfschicht-Rigid-Flex-Platine mit Blind- und Knotenvias, impedance-kontrollierten Paaren und 0,4mm Pitch BGAs erfordert längere Fertigungszyklen und eine intensivere Montage, was den Zeitrahmen ausdehnt.

- Schichtanzahl ist der direkteste Treiber. Eine Vier-Schicht-Platine benötigt drei bis fünf Tage für die Fertigung; eine Zwölfschicht-Platine mit Blind-Vias kann zehn bis zwölf Tage benötigen. Bei Platinen mit mehr als acht Schichten wird das dreißig-Tage-Fenster deutlich enger.

- Bauteildichte und Paketarten beeinflussen ebenfalls die Machbarkeit. Eine Platine mit 01005-Passiven und 0,4mm Pitch BGAs erfordert eine engere Prozesskontrolle während des Reflows und erhöht das Risiko von Defekten, die Nacharbeiten erfordern.

- Impedanzkontrolle erhöht die Fertigungskomplexität und das DFM-Risiko. Es erfordert präzise Materialdicken und Validierung, und wenn die Impedanz außerhalb der Spezifikation liegt, müssen die Platinen verworfen und neu gefertigt werden.

Das Ziel ist nicht, komplexe Designs zu entmutigen, sondern realistische Erwartungen zu setzen. Für eine sechs-Schicht-Platine mit Standardkomponenten ist ein dreißig-tägiger Zeitrahmen konservativ. Für eine zehn-Schicht-Platine mit dichten BGAs und engen Impedanztoleranzen ist es erreichbar, erfordert jedoch eine makellose Ausführung ohne Spielraum für Fehler.

Ausführung des Dreißig-Tage-Zuwachses: Ein integrierter Rahmen

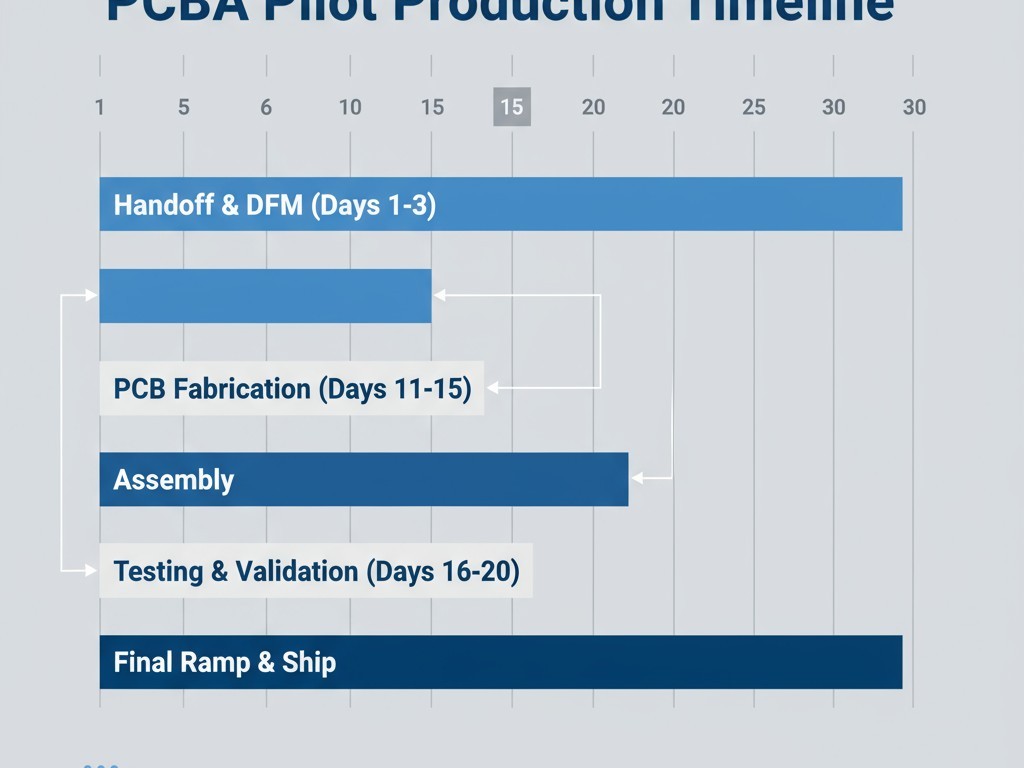

Der dreißigtägige Zeitplan ist eine streng choreografierte Sequenz. Dieses Rahmenwerk skizziert einen realistischen Tag-für-Tag-Fortschritt für eine komplexe Leiterplatte mit sechs bis acht Schichten und einer Pilotmenge von zwanzig bis fünfzig Einheiten.

Tage 1–3: Übergabe und DFM Am ersten Tag erreicht das vollständige Designpaket. Die DFM-Überprüfung beginnt sofort. Bis zum Ende des zweiten Tages wird Feedback geliefert. Am dritten Tag reicht das Designteam korrigierte Dateien ein, und die Leiterplatte ist für die Fertigung freigegeben. Diese Phase zeigt, wie wertvoll die ÜbergabCheckliste ist; ein unvollständiges Paket kann diese Phase auf eine Woche verlängern, was den Zeitplan sofort zunichtemacht.

Tage 4–10: Leiterplattenfertigung Die Fertigung beginnt am vierten Tag. Bei einer sechs Schichten Leiterplatte umfasst dies Bildgebung, Laminierung, Bohren, Plattierung und Endbearbeitung. Dieser Teil des Zeitplans ist am wenigsten komprimierbar, da er von physikalischen Prozessen bestimmt wird. Bare Boards werden am zehnten Tag an die Montageeinrichtung versendet.

Tage 11–15: Montage Bauteil-Kitaufnahme und Schablonenherstellung erfolgen am elften Tag. Lötpaste-Druck, Bestückung und Reflow finden in den nächsten zwei Tagen statt, gefolgt von manueller Montage. Die Inspektion wird am fünfzehnten Tag abgeschlossen. Das größte Risiko besteht hier in der Verfügbarkeit der Komponenten, weshalb die Validierung der Lieferzeiten während der Übergabe unverhandelbar ist.

Tage 16–20: Test und Validierung Test ohne Vorrichtung beginnt am sechzehnten Tag, sobald die Boards verfügbar sind. Montagefehler werden in den nächsten Tagen erkannt und nachbearbeitet. Da kein spezielles Prüfgerät erforderlich ist, beginnt diese Phase unmittelbar nach der Montage. Bei herkömmlichen Vorrichtungen würde das Testen erst am fünfundzwanzigsten Tag oder später beginnen.

Tage 21–30: Pilot-Einführung und Endgültige Validierung Bis zum einundzwanzigsten Tag wurden die ersten Boards getestet und der Montageprozess optimiert. Die verbleibenden Pilot-Einheiten werden gebaut, getestet und validiert. Die Endinspektion, Verpackung und Versand erfolgen bis zum dreißigten Tag. Das Produktteam hat jetzt funktionierende Pilot-Einheiten in der Hand, was gegenüber einem traditionellen Zyklus drei Wochen eingespart hat.

Die kritischen Abhängigkeiten sind klar. DFM muss bis zum dritten Tag abgeschlossen sein. Die Fertigung muss bis zum zehnten Tag beendet sein. Das Testen ohne Vorrichtung muss bis zum sechzehnten Tag beginnen. Jede Phase ermöglicht die nächste. Wenn alle drei Systeme optimiert sind, ist der dreißigtägige Zeitplan kein stretching goal. Es ist die natürliche Folge eines gut durchdachten Prozesses.