Der Druck, Fertigungsfehler vor dem Versand der Platinen zu erkennen, ist unverhandelbar. Ein einziger entkommener Fehler in einem kritischen System kann exponentiell teurer sein als der Test, der ihn erkannt hätte. Diese Realität treibt viele Engineering-Teams zur In-Circuit-Testing (ICT) als Standard, einer Methode, die lange Zeit als Goldstandard für die Abdeckung galt. Vollständiges ICT bietet umfassenden Zugang zu fast jedem Knoten auf einer Platine und verspricht Fehlererkennungsraten, die sich dem theoretischen Maximum nähern. Für die Massenproduktion macht die Investition Sinn; die Fixkosten für Fixture-Engineering und Prüfausrüstung amortisieren sich über Tausende von Einheiten, wodurch die Kosten pro Einheit auf vernachlässigbares Niveau sinken.

Aber die Wirtschaftlichkeit kehrt sich um, wenn die Produktionsmengen sinken. Für Läufe unter einigen hundert Einheiten werden die Stärken des ICT zu Nachteilen. Das für jedes Platinen-Design erforderliche benutzerdefinierte Fixture verursacht hohe, feste Engineering-Kosten, die nicht skalieren. Die Durchlaufzeiten strecken sich, während Fixtures entworfen, gebaut und debuggt werden. Designiterationen, die bei der Einführung neuer Produkte üblich sind, machen Fixtures vollständig obsolet und erzwingen den Neustart des Zyklus. Bei PCBA, wie wir bei Hunderten von Projekten beobachtet haben, rechnet sich Voll-ICT bei Läufen unter 200 bis 300 Einheiten kaum.

Die Alternative besteht nicht darin, rigoroses Testen aufzugeben, sondern das fixturesabhängige Modell durch eine schlankere, schnellere Strategie auf Basis von Boundary Scan, vettelosem Testen und fokussiertem Funktionstest zu ersetzen. Diese Kombination bietet vergleichbare Fehlerabdeckung, eliminiert den Flaschenhals des Fixtures und ermöglicht einen schnelleren Debug-Loop, wenn Fehler gefunden werden. Dieser Wandel ist kein ideologisches, sondern ein praktisches Reagieren auf die mathematische und mechanische Reibung, die ICT auf die Low-Volume-, agile Produktion ausübt.

Die ICT-Annahme und wo sie versagt

Das In-Circuit-Testing wurde in einer Ära hoher Volumina und stabiler Designs zum Industriestandard. Das Modell war einfach: Investitionen in ein maßgeschneidertes Test-Setup und einen hochentwickelten Prüfer, dann diese Investition bei zehntausenden von identischen Einheiten nutzen. Bei Testzeiten, die in Sekunden gemessen werden, waren die Grenzkosten pro Platine effektiv null, nachdem die Fixkosten gedeckt waren. Für einen Hersteller von Unterhaltungselektronik, der 50.000 Einheiten derselben SKU produziert, waren die Berechnungen unanfechtbar.

Dieses Produktionsmodell ist zerbrochen. Moderne Elektronikfertigung bedient zunehmend Märkte mit hohem Mix und niedriger Stückzahl. Produktlebenszyklen sind kürzer, Design-Iterationen häufiger, und die Anpassung ist ein Wettbewerbsvorteil. Ein Unternehmen könnte 150 Einheiten einer Variante produzieren, das Design iterieren und dann 200 der nächsten herstellen. Die Annahme, dass ein einzelnes Fixture Tausende von identischen Platinen testen kann, gilt nicht mehr. Die Fixkosten, die bei hohen Volumina vernachlässigbar waren, werden bei wenigen Hundert Einheiten zu einer Belastung.

Das Modell bricht, wenn die Gesamtkosten für ICT-Infrastruktur die risikoadjustierten Kosten alternativer Strategien übersteigen. Diese Schwelle ist kein Zufall. Sie hängt von den Fixture-Kosten, der Ingenieurzeit, der Produktionsdurchlaufzeit und der durch fixturelose Methoden erreichbaren Abdeckung ab. Für die meisten Platinen-Designs liegt diese Schwelle zwischen 200 und 300 Einheiten.

Die Fixkostenfalle des In-Circuit-Testings

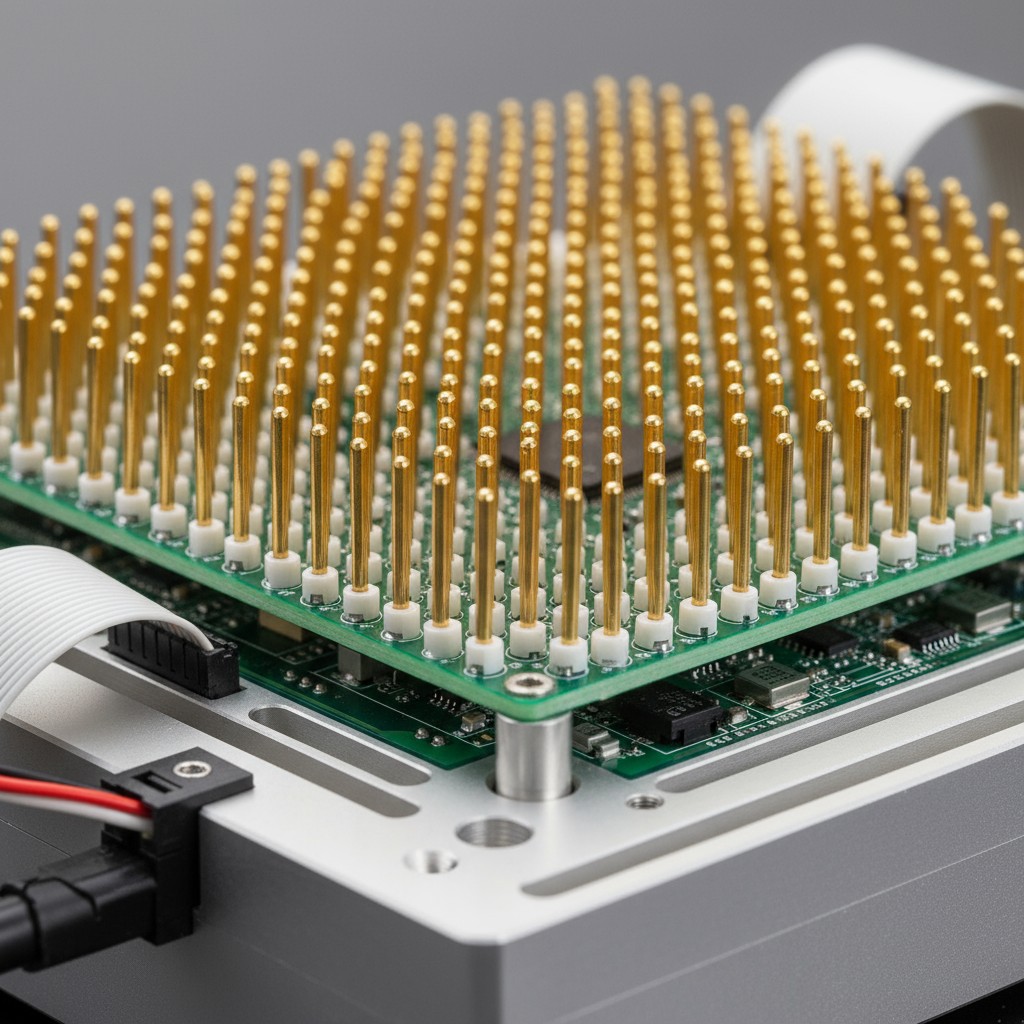

Während das Fixture die sichtbarste Kostenstelle des ICT ist, sind die tatsächlichen wirtschaftlichen Belastungen viel umfassender. Ein maßgeschneidertes ICT-Fixture ist kein Standard-Kauf; es ist ein ingenieurtechnisches Artefakt, speziell für das Layout der Platine gebaut. Der Designprozess erfordert die Übersetzung des Netlists und der Komponentenplatzierung der Platine in eine mechanische Struktur, die mit federbelasteten Testsonden versehen ist, die jeweils mit sub-millimetergenauer Präzision an einem bestimmten Testpunkt ausgerichtet sind. Das Fixture muss Toleranzen der Komponenten, Verformungen der Platine und Verschleiß der Sonden berücksichtigen. Es muss dann validiert und debuggt werden – ein Prozess, der oft unerwartete Probleme mit Sondenaccess oder Signalintegrität aufdeckt.

Fixture-Engineering-Kosten und Lieferzeiten

Die Engineeringkosten für eine mäßig komplexe Vorrichtung liegen typischerweise zwischen $8.000 und $15.000. Hochdichte Platinen mit fein-pitch Komponenten oder begrenztem Zugang zu Testpunkten können diese Zahl auf $25.000 oder mehr treiben. Dies sind rein die Kosten der maßgeschneiderten mechanischen und elektrischen Schnittstelle, die benötigt wird, um die Platine mit der ICT-Ausrüstung zu verbinden, getrennt von den Kapitalkosten des Testers selbst.

Die Vorlaufzeit ist ebenso bedeutend. Sobald ein Platinenentwurf endgültig ist, benötigen das Design und die Herstellung der Vorrichtung typischerweise zwei bis vier Wochen, bei komplexen Designs bis zu sechs Wochen. Während dieses Zeitraums steht die Produktion still. Platinen können montiert werden, aber sie können nicht getestet werden. Sie liegen auf Lager und warten. Wenn sich das Design während dieses Zeitfensters ändert — was bei Neuprodukten häufig vorkommt — muss die Vorrichtung überarbeitet oder verworfen werden. Die Uhr läuft neu ab.

Die Break-Even-Formel für Kleinserien

Die wirtschaftliche Falle wird deutlich, wenn die Kosten der Vorrichtung durch die Stückzahl geteilt werden. Eine $12.000 Vorrichtung für eine Serie von 100 Einheiten erhöht die Belastung pro Platine um $120. Für eine Platine mit einer Stückliste von $500 ist das ein Testüberkopf von 24 Prozent. Selbst wenn der ICT-Prozess schnell ist, ist die wirtschaftliche Effizienz schlecht. Dieselbe Vorrichtung, amortisiert über 500 Einheiten, senkt die Stückkosten auf $24, eine viel akzeptablere Belastung von fünf Prozent. Der Unterschied ist rein eine Volumenfrage.

Der Break-Even-Punkt ist dort, wo die Gesamtkosten des ICT — einschließlich Engineering, Einrichtung und Opportunitätskosten des Vorlaufs — die Kosten einer vorrichtungsfreien Alternative gleich sind. Für eine Strategie, die Boundary-Scan, vectorloses Testen und einen lean funktionalen Test kombiniert, sind die Infrastrukturkosten deutlich niedriger. Boundary Scan benötigt keine Vorrichtung, und vectorloses Testen verwendet wiederverwendbare Sensoren, die ohne mechanischen Kontakt funktionieren. Jede funktionale Testvorrichtung ist in der Regel minimal und generisch, kein platinen-spezifisches Artefakt, das Wochen an Engineering erfordert.

Bei Produktionsmengen unter 200 Einheiten bricht die Wirtschaftlichkeit des ICT zusammen. Unter 300 Einheiten ist die Rechtfertigung marginal, abhängig von der Komplexität der Platine. Erst bei über 300 Einheiten für stabile, nicht-iterative Designs beginnt ICT wieder wirtschaftlich sinnvoll zu werden.

Was Boundary Scan und Vectorless Testing wirklich sind

Die Alternative zu fixturebasiertem Testen ist kein Kompromiss bei der Strenge, sondern eine Umstellung auf Methoden, die bestehende Design-Infrastruktur und kontaktlose Messungen nutzen. Diese Werkzeuge wurden entwickelt, um denselben Trend anzugehen, der die ICT untergräbt: zunehmende Leiterplatten-Dichte und schrumpfender Zugang zu physischen Prüfpunkten.

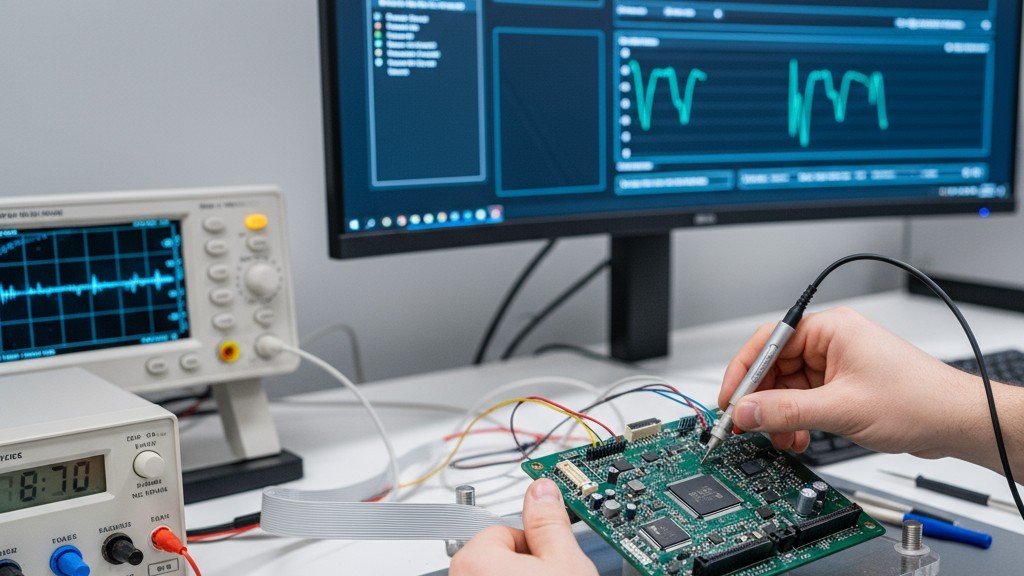

Boundary-Scan, formalisiert im IEEE 1149.1 Standard (allgemein bekannt als JTAG), integriert Testlogik direkt in die integrierten Schaltungen einer Platine. Konforme Chips enthalten eine Kette von Zellen an jedem Eingangs- und Ausgangspin. Während eines Tests verschiebt eine einfache Vier-Leitungs-Schnittstelle Muster in diese Zellen, steuert die Logikpegel auf den Netzen der Platine. Die resultierenden Zustände werden erfasst und ausgegeben, um sie zu analysieren, was dem Tester ermöglicht, Signale auf Pin-Ebene ohne physischen Kontakt zu steuern und zu beobachten. Diese non-invasive Methode ist äußerst effektiv bei der Erkennung von Kurzschlüssen, offenen Verbindungen und Verstopfungen zwischen konformen Geräten.

Vectorloses Testen ergänzt dies, indem es kapazitive und induktive Messungen verwendet, um Fehler über die gesamte Platine zu erkennen. Ein Sensorarray in der Nähe der Platine misst die elektromagnetische Signatur der montierten Komponenten und Leiterbahnen. Kurzschlüsse erzeugen messbaren kapazitiven Kupplung, offene Verbindungen zeigen charakteristische Impedanzänderungen. Die Methode ist schnell, berührungslos und kann das Vorhandensein, die Polarität und den ungefähren Wert von Komponenten ableiten, was sie effektiv macht, um grobe Herstellungsfehler wie fehlende Bauteile, umgekehrte Dioden oder Brückenleitungen zu erkennen.

Abdeckungsvergleich: Die Zahlen hinter dem Trade-Off

Der Hauptvorwurf gegen den Verzicht auf ICT ist die Abdeckung. Während ICT prinzipiell jeden Knoten auf einer Platine mit genügend Testpunkten erreichen kann, ist die Behauptung, dass Alternativen minderwertig sind, unvollständig. Die eigentliche Frage ist, ob sie ausreichende Abdeckung erreichen, um die tatsächlichen Fehler zu erkennen, und ob ein fokussierter funktionaler Test die verbleibende Lücke schließen kann.

Was Boundary Scan abdeckt

Grenzschichtüberwachung hängt davon ab, wie viele Komponenten auf der Platine den JTAG-Standard erfüllen. Bei Platinen, die von digitaler Logik dominiert werden—Mikroprozessoren, FPGAs, Speicher—ist die Abdeckung umfangreich. Die Testkette kann die Verbindung zwischen diesen Geräten auf Fehler testen, mit Fehlererkennungsraten von über 95 Prozent bei Kurzschlüssen, Unterbrechungen und Stuck-at-Fehlern. Eine Platine, auf der 80 Prozent der Komponenten den Standards entsprechen, erreicht etwa 70 bis 85 Prozent Nettoabdeckung. Analoge Abschnitte, diskrete Komponenten und Altteile sind für diese Methode unsichtbar. Für digital-intensive Designs bietet die Grenzschichtüberwachung allein eine Abdeckung, die mit ICT für die Verbindungsschicht vergleichbar ist, wo die meisten Montagefehler auftreten.

Was Vektorloses Testen hinzufügt

Vectorloses Testen füllt die Lücken, die durch Boundary-Scan verbleiben, insbesondere bei passiven Bauteilen und groben Montagefehlern. Kapazitive Messungen können fehlende Widerstände, falsche Kondensatorwerte und umgekehrte Dioden erkennen. Während sie weniger präzise sind als ICTs direkte Messungen, ist sie eine effektive Vorfilterschicht für die häufigsten Fehler: falsches Bauteil, fehlendes Bauteil oder schwere Fehljustierung. Dies erhöht die gesamt Fehlerabdeckung um weitere 10 bis 20 Prozent und bietet eine berührungsfreie Überprüfungsebene für Teile, die Boundary-Scan nicht erfassen kann.

Die verbleibende Lücke und wie der Lean-Funktions-Test sie schließt

Die Kombination aus Boundary-Scan und vectorlosem Testen lässt immer noch eine Lücke in der funktionalen Validierung und der analogen Leistung. Eine Komponente kann vorhanden und richtig verbunden sein, aber dennoch nicht innerhalb der Spezifikation funktionieren. Eine Stromversorgung könnte Spannung liefern, aber mit übermäßigem Ripple. Hier kommt ein leaner funktionaler Schaltungstest (FCT) ins Spiel. Im Gegensatz zu einem vollständigen ICT-Setup validiert ein leaner FCT, dass die Platine ihre beabsichtigte Funktion unter realistischen Bedingungen erfüllt. Es liefert Strom, stimuliert Eingänge und misst Ausgänge. Für einen Motorregler könnte es die PWM-Signalgenerierung überprüfen; für eine Kommunikationsplatine könnte es eine fehlerfreie Datenübertragung testen. Der funktionale Test ergänzt die strukturellen Tests und deckt Fehler auf, die die anderen Methoden nicht erkennen können.

Kombiniert erzielen diese drei Methoden typischerweise eine Fehlerabdeckung von 85 bis 95 Prozent. Das ist nicht 100 Prozent, aber auch ICT erreicht in der Praxis keine volle Abdeckung. Aufgrund von Testpunktbeschränkungen und Probeverschleiß liegt die tatsächliche ICT-Abdeckung oft unter ihrem theoretischen Maximum. Der Unterschied in der Abdeckung ist viel kleiner als die Nachteile bei Kosten und Vorlaufzeit.

Der Debug-Loop-Vorteil

Die Testabdeckung ist nur halb so wertvoll; das andere ist die Geschwindigkeit und Präzision der Fehlerisolierung. Ein Test, der einen Fehler erkennt, aber vage Diagnosen liefert, erhöht die Zeit und die Kosten, um die Wurzel des Problems zu finden.

Während ICT großartig darin ist, Fehler zu erkennen, können seine Diagnosen frustrierend vage sein. Ein Tester kann melden, dass Knoten 47 kurzgeschlossen an Masse ist, aber nicht erklären warum oder wo. Der Techniker muss das Schaltbild nachverfolgen, den Netzverlauf finden und den Bereich visuell inspizieren — ein Prozess, der Stunden auf einer dichten, mehrlagigen Platine in Anspruch nehmen kann.

Grenzflächen-Scan-Diagnosen sind grundlegend anders. Da die Scan-Kette in die Komponenten eingebettet ist, isoliert der Test Fehler auf bestimmte Pins und Bausteine. Ein Kurzschluss zwischen zwei Netzen wird durch die genauen Geräteanschlüsse identifiziert, was die Suche auf wenige Quadr millimeter eingrenzt. Unterbrechungen werden zwischen bestimmten Treiber- und Empfängerpaaren erkannt. Der diagnostische Ausgang ist kein Fehlercode. Es ist eine Karte. Diese Präzision bedeutet, dass ein Fehler, der mit ICT-Daten eine Stunde Debugging benötigt, oft in 10 bis 20 Minuten mit Boundary Scan behoben werden kann. Bei einer Produktion von 100 Einheiten mit einer typischen Fehlerquote kann die kumulative Debugging-Zeit um mehr als 10 Stunden gespart werden.

Durchlaufzeit und Flexibilität: Der versteckte Wert

Das wirtschaftliche Argument gegen ICT bei kleinen Stückzahlen ist überzeugend, aber die Vorlaufzeitstrafe ist ebenso erheblich. Der zweifache bis vierfache Wochenplan für die Vorrichtung, der den Einschnitt des Designs und die Testbereitschaft verzögert, ist unumgänglich. Für Neueinführungen, bei denen die Markteinführungszeit entscheidend ist, ist diese Verzögerung oft nicht akzeptabel.

Boundary Scan und vectorloses Testen eliminieren diese Wartezeit. Der Testaufbau kann in Stunden oder Tagen konfiguriert werden, nicht in Wochen, sodass Boards kontinuierlich vom Zusammenbau zum Testen und Versand gelangen können. Diese Flexibilität ist entscheidend bei iterativen Designs. Ein erster Prototypenlauf könnte Probleme aufzeigen, die Änderungen am Boardlayout erfordern. Mit ICT erfordert jede Revision einen neuen oder umgestalteten Vorrichtung, wodurch Kosten und Vorlaufzeit wieder entstehen. Boundary Scan-Testmuster, die aus der Netzliste generiert werden, aktualisieren sich automatisch mit dem Design. Dies schafft eine Teststrategie, die iterative Entwicklung unterstützt, anstatt sie zu bestrafen.

Wann man immer noch ICT wählt

Aber der Fall gegen Low-Volume-ICT ist nicht absolut. Bestimmte Designs und Produktionskontexte rechtfertigen die Investition weiterhin.

Boards mit hochdichten analogen oder RF-Abschnitten sind schlechte Kandidaten für eine reine Vorrichtungslose Strategie. Analoge Komponenten fehlen die Boundary-Scan-Logik, und kritische Leistungsmerkmale wie Verstärkung oder Phasenrauschen können strukturell nicht überprüft werden. Wenn analoge oder RF-Schaltungen mehr als 40 Prozent der Funktionalität des Boards ausmachen, stärkt sich die Argumentation für ICT erheblich.

Regulierte Branchen wie Medizin, Luft- und Raumfahrt sowie Automobilindustrie arbeiten oft unter Vorschriften, die bestimmte Testabdeckungen oder Methoden vorschreiben. Wenn ein reglementierter Standard In-Circuit-Testing oder gleichwertigen Knotenpunktzugang erfordert, können alternative Strategien nicht ausreichen. Hier sind die Kosten für ICT ein unverhandelbarer Marktzugangskostenpunkt.

Schließlich ändert ein klarer und engagierter Weg zur Produktion in großem Maßstab die Mathematik. Wenn eine anfängliche Produktion von 150 Einheiten voraussichtlich auf 1.000 Einheiten innerhalb von sechs Monaten skaliert, amortisiert sich die Vorrichtung auf das gesamte erwartete Volumen. Dies erfordert großes Vertrauen in die Prognose und ein stabiles Design, aber es kann die Anfangsinvestition rechtfertigen.

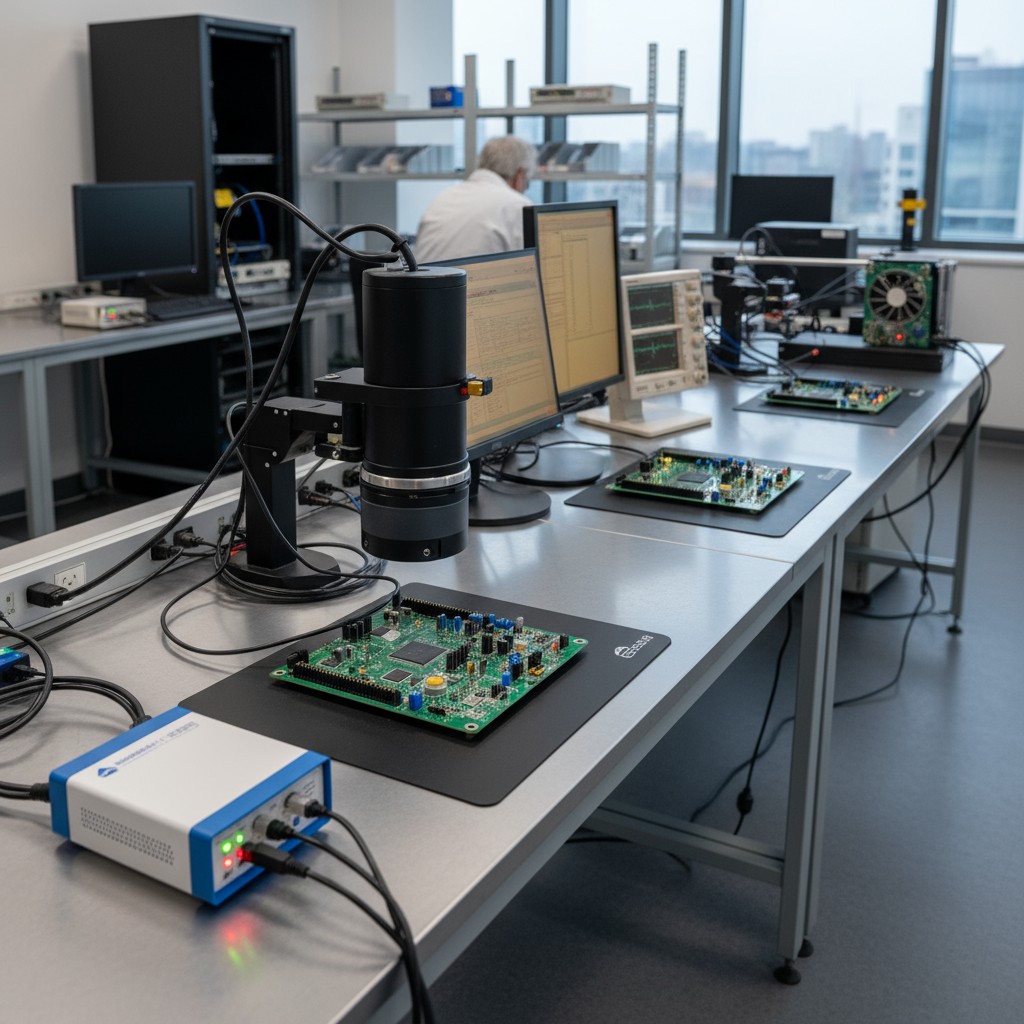

Aufbau der alternativen Teststrategie

Der Ersatz von ICT ist kein einfacher Austausch; es ist eine Neukonfiguration der Testarchitektur zu einer geschichteten Strategie, bei der jede Schicht Fehler erkennt, die die anderen möglicherweise übersehen.

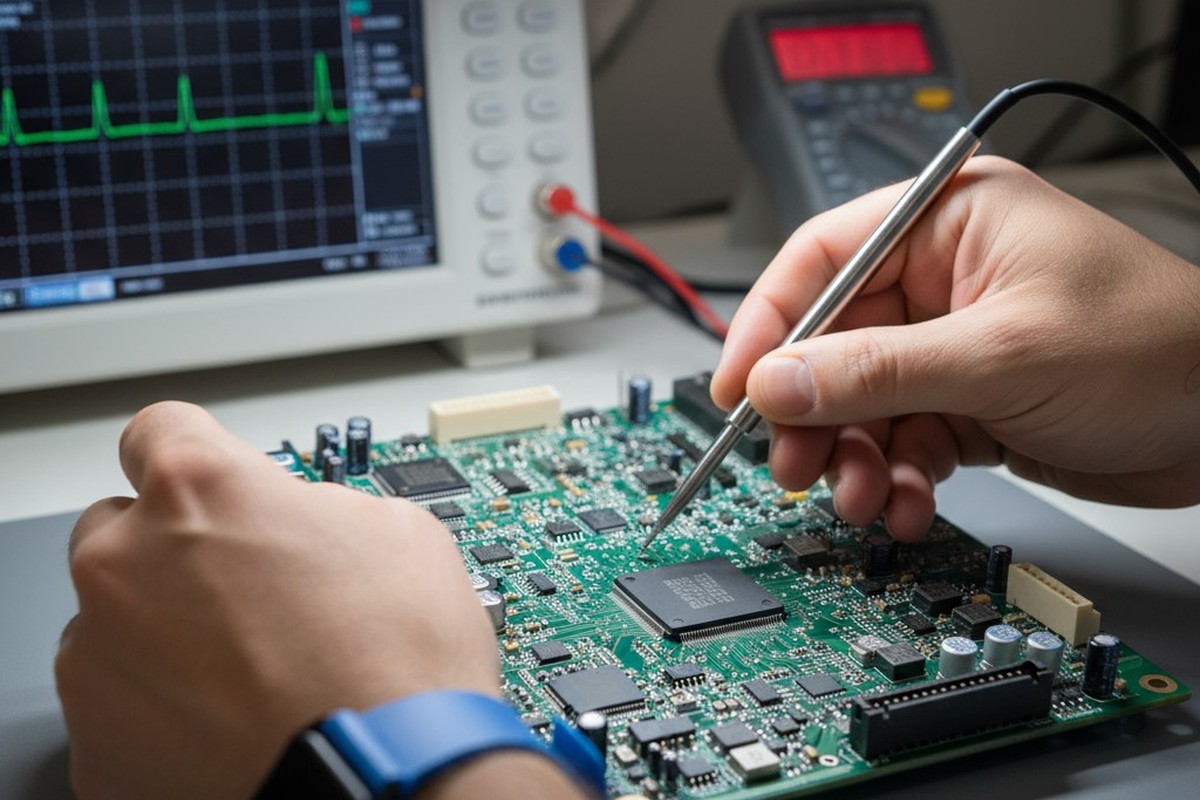

Der Prozess sollte sequenziell erfolgen. Die erste Schicht ist Boundary Scan, der auf allen konformen Geräten schnell läuft, um Interconnect-Fehler bei den digitalen Komponenten des Boards zu erkennen. Boards, die durchfallen, werden für eine sofortige Nacharbeit markiert, wodurch katastrophale Fehler beim späteren Einschalten vermieden werden. Die zweite Schicht ist das vectorlose Testen, das das gesamte Board durchläuft, um fehlende oder falsche passive Komponenten, grobe Kurzschlüsse und Polarisationsfehler zu erkennen. Es deckt die Komponenten und Netze ab, die für die Scan-Kette unsichtbar sind.

Die dritte und letzte Schicht ist ein fokussierter Funktionstest. Nachdem strukturelle Fehler bereits ausgefiltert wurden, wird das Board eingeschaltet, um seine kritischen Funktionen unter realistischen Betriebsbedingungen zu validieren. Der Umfang wird an den Zweck des Boards angepasst – die Genauigkeit des ADC auf einer Datenerfassungsplatine oder die Lastregelung bei einer Stromversorgung. Diese Abfolge stellt sicher, dass katastrophale Fehler frühzeitig erkannt und zerstörungsfrei behoben werden, wodurch die Debugging-Zeit bei komplexeren funktionalen Fehlern minimiert wird.

Für Boards mit hybrider Komplexität – beispielsweise ein dichter digitaler Kern umgeben von analoger Signalkonditionierung – kann eine hybride Strategie am besten sein. Eine teilweise ICT-Vorrichtung kann so gestaltet werden, dass nur der kritische analoge Abschnitt geprüft wird, während der digitale Teil der Boundary Scan überlassen bleibt. Die Wirtschaftlichkeit einer Teilvorrichtung ist günstiger, reduziert Kosten und Vorlaufzeit, ohne die notwendige Abdeckung für das gesamte Design zu vernachlässigen.