Wenn eine Design-Datei in die technische Warteschlange kommt, schauen wir uns zuerst nicht die Routing- oder Bauteilplatzierung an. Wir betrachten die Paste-Masken-Schicht.

Die meisten Designer behandeln diese Schicht als direkte Übersetzung der Kupferpads: Wenn auf der Platine ein Pad vorhanden ist, sollte auch eine Apertur in der Schablone derselben Größe vorhanden sein. Diese 1:1-Logik ist ordentlich, aufgeräumt und mathematisch perfekt in einer CAD-Umgebung. Es ist auch die häufigste Ursache für Montagefehler bei modernen Mixed-Technology-Boards.

Das Problem? Eine Gerber-Datei ist eine zweidimensionale Karte, aber eine Lötstelle ist ein dreidimensionales Volumen. Sobald wir vom Bildschirm in die Fertigungsebene wechseln, beschäftigen wir uns mit Fluiddynamik, Oberflächenspannung und den physikalischen Grenzen, Metallpaste durch ein Stahlblech zu drücken.

Wenn wir blind eine Schablone basierend auf der Standardausgabe „100% Coverage“ Ihrer ECAD-Software schneiden, garantieren wir Scheitern. Bei einer Platine mit sowohl schweren Anschlüssen als auch feinen Pin-Abständen sorgt ein einheitlicher Ansatz dafür, dass die Hälfte der Platine zu viel Paste hat, während die andere Hälfte vernachlässigt wird. Wir modifizieren Ihre Schablonendaten nicht, um sie schwierig zu machen; wir tun es, weil die Physik es verlangt.

Löten ist ein Volumenproblem

Vergessen Sie „Coverage“. Wir müssen in Kubikmillicals denken.

Die mechanische Integrität einer Lötstelle – insbesondere bei Leistungsbauteilen und Anschlüssen – hängt vollständig vom Volumen des resultierenden metallischen Fillets ab. Ein standardmäßiges Oberflächenmontagepad sieht bei einer 5mil dicken Pasteauflage eventuell gut aus, aber ein Durchkontakt-Reflow-Kopf oder ein USB-C-Anschluss sind eine andere Dimension.

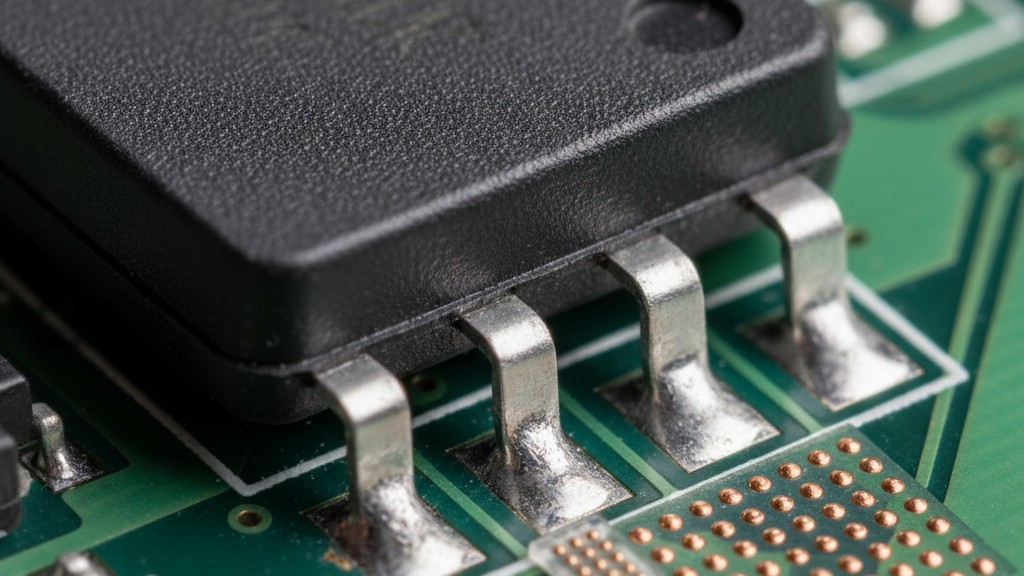

Designer geraten oft in Panik, wenn ein Anschluss während des Prototyp-Tests abbricht, in der Annahme, das Bauteil selbst sei defekt oder das Gehäuse zu schwach. In Wirklichkeit liegt das Problem fast immer an der Schablondicke. Ein USB-C-Anschluss hat strukturelle Beine, die tief in den Barrel der PCB verankert werden müssen. Wenn wir eine standardmäßige 4mil- oder 5mil-Folie (typisch für die meisten Signalkarten) verwenden, liefern wir nur einen Bruchteil des benötigten Lotes, um diesen Barrel zu füllen. Die Paste wird auf der Oberfläche aufgetragen, reflowt und verschwindet in der Bohrung, hinterlässt einen schwachen, ausgehungerten Meniskus, der beim ersten Einstecken bricht.

Um das zu beheben, müssen wir das Gesamtvolumen des Lochs minus Pin berechnen, einen 10%-Puffer für Flussmittel-Verbrennung hinzufügen und die Schablonenöffnung reverse-engineeren, um genau so viel Paste zu liefern. Oft ist das Pad auf der Platine nicht groß genug, um diese Menge nasse Paste zu halten. Das zwingt uns, Überdruck zu verwenden – absichtlich Paste auf die Lötstoppmaske zu drucken, damit sie während des Reflows auf das Pad zurückgezogen wird.

Der Flächenverhältnis-Boden

Während große Teile verhungern, haben kleine Teile das GegenteilProblem: Sie lassen nicht los. Hier wird die „Area Ratio“-Regel zur harten Grenze der Herstellbarkeit.

Siebdruck ist ein Kampf zwischen zwei Kräften: die Oberflächenspannung des auf die PCB-Pads haftenden Pastes und die Reibung des Pasts an den Innenwänden der Schablonentülle. Damit die Paste erfolgreich freigesetzt wird, muss die Fläche des Pads deutlich größer sein als die Fläche der Tüllenwände.

Der Branchenstandard (IPC-7525) setzt die Gefahrenzone auf ein Verhältnis von 0,66. Wenn das Verhältnis darunter fällt (zum Beispiel bei einem BGA mit 0,4mm Pitch oder einem 01005-Kondensator), verstopft die Paste die Schablone im Inneren, anstatt auf die Leiterplatte zu gelangen. Sie erhalten vielleicht einen guten Druck, vielleicht zwei, und dann verstopfen die Tüllen. Die automatische optische Inspektionsmaschine (AOI) wird sofort "unzureichender Lötmittel" melden.

Wir können versuchen, dies mit Nano-Beschichtungen zu überlisten, die den Stahl hydrophob machen und die Wände der Tülle effectively schmieren, aber das ist nur eine temporäre Lösung. Diese Beschichtungen nutzen sich nach 10.000 Zyklen oder intensiver Unterreinigung ab. Die einzige dauerhafte technische Lösung ist die Änderung der Geometrie: Wir machen die Tülle entweder größer (Risiko von Brückenbildung) oder dicker, um die Wandoberfläche zu verringern.

Der Konflikt zwischen großen und kleinen Teilen

Jetzt kommen wir zum zentralen Konflikt in der modernen Elektronikmontage: das ‚Großes Teil / Kleines Teil‘-Problem. Vielleicht haben Sie einen schweren D2PAK-Spannungsregler, der eine Berg von Lötmittel zur Wärmeabfuhr benötigt, direkt neben einem Wafer-level-Paket mit 0,35 mm Pitch, das nur eine mikroskopische Staubschicht an Paste braucht, um Kurzschlüsse zu vermeiden.

Wenn wir eine ‚Standard‘ 5mil-Schablone verwenden – die Standardwahl bei 90%-Anfragen, die wir sehen – gefährden wir eine dieser Komponenten. Die 5mil-Folie bietet genug Volumen für den D2PAK, ist jedoch zu dick für den winzigen Wafer-Chip; das Seitenverhältnis ist falsch und die Paste wird nicht freigesetzt. Wenn wir auf eine 3mil-Folie umstellen, um den kleinen Chip unterzubringen, wird der D2PAK vernachlässigt, was zu Lufteinschlüssen und thermischen Ausfällen führt.

Designer fragen oft: „Warum können Sie die Tüllenöffnung nicht einfach für das kleine Teil verkleinern?“ Wir können, aber denken Sie an das Flächenverhältnis: Die Verringerung der Tüllenöffnung bei gleichbleibender Dicke macht das Verhältnis nur schlechter. Sie können kein Z-Achsen-Problem mit X-Y-Achsen-Änderungen lösen.

Topografie der Technik: Der Stufen-Schablone

Wir müssen die Schablone weniger wie ein flaches Blatt und mehr wie eine topografische Karte behandeln.

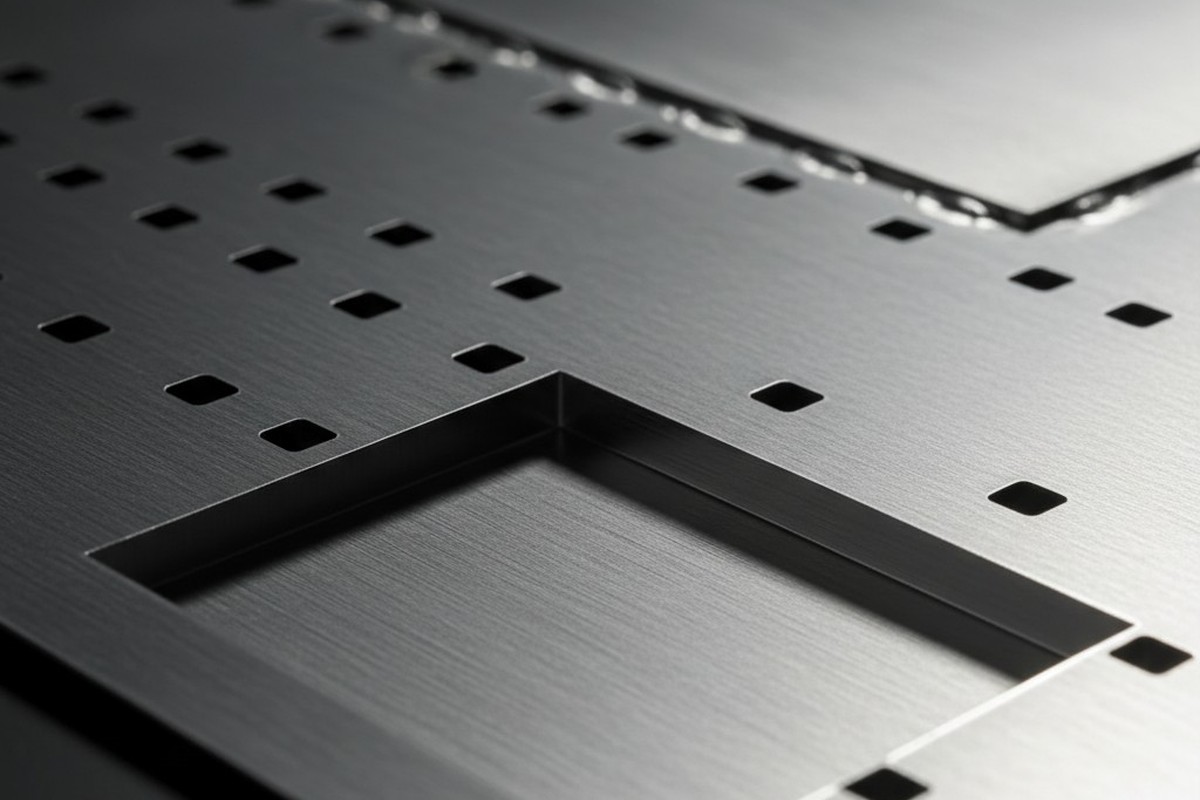

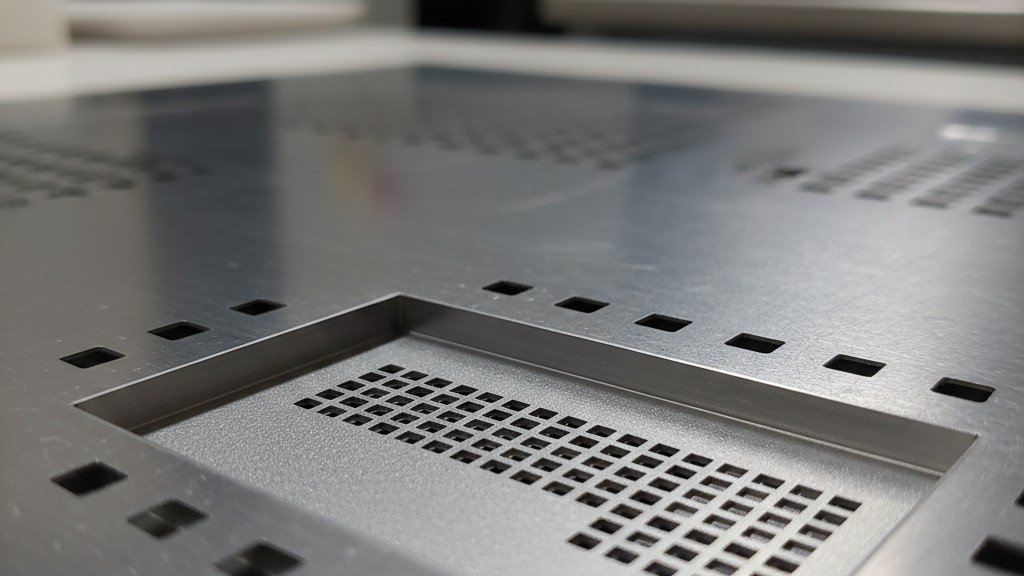

Wir verwenden Stufen-Schablonen, um lokale Dickenbereiche zu erstellen. Für dieses D2PAK oder USB-Anschluss könnten wir die Schablone ‚anheben‘, indem wir einen dickeren Stahlabschnitt (sagen wir 6mil oder 8mil) in diesen Bereich einbauen. Für den feinpitch BGA fräsen wir eine ‚absenkende‘ Tasche, die die Dicke auf 3,5mil oder 3mil für den Fußabdruck des Bauteils reduziert.

Das ist keine Magie; es erfordert eine sorgfältige Layoutplanung. Die Rakel ist flexibel, aber kein Fluid. Sie braucht Übergangsraum – typischerweise 50 bis 100 mil – um die Stufe hoch- oder runterzufahren, ohne zu skippen oder Paste aus den Löchern zu holen. Wir müssen diese Sperrzone sorgfältig vermessen, um sicherzustellen, dass keine kritischen Komponenten auf der Steigung der Stufe sitzen. Wird es richtig gemacht, ermöglicht es uns, große Pastevolumen für Leistungsbauteile und empfindliche, hochauflösende Absetzbereiche für Mikroteile in einem Durchlauf zu drucken. Es verwandelt eine „nicht baubare“ Leiterplatte in eine mit einer Ausbeute von 99%.

Fensterflächen und Outgassing

Geometrieänderungen beschränken sich nicht nur auf die Dicke. Wir müssen auch das Verhalten des Flusses selbst bekämpfen.

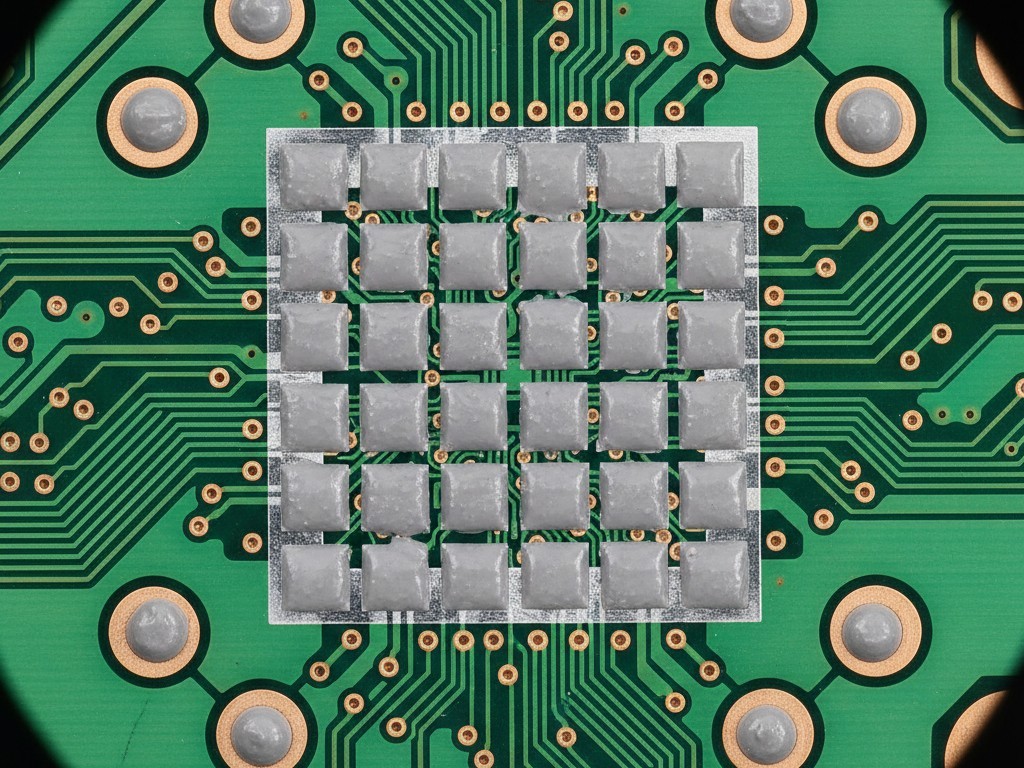

Unter großen thermischen Pads, wie bei QFNs oder Leistungstransistoren, zeichnen Designer in der Regel eine feste Masse aus Paste-Maske, die dem Kupferpad entspricht. Wenn wir das drucken, fangen wir während des Reflow einen großen Pool an flüchtigen Stoffen (Flux-Transportmittel) unter dem Chip ein. Während der Fluss kocht, hat das Gas keinen Ausweg und bildet enorme Hohlräume – Luftbläschen im Lötverbindung, die den Wärmeübergang blockieren.

Um dies zu verhindern, ignorieren wir den festen Block im Gerber und wenden eine "Fensterpaneel"-Reduktion an. Wir zerlegen die große quadratische Apertur in ein Gitter kleinerer Quadrate, getrennt durch 10-15 Mil breite Stahlkanäle. Diese Kanäle dienen als Autobahnen, damit das ausgasende Flussmittel entweichen kann. Das klingt für Leistungselektriker, die maximale Wärmeübertragung wollen, kontraintuitiv, aber beim Drucken weniger Tastungeln (oft mit 60-70% Abdeckung anstelle von 100%) führt tatsächlich zu mehr Metall-auf-Metall-Kontakt, weil es den Hohlraum eliminiert.

Die Wirtschaftlichkeit der Modifikation

Oft gibt es Widerstand gegenüber den Kosten. Eine standardmäßige Laser-Schablone könnte $150 bis $200 kosten. Eine mehrstufige Schalenschablone mit Nano-Beschichtung könnte zwischen $350 und $450 kosten. Einkaufsteams schauen sich diese Position an und fragen, ob wir es mit der Standardoption einfach "zum Funktionieren bringen" können.

Vergleichen Sie das mit den Kosten der Alternative.

Das Nacharbeiten eines überbrückten 0,4mm BGA ist nicht nur schwierig; oft ist es unmöglich, ohne die Platine oder benachbarte Komponenten zu beschädigen. Das Austauschen eines abgeknickten Steckers an einer fertigen Einheit kostet das Fünfzigfache des Preises des Rohteils. Die NRE-Kosten (Nicht-Wiederholende Entwicklungskosten) einer ordnungsgemäßen Schablone sind eine einmalige Gebühr. Die Kosten, Lot von tausend Platinen abzuschaben, weil wir versucht haben, die Physik zu trotzen, sind wiederkehrend, schmerzhaft und vollständig verhinderbar. Wir modifizieren die Daten, weil die Kosten, beim ersten Mal richtig zu liegen, immer niedriger sind als die Kosten, es später zu beheben.