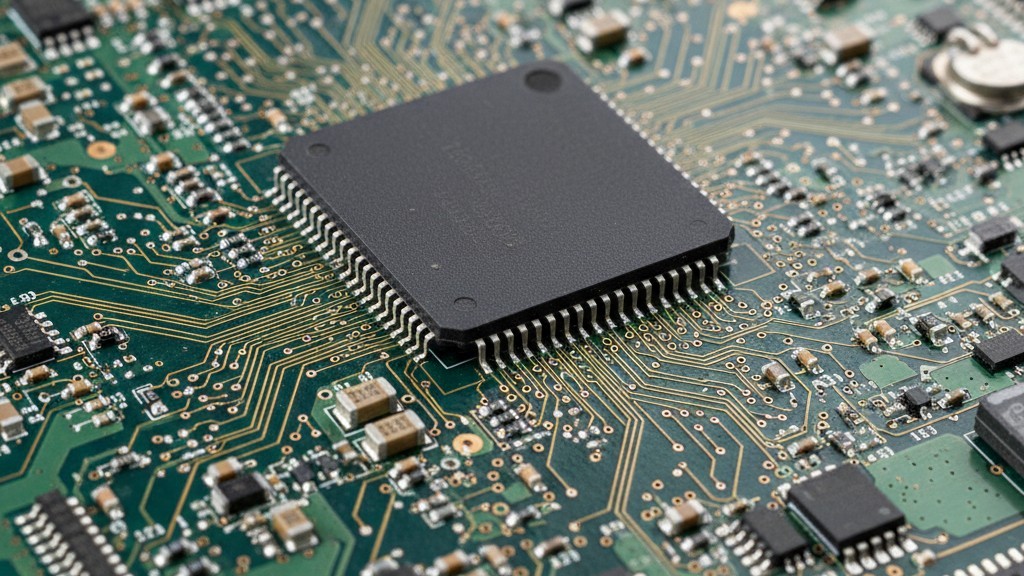

Die Stille eines toten Prototyps ist schwer. Es ist nicht nur das Fehlen von Lüftergeräuschen oder die dunklen LEDs auf der Debug-Schnittstelle. Es ist die sofortige, sinkende Kostenschätzung. Wenn eine Prototyp-Platine beim Starten nicht initialisiert, vielleicht ein BGA beim Zusammenbau nicht richtig Sitz hat oder ein Designfehler einen Austausch erfordert, verengt sich der Fokus sofort auf das große, schwarze Quadrat in der Mitte des PCB.

In Hochzuverlässigkeitsbereichen ist dieses Quadrat oft ein hochwertiger FPGA, wie ein Xilinx Kintex UltraScale oder ein Intel Stratix 10. Diese sind keine Handelskomponenten; sie sind Vermögenswerte. In Zeiten der Lieferkettenbeschränkung kann der Austausch dieses einzelnen Chips eine Vorlaufzeit von 52 Wochen oder eine Markup auf dem Maklermarkt bedeuten, die das Projektbudget sprengt. Die Platine selbst, ein 12-lagiger Stapel mit Blind- und Durchkontaktierungen, könnte in Fertigung und Montage $,000 kosten. Nacharbeiten sind kein Standardreparaturvorgang. Es ist eine Bergungsoperation, bei der der gesamte Entwicklungszeitraum aufs Spiel gesetzt wird.

Physik Verhandelt Nicht

Ein gefährliches Missverständnis besteht darin, dass das Entfernen eines Ball Grid Array (BGA) einfach damit verbunden ist, Hitze aufzubringen, bis der Lötzinn schmilzt. Diese Einstellung zerstört Prototypen. Handgehaltene Heißluftgebläse, die zwar hervorragend für das Schrumpfen von Schläuchen geeignet sind, sind Zerstörungsinstrumente für hochdichte Kopplungen.

Die Physik hängt von thermischer Masse und demCoefficient of Thermal Expansion (CTE) ab. Ein moderner FPGA sitzt auf einer Platine, die mit Kupfermaschenflächen gefüllt ist, die speziell zur Wärmeableitung entwickelt wurden. Wenn du die Oberseite des Chips mit heißer Luft kratzt, ohne die Unterseite des Boards ausreichend zu erhitzen, erzeugst du einen vertikalen thermischen Gradient. Die Oberseite dehnt sich aus, während die Unterseite kühl und starr bleibt. Das Ergebnis ist Verformung. Während sich das Board biegt, zieht es an den Lötstellen. Wenn die Wärmequelle unkontrolliert ist, besteht die Gefahr des „Pad-Cratering“ – buchstäblich das Herausreißen der Kupferpads aus dem Fiberglaslaminat. Sobald ein Pad aus einer internen Spur gerissen ist, ist das Board Schrott. Kein Drahtbrücke kann zuverlässig ein Hochgeschwindigkeits-Differentialpaar mit 10 Gbps reparieren.

Deshalb müssen Ingenieure eine „lokale Fertigung“-Mentalität annehmen. Das Ziel ist, das ursprüngliche Reflow-Profil – die spezifische Temperaturkurve über die Zeit – nachzubilden, die das Board im Fertigungsofen gesehen hat. Das gesamte Bauteil muss auf eine Durchlauf-Temperatur (normalerweise etwa 150°C bis 170°C) gebracht werden, um das Flussmittel zu aktivieren und die Temperatur über das PCB zu gleichen. Erst dann sollte man lokale Energie auf das Bauteil selbst anwenden, um es über den Liquiduspunkt von 217°C zu bringen. Physik ignoriert Fristen; wenn die thermische Steigung zu steil ist, dehnt sich die im Chipsatz eingeschlossene Feuchtigkeit in Dampf aus, was dazu führt, dass das Gehäuse delaminiert oder „Popcorn“ bildet. Ein explodierter Chip ist ein toter Chip.

Der Prozess: Kontrollierte Intervention

Das Retten einer $,000-Komponente erfordert Sorgfalt. Der Prozess beginnt Tage vor der eigentlichen Nacharbeit mit Feuchtigkeitsmanagement. Sollte die Platine nicht in einer trockenen Box mit Feuchtigkeitsindikatoren, die sichere Werte anzeigen, aufbewahrt worden sein, muss sie gebacken werden. Standard-IPC-1601-Protokolle verlangen, die Feuchtigkeit aus der PCB und den Komponenten zu backen, um das Dampfdruck-Abblättern zu vermeiden. Das Überspringen dieses Schrittes ist die häufigste Ursache für unsichtbare Fehler, die Wochen später auftreten.

Sobald die Platine trocken ist, wird sie in ein spezielles Nacharbeits-System überführt – typischerweise eine Maschine mit Split-vision-Optik, Infrarot-Vorheizern auf der Unterseite und einer computersteuerbaren Oberkonvektionsdüse. Automatisierung steuert diesen Prozess, nicht manuelles Gefühl. Ein Thermosensor ist oft an eine opferbereite Platine angebracht, um das thermische Profil genau abzubilden. Wir müssen wissen, dass wenn die Maschine 230°C anzeigt, die Lötperlen unterhalb des Zentrums dieses 35x35mm Gitters tatsächlich das Reflow-Temperaturfenster erreichen und nicht kalt bleiben, weil sie von einem Wärmeleiter in der Nähe beeinflusst werden.

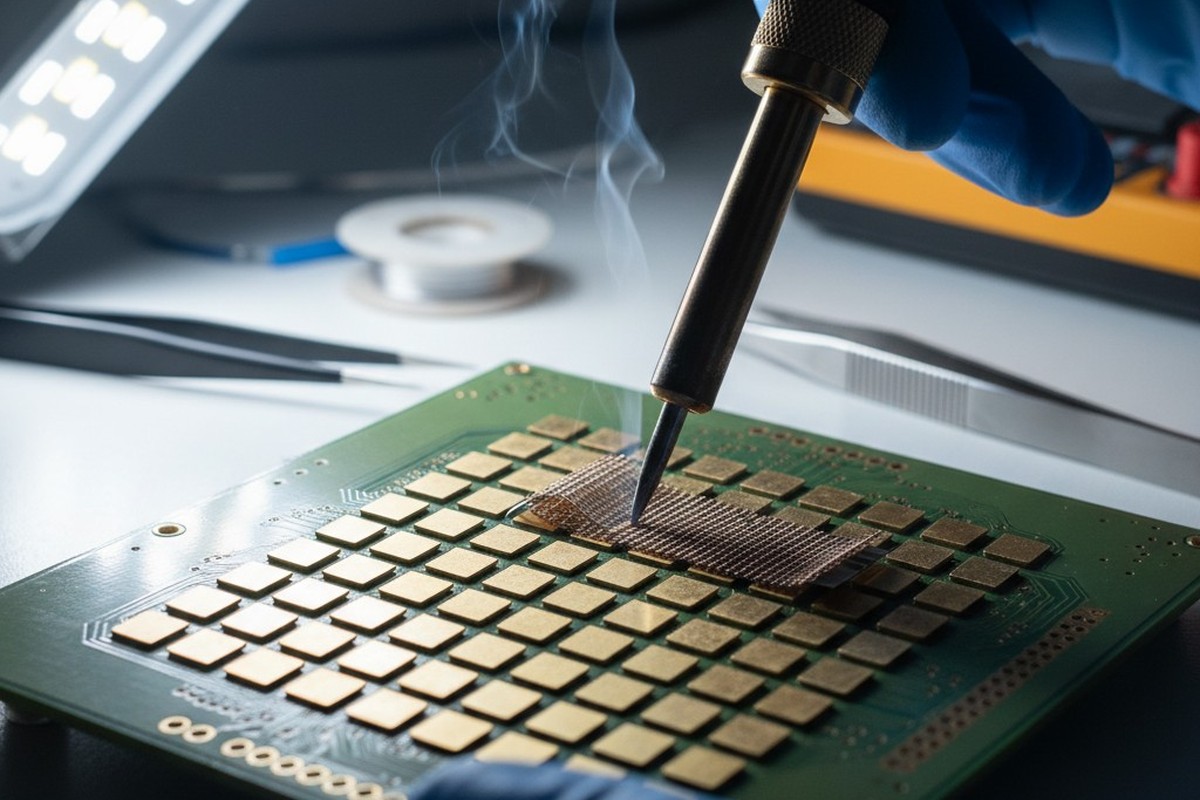

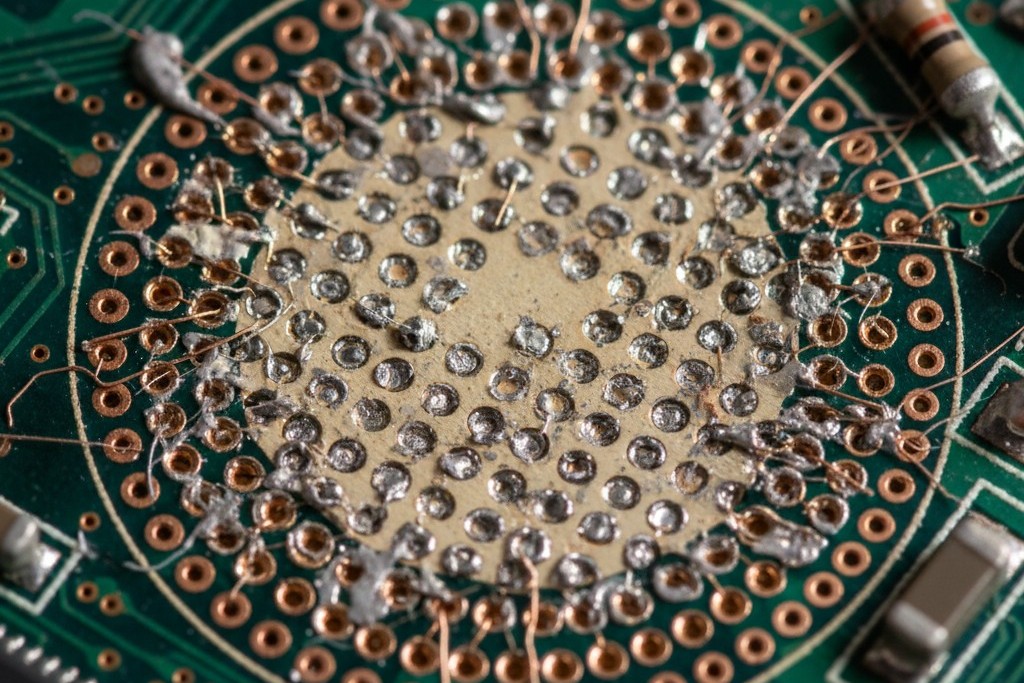

Das Entfernen an sich ist wenig dramatisch, wenn das Profil stimmt. Die Vakuumdüse senkt sich, das Lötzinn verflüssigt sich, und das Bauteil hebt sich vertikal ohne Kraftaufwand. Die Anspannung steigt sofort danach: das Site-Dressing. Dabei werden alte Lötstellen manuell mit einem Lötkolben und einem Wellenflussbands entfernt. Hier zählt vor allem die Erfahrung des Technikers. Die Lötspitze muss „schweben“ über den Pads; jeder Druck nach unten läuft Gefahr, ein Pad zu heben, was in der Regel tödlich für die Platine ist. Es gibt Epoxid-Reparaturmethoden für gelöste Pads, aber die Impedanzfehlanpassung, die durch eine Reparatur eingeführt wird, ist oft für Hochfrequenz-FPGA-Leitungen unakzeptabel. Die Pads müssen vor einem neuen oder erneut gelöteten Chip sauber, eben und kupferhell sein.

Die Reballing-Gleichung

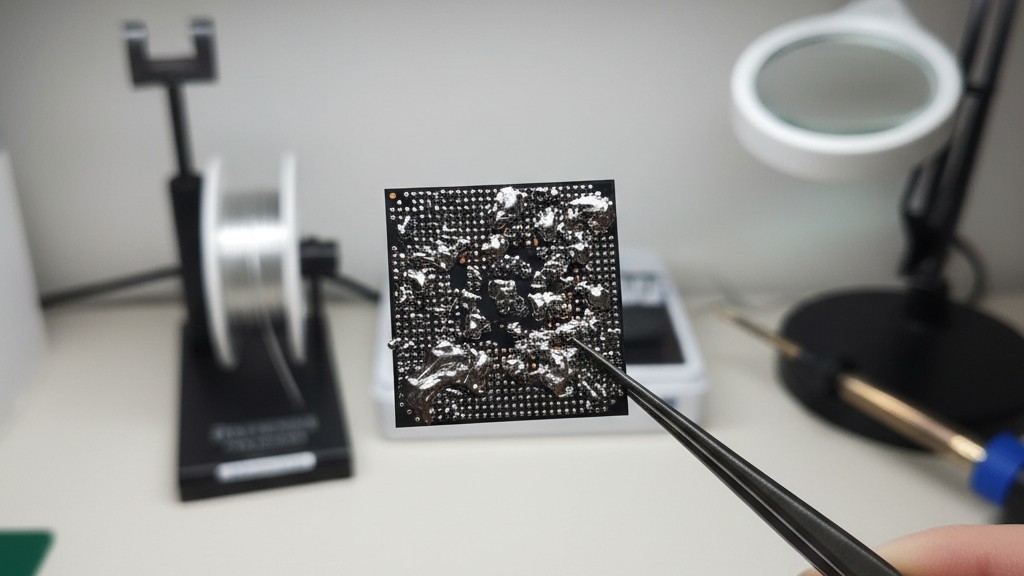

Manchmal ist das Ziel nicht ein neuer Chip, sondern das Retten des alten Chips von einer defekten Leiterplatte, um ihn anderswo zu verwenden, oder das erneute Einsetzen eines Chips, der einen Verbindungsfehler hatte. Dies führt zur Sub-Disziplin des Reballings. Ein entferner BGA hat unordentliche, unregelmäßige Lötbumpen auf der Unterseite. Diese müssen abgekratzt und neue Lötkugeln angebracht werden.

Es ist eine reine ROI-Berechnung. Reballing eines $5-Standardmikrocontrollers ist finanzieller Unsinn; die Arbeitsstunden übersteigen die Komponenten kosten. Aber für einen Virtex UltraScale+ im Wert von $15.000 ist Reballing obligatorisch. Der Prozess umfasst eine spezielle Schablone, die den Chipabdruck passt, einen klebrigen Flussmittel und Tausende vorgeformte Lötkugeln (oft 0,4 mm oder 0,5 mm Durchmesser), die manuell gegossen und ausgerichtet werden.

Uncertainty ist jedoch unvermeidbar. Jedes Mal, wenn ein Silizium-Wafer einen Reflow-Zyklus durchläuft – auf 240°C erhitzt und abgekühlt – sammelt sich thermischer Stress an. Die Unterschiede im thermischen Ausdehnen zwischen dem Silizium-Wafer, dem Gehäuse-Substrat und der Leiterplatte üben Kraft auf die internen Verbindungen aus. Während ein Chip in der Regel zwei oder drei Reflow-Zyklen aushält (erste Montage, Entfernung, Reballing, Platzierung), ist die Ausbeute nie garantiert. Wir können das Risiko durch perfektes Profiling mindern, aber wir können die Ermüdungsgrenze der Materialien nicht verändern.

Die Entscheidung zur Nachbearbeitung hängt meist vom Verhältnis „Austausch vs. Wiederherstellung“ ab. Wenn das Silizium aufgrund von Engpässen unersetzlich ist oder wenn die Leiterplatte Wochen an einzigartiger Fertigungszeit repräsentiert, ist der Aufwand für ein richtiges thermisches Profil und geschultes Bedienpersonal im Vergleich zu den Kosten für einen Neuanfang vernachlässigbar. Die Geräte – die Vorheizer, die Bildverarbeitungssysteme, die mit Stickstoff inertisierten Reflowköpfe – sind vorhanden, um eine Katastrophe in eine standardmäßige Ingenieur-Verzögerung zu verwandeln.