Blog

-

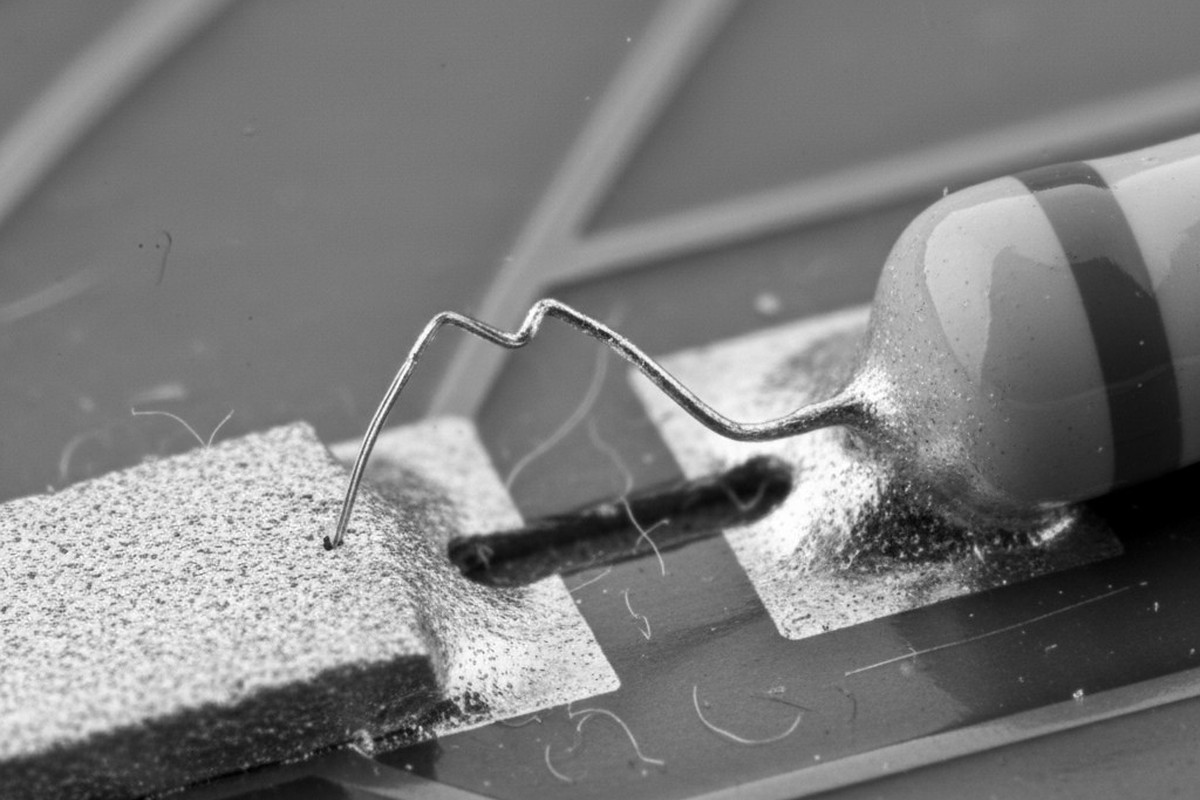

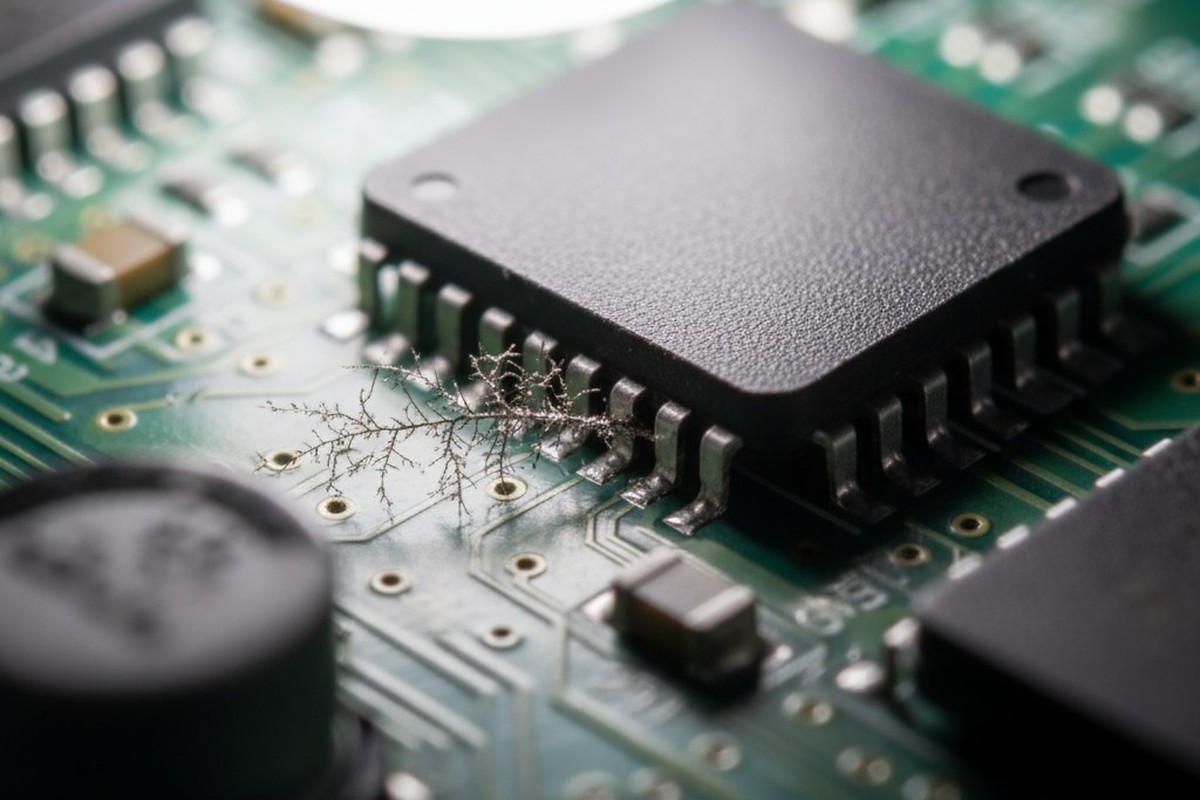

Der stille Kurzschluss: Warum Lotfäden in Niedrigleistungs-Elektronik gedeihen

Tin whiskers are a significant threat to long-life, low-power electronics, causing silent short circuits even in stable, room-temperature environments. This insidious failure mode is driven by compressive stress in tin plating, but can be effectively mitigated by choosing the right surface finish, specifically a system of matte tin over a nickel underplate with a post-plating…

-

Der HiP-Defekt auf Hoch-thermischer Leiterplatten: Warum mehr Paste nie die Lösung ist

When faced with head-in-pillow (HiP) defects on high thermal mass boards, the instinct is to add more solder paste, but this approach fails to address the root cause. The true problem is dynamic board warpage driven by thermal gradients, which can only be solved by mastering the reflow profile, ensuring proper mechanical support, and selecting…

-

Der penny-wise, pound-foolish Fall gegen OSP

OSP may seem like a cost-effective PCB surface finish, but its short shelf life and vulnerability to heat create significant risks for New Product Introductions. This hidden liability often leads to solderability failures and expensive rework, turning initial savings into major project delays and costs that could be avoided with a more robust finish like…

-

Der 48-Stunden-Loop: Wie die schnelle Fehleranalyse der PCBA von Bester die Margenverluste stoppt

Traditionelle PCBA-Fehlanalyse ist zu langsam, wodurch kleinere Fehler zu erheblichen finanziellen Belastungen werden, wenn mehr fehlerhafte Einheiten hergestellt und versendet werden. Der 48-Stunden-Schnell-Fehleranalysezyklus von Bester bricht diesen Kreislauf und liefert eindeutige Ursachenanalysen sowie umsetzbares Feedback, um Probleme daran zu hindern, sich zu verschlimmern, und um Gewinnmargen zu schützen, bevor sie schrumpfen.

-

Das Unsichtbare Engpass: Warum Ihre Firmware-Lade-Strategie die SMT-Produktivität einschränkt

Online-Firmware-Programmierung ist ein stiller Killer für die SMT-Produktivität, da sie die gesamte Produktionslinie in Geiselhaft nimmt. Durch die Entkopplung des Programmierens vom Bau und die Verwendung paralleler Methoden wie Offline-Gang-Programmierung oder dedizierte Hochgeschwindigkeits-Flashstationen können Sie diesen kritischen Engpass beseitigen und Ihre Linie mit höchster Geschwindigkeit laufen lassen.

-

Das Reinigkeitsmaß, das wirklich zählt: Warum Ihr ROSE-Test Ihnen etwas vormacht

Der standardmäßige ROSE-Test auf PCB-Reinheit vermittelt ein falsches Sicherheitsgefühl und führt zu kostspieligen Feldausfällen durch Korrosion und Kurzschlüsse. Seine Durchschnittsmethode verschleiert gefährliche lokale Kontaminationen unter Komponenten, ein Problem, das durch die Verwendung von Ionenchromatographie für eine detaillierte chemische Analyse zur echten Vorhersage der Langzeitzuverlässigkeit gelöst wird.